卷积神经网络的软硬件协同加速技术

2021-08-23李欣瑶刘飞阳文鹏程李鹏

李欣瑶 刘飞阳 文鹏程 李鹏

摘 要: 面向构建智能化航空电子系统的需求,提升有人机/无人机智能化作战水平,设计并实现卷积神经网络CNN的软硬件协同加速技术,以解决目标识别、辅助决策、自主规划等复杂问题。针对算法模型的庞大参数量与嵌入式环境有限存储资源的冲突问题,采用模型结构优化及量化算法压缩网络规模。针对复杂浮点运算与计算资源紧缺的冲突问题,基于Verilog HDL设计卷积、池化两种加速算子,采用流水线+全并行方式,以达到计算加速的目的。通过软件优化设计与硬件加速运算的协同作用,实现卷积神经网络的推理过程加速。以YOLOv3及YOLOv3-Tiny两種典型CNN为例进行加速,并在Xilinx ZCU102 FPGA评估板上进行验证。结果表明,加速后的模型与原模型对比,参数量可压缩3/4左右,YOLOv3的推理速度提升近65倍,YOLOv3-Tiny提升23倍左右。

关键词:智能计算;硬件加速;目标检测;模型压缩;FPGA

中图分类号:TJ760; TP18 文献标识码: A 文章编号:1673-5048(2021)03-0099-06

0 引 言

随着人工智能算法模型结构的快速更迭,神经网络正逐步被应用于解决智慧医疗、自动驾驶等多种复杂智能问题。在航空领域,有人机与无人机的空战过程均朝着智能化的方向发展[1],目标识别跟踪、辅助决策、自主规划等复杂任务均可依赖神经网络完成。但机载嵌入式环境对功耗、实时性都有着严格的制约,且存储、计算资源都较为紧缺,如何将神经网络模型部署于资源受限的嵌入式环境成为亟待解决的问题。

本文面向智能化航空电子系统的需求,设计并实现一种面向卷积神经网络(Convolutional Neural Network,CNN)的软硬件协同加速方法。针对庞大网络模型参数量与有限存储资源的冲突问题,以及大量复杂浮点运算与计算资源紧缺的冲突问题,从软硬件两方面对网络模型进行了优化与加速,解决了基于CAFFE(Convolutional Architecture for Fast Feature Embedding)框架的网络结构优化问题、模型参数量化问题以及神经网络加速算子的构建问题,以YOLOv3及YOLOv3-Tiny两种用于目标检测的典型CNN网络为例进行加速,并在Xilinx ZCU102 FPGA评估板上进行验证。

1 国内外研究现状

一个完整的深度学习框架通常包含训练与推理两个主要部分,本文所针对的主要是推理部分的优化与加速。

在软件加速方面,分解卷积核使得参数量大幅减少的SqueezeNet模型[2]、逐个通道进行卷积后将结果串联以减少计算量的MobileNet模型[3]、采用残差网络思想并在不影响精度的情况下降低分辨率的ShuffleNet模型[4]、更改卷积运算流程以提高网络效率的Xception模型[5]等轻量化模型被相继提出并不断优化。除轻量化模型以外,剪枝、奇异值分解、哈弗曼编码等轻量化技术亦得到广泛采用,该类方法的核心思想均为压缩网络模型大小,以减少计算量和降低计算复杂度,虽然会损失网络模型的部分精度,但模型推理速度会得到大幅度提升。目前,在众多轻量化算法中,量化算法具有较为突出的表现。

深度神经网络的训练阶段普遍采用float 32(简称FP32)的数据格式,量化算法即采用较低精度的数据格式(如float 16和int 8,简称FP16和INT8)代替高精度的数据格式[6]。此外,二值化(所有权重的值取+1或-1)[7]和三值化(将所有权重的值量化为[-α,0,+α]三个数之一,其中α为可训练的参数) [8]也是常用的量化方法。

在硬件加速方面,目前主流采用GPU,ASIC与FPGA三种智能计算架构进行深度神经网络模型加速[9]。其中,高性能GPU主要应用于神经网络训练阶段,对环境和库的依赖性较大,国内技术积累较弱,难以实现技术自主可控;ASIC是为特定需求而专门定制优化开发的架构,灵活性较差,缺乏统一的软硬件开发环境,开发周期长且造价极高;FPGA是可编程的半定制芯片,具有高灵活性、低延时特性,开发难点在于硬件逻辑实现复杂。目前,面向智能化航空电子系统多应用需求的智能计算加速技术多处于预研阶段,考虑后期的移植、再开发等工作,相对来说FPGA架构更适用于航空领域的智能计算加速。

2 面向CNN的软硬件协同加速方法

卷积神经网络在处理复杂智能问题时具有巨大的优势,但机载嵌入式环境的存储、计算资源均受限,为满足航空电子系统智能化场景感知的应用需求,本文设计了一种面向CNN的软硬件协同加速方法,如图1所示。

软硬件协同设计方法是针对系统开发中软硬件设计的相互作用关系而提出的[10]。由于在机载嵌入式环境中,存储资源与计算资源均较为受限,难以将规模庞大的神经网络移植到FPGA平台上,且FPGA并不擅于进行浮点运算,不能发挥FPGA在算力方面的优势,实现计算加速。因此,本文选用软硬件协同方法对卷积神经网络进行加速。软件优化方面,基于CAFFE框架实现结构优化与参数量化,旨在压缩网络模型规模,以大幅降低网络模型对嵌入式平台功耗、内存的需求。硬件加速方面,基于Verilog HDL设计加速算子,采用流水线+全并行的方式,充分利用有限的计算资源,达到计算加速的目的。软件优化与硬件加速两部分协同作用,使得卷积神经网络能够部署于资源受限的嵌入式环境。

本文构建了含雷达、舰船、坦克、汽车、建筑五类物体在内的空对地小目标数据集,从30°和90°两类不同视角以及彩色、红外、黑白三种不同视图场景进行影像采集,将采集到的12个视频片段逐帧截取成5 000余张1 024×768像素的高分辨率图片,参照PASCAL VOC标准数据集格式,标注生成以航空应用为背景的数据集,包括训练集3 000余张、测试集1 000余张和验证集1 000余张,单张图片平均含有7.4个物体。

开发阶段分为软件优化设计与硬件加速设计两部分。软件优化设计基于CAFFE框架对网络结构进行调整、优化,并采用量化算法压缩网络模型,为模型部署于嵌入式环境奠定基础。硬件加速设计基于FPGA 模块化设计思想,针对典型CNN网络中占用资源最多的卷积、池化网络层设计加速算子。

验证阶段将网络移植到Xilinx ZCU102评估板上进行验证。其中,卷积、池化加速算子封装为IP核,在PL端实现,其余各层算子在以ARM为核心的PS端实现,PL与PS之间通过DMA进行通信。

3 面向CNN的软件优化技术

由于构建的空对地小目标数据集以小目标(目标占图片总比例的0.5%以内)为主,且目标分布较为集中,综合考虑航空嵌入式环境对实时性的需求,选用YOLOv3及YOLOv3-Tiny两种典型CNN网络模型进行优化与加速[11]。YOLOv3及YOLOv3-Tiny模型具有高检测速度及小目标高检测精度的特点,适用于本文构建的数据集。

文献[12]指出,FPGA加速卷积神经网络推理过程时面临的主要瓶颈体现在两方面,一是计算量,二是数据传输。其中计算量对应本文所述计算资源受限的瓶颈,数据传输对应存储资源受限的瓶颈。具体来看,卷积神经网络中的卷积层、池化层等网络层涉及大量复杂浮点运算,浮点运算占用资源较多且运行速度较慢,而FPGA中DSP资源较少,若在FPGA加速之前对数据类型进行转化,可有效提高FPGA中的并行计算能力和计算效率,从而解决计算量庞大造成的瓶颈。此外,由于片上存储资源有限,大量中間网络层数据在运算过程中需进行多次访问存储,由此导致严重的传输延迟。为解决该瓶颈,本文对模型结构进行优化设计,减少中间参数,降低访问存储次数,从而降低数据传输开销,提高FPGA加速性能。

3.1 基于CAFFE框架的模型结构优化

CAFFE是一个开源的深度学习框架,无硬件与平台的限制,提供网络模型训练、微调、部署所需的完整工具包。与Darknet框架相比,CAFFE框架提供了卷积、池化、激活等多种算法接口,能够快速、高效地搭建网络模型;而Darknet框架较为小众,对除YOLO系列以外的网络模型支持度较低。本文基于CAFFE框架搭建YOLOv3以及YOLOv3-Tiny两种网络,并在原有模型基础上对卷积层结构进行调整优化。CAFFE框架虽然提供了卷积层的接口,但由于YOLOv3及YOLOv3-Tiny两种网络中,每一个卷积层之后都会连接一个归一化层(Batch Normalization,BN),而BN层主要用于训练时解决梯度消失或梯度爆炸问题,单独实现会占用大量显存空间。为提高本文构建模型的推理速度,减少BN层的运算,在基于CAFFE框架搭建时,将BN层参数合并到卷积层,实现为Conv+BN层。融合前原卷积层运算公式为

Y=W×X+b(1)

式中:X为卷积层输入特征图参数;W为卷积层滤波器参数;b为偏置值;Y为卷积层输出值。BN层共包含两部分运行,分别为归一化运算以及尺度变换偏移运算:

i← xi-μxδ2x+ε(2)

yi← γxi+β(3)

式中:μx为输入参数均值;δ2x为输入参数方差;ε为避免除数为0的微小正数;γ为尺度因子,用于调整数值大小;β为偏移因子,用于增加数据偏移,γ及β是模型在训练过程中自学习得到的两个参数。将BN层的两种运算融合到原卷积层运算中:

Y′=γ×(W×X+b)-μxδ2x+ε+β(4)

对该式进行展开,即可得到融合后新卷积层滤波器参数W′以及新偏置值b′:

W′=γδ2B+ε×W(5)

b′=γδ2x+ε(b-μx)+β (6)

将式(5)~(6)合并到式(4)中,即可得到融合BN层后的新卷积层运算公式:

Y′=W′×X+b′(7)

式(7)即为Conv+BN层输出值的运算公式。

基于以上推理,在原CAFFE框架中增加了Conv+BN层,可应用于基于CAFFE框架搭建的网络中,将BN层融合到卷积层内进行实现,消除推理过程中BN层单独运算对硬件资源的占用与消耗。

3.2 模型量化处理

网络模型参数量会直接影响存储资源和计算资源的占用情况,从而影响网络推理速度。为能更精准地提取出待识别图片的各类特征,神经网络通常需要大量卷积层和大量滤波器进行复杂浮点的乘加运算,这意味着一个精度较高的网络模型在计算量上可达10亿量级,参数量更是轻易突破百兆量级[13]。如在YOLOv3-Tiny网络中,仅第13层的参数量便高达8亿个,在不考虑复用的情况下,该层需进行的乘加运算约9 000万次。如果将原始FP32型数据映射到硬件上,不仅会占用大量的BRAM存储资源,其推理过程更会消耗大量的DSP计算资源,这对资源受限的嵌入式环境来说是难以承受的。基于硬件资源的考虑,采用量化算法将FP32位数据映射为INT8位数据,节省存储资源占用情况。以n×n卷积核K为例,量化过程为

K=(k11,k12,…,kin,k(i+1)1,…,knn)(8)

kmax=max(k11,k12,…,kin,k(i+1)1,…,knn)(9)

δ=127/kmax(10)

K′=(k11×δ,k12×δ,…,kin×δ,…,knn×δ) (11)

式(8)为卷积核K的n2个参数;式(9)取卷积核K参数中的最大值,记为kmax;式(10)计算量化系数δ,其中127为INT8值域中的最大值;式(11)为量化后的卷积核K′。偏置值由于数量较少,对其进行量化并不会节省太多存储资源,反而会导致模型精度严重下降,因而对偏置值直接进行保存处理。

使用构建的空对地小目标数据集中的测试集进行精度测试,模型量化前后对比如表1所示。网络模型压缩处理后,其规模可缩小约3/4,解决了硬件存储资源受限的瓶颈。

量化算法主要用于压缩参数规模庞大的网络模型,减小权重参数的存储资源占用,缓解嵌入式环境存储资源受限的瓶颈,为网络模型移植到嵌入式环境奠定基础。

4 面向CNN的硬件加速技术

FPGA作为一种可编程重构的硬件架构,能够很好地兼顾处理速度与调控能力。目前,高层次综合(High-Level Synthesis,HLS)与Verilog HDL是常用于设计神经网络加速模块的硬件结构及硬件语言。HLS是指将高层次语言(如C, C++, System C等)描述的逻辑结构,自动转换成低抽象级语言描述的电路模型[14],更注重于上层算法的实现,但基于HLS结构实现的神经网络有两个弊端,一是资源占用不合理、不可控,网络运行时能达到的并行度较为受限,特别是搭建中大型神经网络时,并行度较低直接导致其推理速度难以提升;二是转换后的代码不具备可读性,这不仅加大了排查故障的难度,在不满足设计需求时也很难对其进行优化。

Verilog HDL适合于RTL级的硬件描述,用于从算法级、门级到开关级的多种抽象设计层次的数字系统建模,更偏重于底层,因而基于Verilog HDL的设计更灵活,且效率更高。

在YOLOv3(共106层网络层)及YOLOv3-Tiny(共23层网络层)网络中,卷积层与池化层(共94层)占所有网络层的73%左右,其中涉及的乘加、比较等运算是影响其推理性能的主要因素。为充分合理利用有限的计算资源以满足卷积神经网络中的大量运算,从而达到加速目的,基于Verilog HDL设计卷积、池化两种加速算子,并将其封装为IP核,便于在加速其他具有相同结构的网络模型时复用。

4.1 卷积加速算子的设计与实现

卷积加速算子实现3×3滤波器的卷积运算。采用全并行加流水线方式,单次卷积运算调用9个乘法器,每个时钟处理9组数据的乘法运算,加法运算通过2级流水线完成。

卷积算子端口时序如图2所示。ORDER为输入特征图阶数,特征图读取共需ORDER×ORDER个CLK时钟周期,滤波器需9个CLK时钟周期,偏置值Bias需1个CLK时钟周期,结果特征图从第(2×ORDER+7)个CLK时钟周期开始输出(无偏置值时,有偏置值则从第(2×ORDER+8)个时钟周期开始输出),每个时钟周期输出一个值,输出(ORDER-2)2个CLK时钟周期。

4.2 池化加速算子的设计与实现

池化加速算子实现步长为2的最大池化运算,采用全并行加流水线方式。

池化加速算子端口时序如图3所示。其中,ORDER为输入特征图阶数,特征图输入共需ORDER×ORDER个CLK时钟周期,结果特征图从第(2×ORDER+1)个CLK时钟周期开始输出,每隔一个时钟周期输出一个值,输出(ORDER/2)2个CLK时钟周期。由于每次读取2×2数据进行比较之后,输出数据会减少一半,因此valid信号表现为2分频。

4.3 卷积加速算子仿真及资源占用情况

以5×5特征图与3×3滤波器进行卷积运算为例,仿真结果如图4所示。每帧特征图输入到输出延时为2行输入的时间,使用2个FIFO缓存将特征图输入数据延时1行和2行,当第3行特征图数据到达时,由于延时,此时第1行和第2行数据会同时输出。将3行数据和每行对应的滤波器数据进行滑动相乘,通过2级流水相加求和,即可得到卷积运算结果。

以Xilinx ZCU102评估板上的运行为例,占用资源情况如表2所示。该算子在9组乘加并行运算且含2级流水线的条件下,DSP资源仅占用了9个,占总资源的0.36%, LUT仅占用了0.07%,资源占用量较少,且并行度较高,能够达到节省计算资源且运算加速的目的。4.4 池化加速算子仿真及资源占用情况

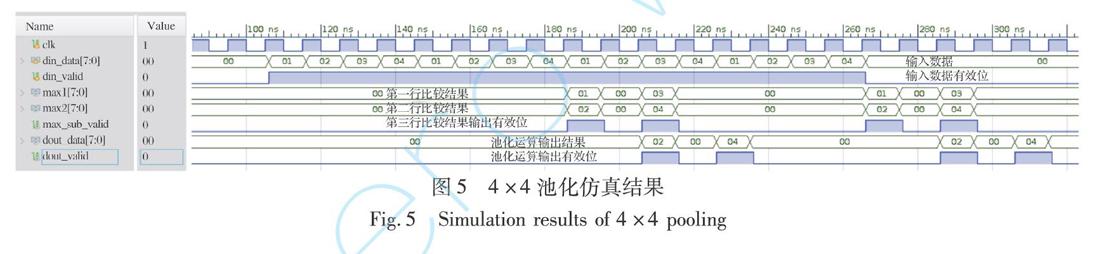

以4×4特征图、步长为2进行池化运算为例,仿真结果如图5所示。当奇数行特征图数据输入时,会写入FIFO进行缓存。当偶数行特征图数据输入时,同时读出FIFO中的数据,每隔两个数据进行2×2的数据比较,将最大数据进行输出。

以Xilinx ZCU102评估板上的运行为例,该算子占用资源情况如表3所示。

5 测试与验证

本文在Xilinx ZCU102评估板上进行验证,该评估板含有2 520个DSP单元、32 Mb RAM内存、512 MB与PL端相连的DDR4存储器件以及4 GB与PS端相连的DDR4存储器件,能够满足神经网络硬件部署的基本资源需求。在100 MHz时钟频率下,YOLOv3网络对单张图片的推理过程需1.49×107个时钟周期,YOLOv3-Tiny网络对单张图片的推理过程需4.17×106个时钟周期。

为评估本文算法在航空背景特定数据集上的有效性以及推理阶段的时效性,本文以构建的空对地小目标数据集作为样本集,采用功耗、均值平均精度(mean average precision,mAP)以及推理阶段运行时间FPS(frames per second)作为评价指标,衡量智能计算加速技术的综合性能。表4列出了加速方法基于构建的空对地小目标数据集(1 024×768像素)在不同硬件平台上测试的功耗与运行时间的对比情况。

采用量化后的同一权重参数在不同硬件平台上进行测试,测试结果表明,在CPU,GPU与FPGA三种硬件平台上,網络检测精度基本一致。在模型推理过程的加速方面,两种网络部署于ZCU102评估板后的运行速度均有大幅提升。与原网络在CPU上的运行速度相比,YOLOv3提升了65倍,可达到每秒6帧,YOLOv3-Tiny可达到每秒23帧。虽然推理速度与高性能GPU相比还有较大差距,但在功耗方面,ZCU102上的功耗不到GPU功耗的十分之一,能够满足嵌入式环境低功耗的需求。可见,卷积加速算子与池化加速算子在加速神经网络模型的推理过程方面发挥了重要作用。检测效果如图6所示。

綜上,本文采用了软硬件协同加速技术,为卷积神经网络部署于资源受限的嵌入式环境提供了支撑。其中,软件优化技术对模型结构进行优化,并实现量化算法,有效压缩了网络模型规模,极大缓解了机载嵌入式环境存储资源受限的瓶颈,为神经网络移植到嵌入式平台建立基础。硬件加速技术基于Verilog HDL设计并实现卷积、池化两种加速算子,仅需占用少量计算资源即可实现这两种复杂运算。通过软硬件两种加速技术的协同作用,有效解决机载嵌入式环境下部署卷积神经网络时面临的存储资源紧缺与计算资源受限瓶颈,达到智能计算加速的目的。

6 结 论

面向空战过程智能化的应用需求,提高有人机/无人机自主感知、目标识别跟踪、自主决策等能力,设计并实现了应用于资源受限的嵌入式环境的CNN软硬件协同加速技术,旨在解决庞大模型参数量与有限存储资源的冲突问题以及大量复杂浮点运算与计算资源紧缺的冲突问题。在开发阶段,构建了空对地小目标数据集,基于CAFFE框架对YOLOv3和YOLOv3-Tiny两种网络进行了结构优化。对两种模型进行压缩量化处理,压缩模型约3/4。基于Verilog HDL设计并实现两种加速算子,仅需占用少量资源即可完成相应运算。通过软硬件协同作用,达到推理过程加速的目的。其中,基于CAFFE框架的结构优化方法、模型压缩量化算法以及卷积池化加速算子均具备一定的通用性,便于构建其他网络模型时使用。在验证阶段,将两种网络模型部署于Xilinx ZCU102评估板上进行了验证。实验证明,两种加速算子在计算资源紧缺的嵌入式环境下,可有效加速两种网络的推理过程。

下一步工作主要着眼于构建加速算子库,封装除卷积、池化以外的多种算子,搭建结构更为复杂的神经网络模型,以满足智能化航空电子系统的多应用需求。同时,设计数据重用算法,提高存储空间利用率,进一步加速嵌入式环境下深度神经网络模型的推理过程。

参考文献:

[1] 鲜勇,李扬. 人工智能技术对未来空战武器的变革与展望[J]. 航空兵器,2019,26(5): 26-31.

Xian Yong,Li Yang. Revolution and Assumptions of Artificial Intelligence Technology for Air Combat Weapons in the Future[J]. Aero Weaponry,2019,26(5): 26-31. (in Chinese)

[2] Wu B C,Iandola F,Jin P H,et al. SqueezeDet: Unified,Small,Low Power Fully Convolutional Neural Networks for Real-Time Object Detection for Autonomous Driving[C]∥2017 IEEE Conference on Computer Vision and Pattern Recognition Workshops (CVPRW),2017: 446-454.

[3] Chollet F. Xception: Deep Learning with Depthwise Separable Convolutions[C]∥2017 IEEE Conference on Computer Vision and Pattern Recognition (CVPR),2017: 1251-1258.

[4] Shen Y R,Han T,Yang Q,et al. CS-CNN: Enabling Robust and Efficient Convolutional Neural Networks Inference for Internet-of-Things Applications[J]. IEEE Access,2018,6: 13439-13448.

[5] Zhang X Y,Zhou X Y,Lin M X,et al. ShuffleNet: An Extremely Efficient Convolutional Neural Network for Mobile Devices[C]∥2018 IEEE Conference on Computer Vision and Pattern Recognition(CVPR),2018: 6848-6856.

[6] Vanhoucke V,Senior A, Mao M Z. Improving the Speed of Neural Networks on CPUs[C]∥Deep Learning and Unsupervised Feature Learning Workshop,NIPS,2011.

[7] Courbariaux M,Bengio Y,David J P. BinaryConnect: Training Deep Neural Networks with Binary Weights During Propagations[C]∥Advances in Neural Information Processing Systems(NIPS), 2015: 3123-3131.

[8] Alemdar H,Leroy V,Prost-Boucle A,et al. Ternary Neural Net

works for Resource-Efficient AI Applications[C]∥2017 International Joint Conference on Neural Networks (IJCNN),2017: 2547-2554.

[9] Sze V,Chen Y H,Yang T J,et al. Efficient Processing of Deep Neural Networks: A Tutorial and Survey[J]. Proceedings of the IEEE,2017,105(12): 2295-2329.

[10] 崔小乐,陈红英,崔小欣,等. 一种软硬件协同设计工具原型及其设计描述方法[J]. 微电子学与计算机,2007,24(6): 28-30.

Cui Xiaole,Chen Hongying,Cui Xiaoxin,et al. A HW/SW Codesign Design Tool and its Specification[J]. Microelectronics & Computer,2007,24(6): 28-30. (in Chinese)

[11] Redmon J,Divvala S,Girshick R,et al. You Only Look Once: Unified,Real-Time Object Detection[C]∥ 2016 IEEE Conference on Computer Vision and Pattern Recognition (CVPR), 2016: 779-788.

[12] 吴艳霞,梁楷,刘颖,等. 深度学习FPGA加速器的进展与趋势[J]. 计算机学报,2019(11): 2461-2480.

Wu Yanxia,Liang Kai,Liu Ying,et al. The Progress and Trends of FPGA-Based Accelerators in Deep Learning[J]. Chinese Journal of Computers, 2019(11): 2461-2480. (in Chinese)

[13] Cheng Y,Wang D,Zhou P,et al. Model Compression and Acce-leration for Deep Neural Networks: The Principles,Progress,and Challenges[J]. IEEE Signal Processing Magazine,2018,35(1): 126-136.

[14] 卢冶,陈瑶,李涛,等. 面向边缘计算的嵌入式FPGA卷积神经网络构建方法[J].计算机研究与发展,2018,55(3): 551-562.

Lu Ye,Chen Yao,Li Tao,et al. Convolutional Neural Network Construction Method for Embedded FPGAs Oriented Edge Computing[J]. Journal of Computer Research and Development,2018,55(3): 551-562. (in Chinese)

Software and Hardware Cooperative Acceleration Technology for CNN

Li Xinyao1*,Liu Feiyang1,2,Wen Pengcheng1,2,Li Peng 1,2

(1. Xian Aeronautics Computing Technique Research Institute,AVIC,Xian 710068,China;

2. Aviation Key Laboratory of Science and Technology on Airborne and Missileborne Computer,Xian 710068,China)

Abstract: To meet requirements of building intelligent avionics systems,and improve the intelligent combat level of manned/unmanned aerial vehicles,the software and hardware cooperative acceleration technology for CNN is designed and implemented to solve complex problems such as target recognition,auxiliary decision-making,and autonomous planning. Aiming at solving the conflicts between the huge amount of parameters and the limited storage resources for embedded environment,the neural network model is optimized with model structure optimization and quantization of parameters. Aiming at solving the conflicts between complex floating-point operations and the shortage of computing resources,the convolution accelerating operator and the pooling accelerating operator are designed based on Verilog HDL. The pipeline and full parallel method are used to achieve the purpose of acceleration. Through the synergy of software optimization and hardware accelerated,the inference process of convolutional neural network is accelerated. Two popular CNN networks,that are YOLOv3 and YOLOv3-Tiny,are used as examples to accelerate and verify on the Xilinx ZCU102 FPGA development board. The results show that compared with the original models,the parameters of the accelerated models can be compressed about 3/4. The inference speed of YOLOv3 is increased by nearly 65 times,and that of YOLOv3-Tiny is increased by about 23 times.

Key words: intelligent computing;hardware acceleration;target detection;model compression;FPGA

收稿日期:2020-01-19

基金項目:航空科学基金项目(2018ZC31002;2018ZC31003)

作者简介:李欣瑶(1994-),女,陕西西安人,硕士, 研究方向为智能计算加速技术。