55nm双大马士革结构中电镀铜添加剂的研究

2018-09-12曾绍海陈张发

曾绍海,林 宏,陈张发,李 铭

(上海集成电路研发中心有限公司,上海 201210)

随着集成电路制造技术进入数十纳米技术代,更细更长的金属互连线的电容电阻延迟(RC延迟)已无法忽略,并成为超大规模集成电路芯片的RC延迟的主要组成部分之一.业界普遍采用电阻率更低的铜和介电常数更低的低介电常数介质(Low-k介质)来降低后道互连线的RC延迟[1-5].IBM公司在1997年宣布了一项互连技术的重大变革——铜互连大马士革(Damascene)工艺[6],即现在国际上铜布线技术路线采用的嵌入式工艺.在深亚微米刻槽中能够淀积出无空洞和无裂缝的铜填充技术是铜嵌入式工艺中的关键技术之一.电镀是完成铜互连线的主要工艺.由于铜电镀要求在厚度均匀的整个硅片镀层以及电流密度不均匀的微小局部区域(超填充区)能够同时传输差异很大的电流密度.再加上集成电路特征尺寸不断缩小和沟槽深宽比增大,沟槽的填充效果和镀层质量很大程度上取决于电镀液的化学性能.有机添加剂是改善电镀液性能非常关键的因素,填充性能与添加剂的成份和浓度密切相关,关于添加剂的研究一直是电镀铜工艺的重点之一.本文研究了不同添加剂配比电镀铜的工艺性能以及在铜互连工艺中的应用.通过添加剂不同配比的优化,找出一组最佳的添加剂配比,并将该添加剂配比所镀的铜膜运用在55nm技术代的铜互连工艺中,拥有达到业界标准的电学性能和可靠性.

1 实验部分

本文采用12英寸设备Sabre的电镀设备,使用半导体业界通用的电镀液,加入不同配比的添加剂,运用国内某半导体制造公司成熟的55nm技术代的铜互连工艺,然后评估其工艺性能,电学性能和可靠性.

1.1 图形片的准备

本文采用的55nm技术代的铜互连工艺图形片,分别采用符合55nm技术代设计规则的铜互连层次光刻版来实现单大马士革工艺(Single Damascene)或双大马士革工艺(Dual Damascene),通过反复利用光刻工艺、刻蚀工艺、湿法清洗工艺、化学气相沉积(Chemical Vapor Deposition,CVD)工艺、物理气相沉积沉积(Physical Vapor Deposition, PVD)工艺和化学机械抛光(Chemical Mechanical Polishing, CMP)工艺,完成第1层金属线(Metal 1, M1)、第2层金属线(Metal 2, M2)及第1层通孔(Via1)、第3层金属线(Metal 3, M3)及第2层通孔(Via2)的铜互连工艺集成.

1.2 测试设备

本实验采用Four Dimensions公司的4探针测试系统Model 280进行方块电阻及其不均匀性测试,使用美国KLA Tencor公司的表面轮廓仪P 16+进行膜应力监控;采用了CASCADE公司的多功能探针台S300进行电镀液和添加剂的电学测试和可靠性测试.

2 结果与讨论

2.1 添加剂不同配比的优化

根据文献[7-8]报道,抑制剂(S)都具有抑制电镀活性的功能团,过多的抑制剂会增加电镀体系的电化学反应电位,进而减低整体沉积速率.这既降低了生产效率,也增加了添加剂用量,不利于大生产实际应用,因此,在保证电镀铜工艺正常工作的前提下,应尽量减少抑制剂的浓度.本文采用标准电镀工艺菜单,对加速剂(A)和抑制剂不同配比的6种样品A10/S3,A5/S3,A2/S5,A10/S5,A5/S5和A5/S10,进行了方块电阻、不均匀性和退火后应力的研究.

2.1.1 不同A/S下的光片工艺性能

对于不同配比下所电镀的铜膜,本文采用Four Dimensions公司的4探针测试系统Model 280CI进行方块电阻及其不均匀性测试.并采用KLA-Tencor公司的表面轮廓仪P 16+进行退火后应力测试.结果见表1.

可以看到,加速剂和抑制剂的比例改变对方块电阻及不均匀性的影响有限,对退火后铜膜的应力影响很小.但是,A和S配比为2∶5和10∶5时,样品的应力略高其他样品,这说明增加抑制剂会引起铜应力升高.而A和S配比为10∶5时的应力比A和S配比为2∶5的应力高1.1MPa,可能是表面轮廓仪P 16+引起的测量误差.

2.1.2 不同A/S下的填充性能

图1 55nm技术代SRAM版图结构示意图Fig.1 Schematic diagram of the SRAM layout of 55 nm technology generation

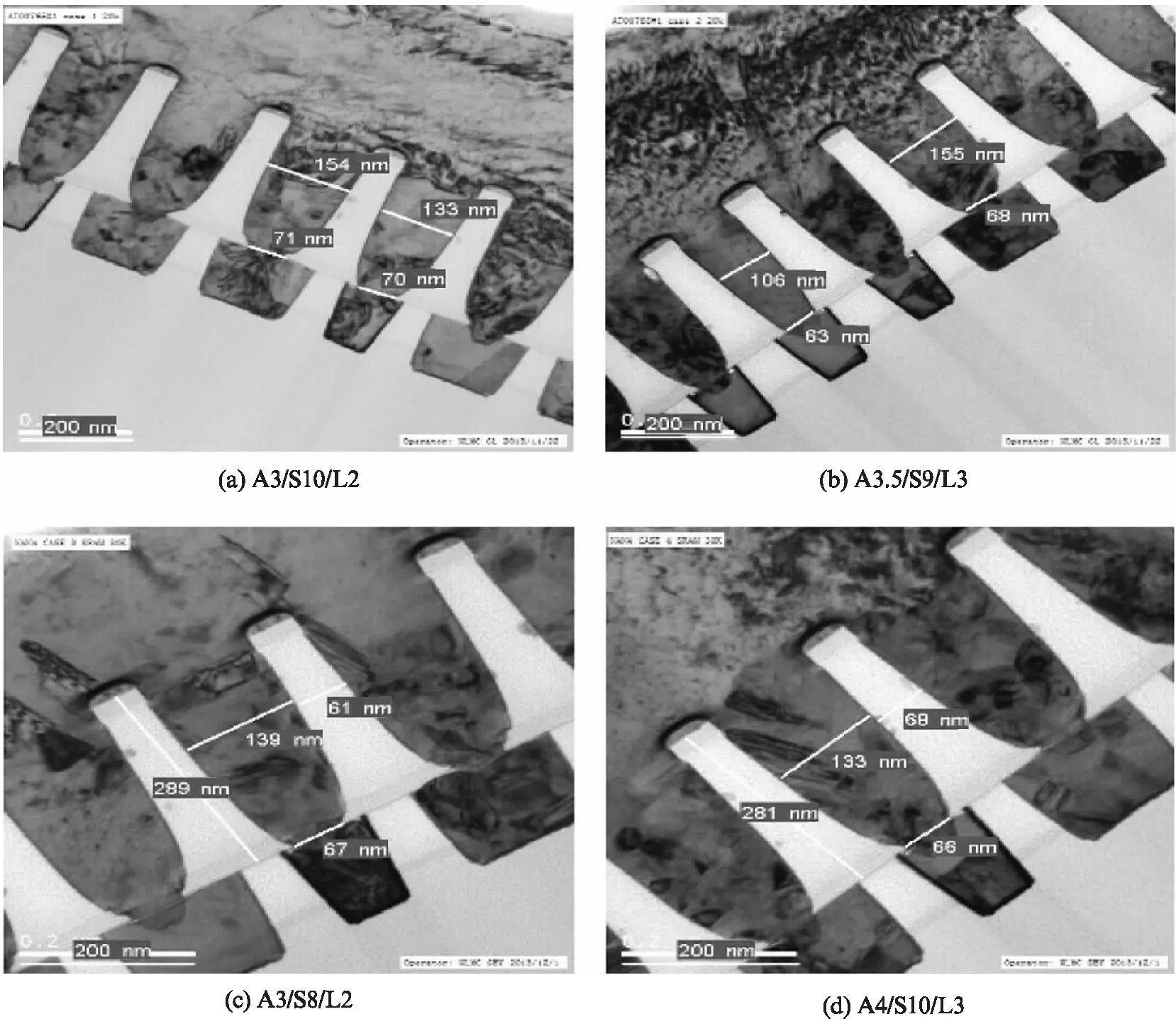

采用55nm技术代的标准双大马士革结构SRAM的添加剂配比的填充性能研究,其版图结构如图1所示,通孔尺寸约为70nm,沟道尺寸约为150nm.由于业界电镀铜添加剂配比的最著名的方法(Best Known Method, BKM)是A3/S10/L3,结合现有电镀设备的工艺能力,本文分别采用A3/S10/L2、A3.5/S9/L3、A3/S8/L2、A4/S10/L34种添加剂配比进行铜填充实验,所镀图形片先采用FIB技术定点切割硅片中心区域的SRAM结构剖面,选择SRAM通孔密集区,如图1中划线位置,然后采用TEM进行SRAM结构剖面的拍摄.不同添加剂配比对55nm技术代SRAM结构的剖面图如图2所示.

从图2可以看出,电镀添加剂在55nm技术代SRAM结构获得无缝、无空洞的填充效果.添加剂配比A3.5/S9/L3和A4/S10/L3的填充结果表明,平坦剂在3mL/L范围内不会影响双大马士革结构的填充性能,平坦剂浓度太高会增加铜膜内的杂质含量,同时增加铜膜的应力.添加剂配比A3/S10/L2和A4/S10/L3的填充结果表明,加速剂和抑制剂的配比在1∶2.5至1∶3.3之间都能在55nm技术代SRAM结构中获得好的填充效果,选择添加剂配比A3/S9/L2作为最佳的电镀铜工艺体条件.

图2 不同添加剂配比55 nm技术代SRAM结构剖面的TEM图Fig.2 TEM spectra of SRAM structural profiles of 55 nm technology generation with different additive ratio

2.2 电学性能测试

注: 1) M2/M3蛇形线0.09μm×9720μm;2) Via1/Via2通孔链3612个.

采用添加剂配比A3/S9/L2为电镀铜工艺体条件,对55nm技术代的M2蛇形线、M3蛇形线、Via1通孔链和Via2通孔链进行了添加剂的电学性能评估.采用的55nm技术代图形片由国内某半导体制造公司提供,并采用CASCADE公司的多功能探针台S300对12英寸硅片上的63个Die逐一进行测试.55nm技术代的相关电学测试的性能指标如表2所示.

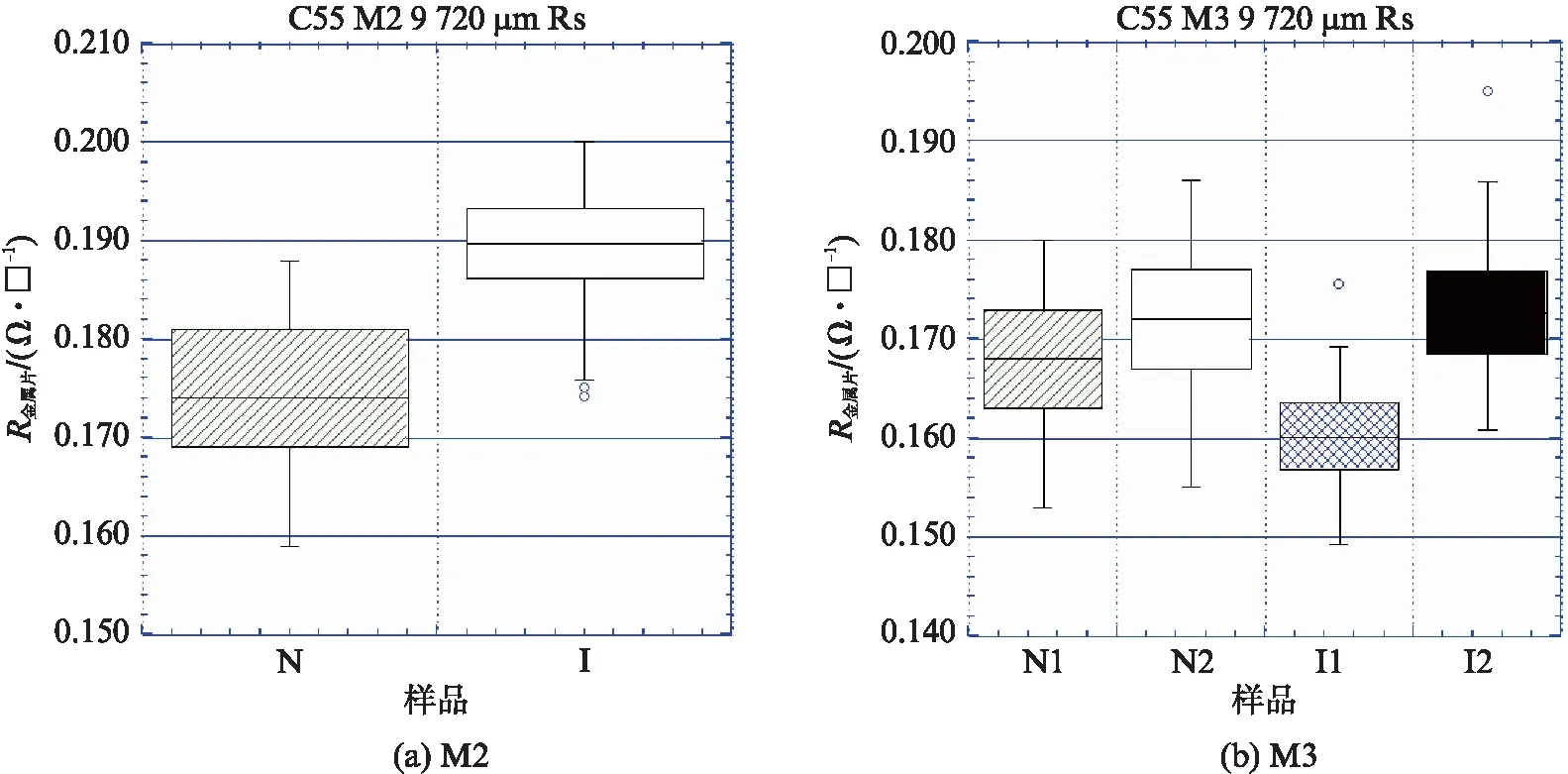

55nm技术代M2和M3的蛇形线的设计线宽为0.09μm,本文选择了较长的9720μm的蛇形线测试结构.从图3可以看出,本文采用的添加剂配比N1(A3/S9/L2)、N2(N1的重复实验)与业界标准添加剂I1(A3/S10/L3)、I2(I1的重复实验)的M3电学结果均在目标值0.176Ω/□上下波动,且本文采用的添加剂配比的片间波动要小于业界标准添加剂.

图3 不同添加剂配比,9720μm蛇形线的电学测试Fig.3 The electrical test of 9720μm Snake Wire with different additive ratio

55nm技术代Via1和Via2的通孔线宽为0.1μm,通孔链个数为3612.从图4可以看出,本文采用的添加剂配比的Via1电学结果略好于业界标准添加剂,2.5Ω的目标值更近,且波动范围更小.

图4 不同添加剂配比对(a) Via1,(b) Via2 3612个通孔链的电学测试Fig.4 The electrical test of (a)Via1, (b)Via2 3612 through holes chain with different additive ratio

根据上述电学测试结果,本文采用的添加剂配比在55nm技术代的电学性能接近业界标准添加剂,金属线的方块电阻和通孔电阻均达到工艺集成的控制规范,满足半导体生产线的要求.

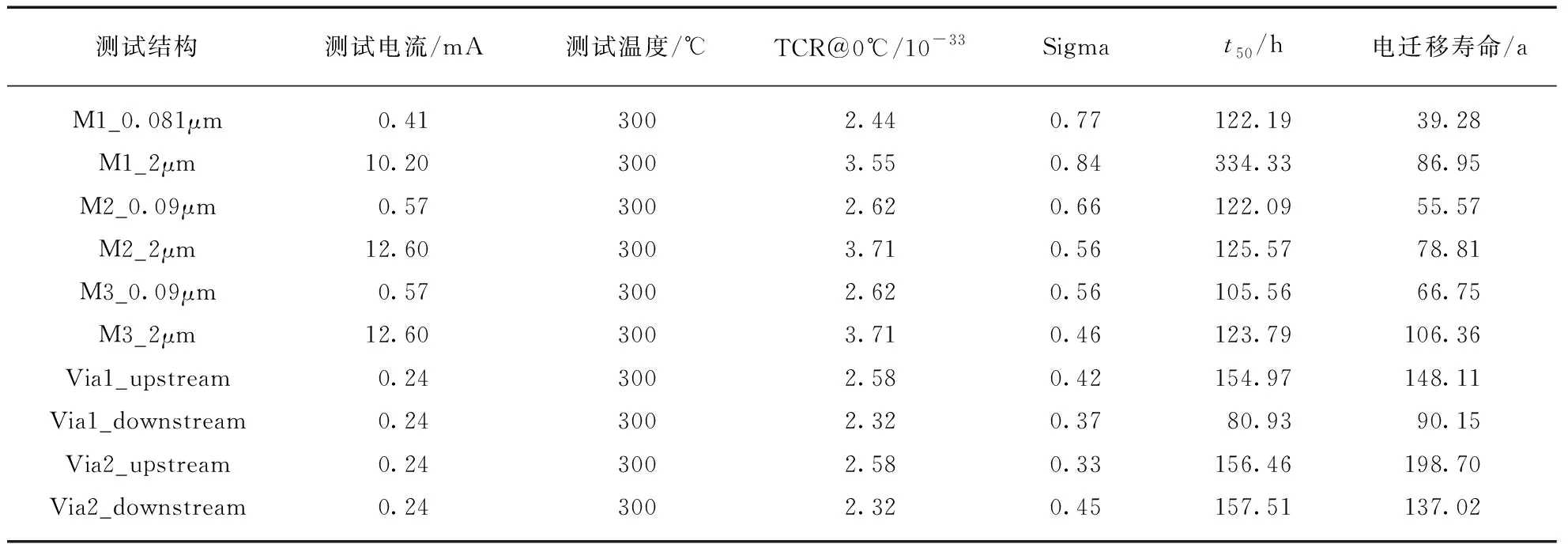

2.3 可靠性测试

本文采用国内某半导体制造公司的成熟55nm技术代工艺完成本文采用的添加剂配比所镀的图形片的铜后道工艺集成,并完成芯片切割和封装,然后采用CASCADE公司的多功能探针台S300对封装后的芯片分别进行了金属线条和通孔的电迁移测试,具体结果如表3所示.

表3 55nm技术代金属线和通孔的电迁移测试结果对比

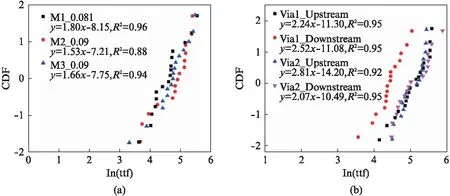

封装级电迁移测试温度恒为300℃.由于金属线条的宽度和厚度不同,外加测试电流会根据不同测试结构做相应调整,一般来说,为了控制测试时间,越宽越厚的金属线条需要施加越大的测试电流应力.M1的0.081μm线条的测试电流为0.41mA,而M1的2μm线条的测试电流较大,为10.2mA.M2和M3的0.09μm线条的测试电流均为0.57mA,而M2和M3的2μm线条的测试电流均增加至12.6mA.Via1和Via2的测试电流均为0.24mA.通过对20个测试样品的数据进行绘图得到各测试结构的拟合曲线,如图5所示,经过理论计算可以得到表3中的可靠性寿命,结果表明,各测试结构的电迁移寿命均达到可靠性要求,大于10年.

图5 (a)不同添加剂配比在55nm技术代M1,M2,M3直线条结构的电迁移测试,(b)不同添加剂配比在55nm技术代Via1,Via2通孔结构的电迁移测试Fig.5 (a) The electromigration test of M1, M2, M3 linear structure with different additive ratio in 55nm technology generation, (b) the electromigration test of Via1, Via2 through holes with different additive ratio in 55nm technology generation

3 结 论

经过对不同添加剂配比电镀铜的方块电阻、不均匀性、退火后应力以及填充性的测试,选择了最佳的添加剂配比A3/S9/L2作为电镀铜工艺体条件,实现55nm技术代大马士革结构的无空洞、无缝的填充效果;通过了55nm技术代的电学测试,基本电学性能达到该技术代工艺集成的控制规范;满足半导体生产线的量产要求.