FPGA中开关矩阵的研究

2016-12-06张艳飞单悦尔

胡 凯,谢 达,刘 彤,张艳飞,单悦尔

(中国电子科技集团公司第58研究所,江苏无锡 214072)

FPGA中开关矩阵的研究

胡凯,谢达,刘彤,张艳飞,单悦尔

(中国电子科技集团公司第58研究所,江苏无锡 214072)

开关矩阵是现场可编程门阵列FPGA芯片中最重要的组成部分之一。通过对FPGA中开关矩阵进行分析和研究,介绍了开关矩阵的布局和绕线方式,建立了开关矩阵的基本模型,对开关矩阵模型进行了仿真、分析和优化。重点分析了开关矩阵速度与各参数因子之间的关系,结果表明优化后的开关矩阵具有很好的性能。

FPGA;开关矩阵;布线;延时

1 引言

现场可编程门阵列FPGA是一种半定制电路,具有开发周期短、成本低、风险小、集成度高、灵活性大以及便于电子系统维护和升级的优点,FPGA是数字集成电路的主流芯片,被广泛应用在通信、控制、视频、信息处理、消费电子、互联网、汽车以及航空航天等诸多领域[1]。

开关矩阵Switch matrix(简称SW)和绕线资源是FPGA结构中最基本、最核心的逻辑部件,具有层次化布局和布线架构的FPGA设计已经成为可编程逻辑器件设计的热点,拥有最佳的面积和延时性能[2~3]。开关矩阵是连接CLB、DSP、BRAM、IO、CLK、MAC、 PCIE、GTP等各个模块之间的互连枢纽,由大量的MUX开关、配置SRAM以及互连线构成,遍布于FPGA芯片各个部位,开关矩阵的速度、功耗和面积决定着整个芯片的性能[4~5]。本文对开关矩阵进行了分析和研究,首先介绍了FPGA中开关矩阵的布局布线,分析了绕线资源的类型和命名方式,并建立了开关矩阵的基本模型,对开关矩阵模型进行了仿真、分析和优化,并详细阐述了优化过程和结果。

2 原理

FPGA中所有逻辑功能块,如CLB、IOB、DSP、BRAM等,都连接到各自相同的开关矩阵,再通过开关矩阵连接到全局互联资源,整个FPGA芯片由大量相同的开关矩阵阵列构成,如图1所示。图1为Xilinx Virtex 5系列芯片开关矩阵布局示意图,图中包括SW与CLB、DSP、BRAM以及IOB的连接关系。开关矩阵按阵列重复分布,是连接各逻辑模块的枢纽。

图1 开关矩阵布局示意图

开关矩阵和其他逻辑资源是通过绕线连接的,绕线资源贯通南北,是开关矩阵的重要组成部分,直接影响着芯片逻辑布通率和芯片的工作频率。此处以Xilinx公司Virtex 5系列FPGA芯片为例,简单介绍绕线资源的特性。Virtex 5绕线资源主要包含以下几种绕线类型:首先是外部绕线,即开关矩阵与开关矩阵之间的绕线,可分为二倍线、五倍线和长线;其次是局部绕线,即开关矩阵与其他MACRO连接的局部直连线;此外还包括时钟线以及MACRO的快速进位链等。下面对绕线资源中最基本、最核心的绕线——二倍线和五倍线作简单介绍。图2所示为二倍线和五倍线的示意图,一个方框代表一个开关矩阵SW。二倍线指一根信号线长度跨越了两个SW宽度,方向包含东南西北四个方向,如图中的NW2、NE2、SW2、SE2等。其中二倍线包含了一个中间点信号输出,如图中的NW2MID0,其为一倍线宽度。五倍线为信号线跨越五个SW宽度,如图中的WN5、NW5、NE5、EN5、ES5、SE5、SW5、WS5、NR5、ER5、SL5、WL5等。

图2中开关矩阵的绕线类型可以通过命名方式来确定,用Xilinx Design Language(XDL)在ISE TCL命令行中输入“xdl-report-pips-all_conns xc5vlx20t”,可以产生xc5vlx20t器件的所有绕线和宏单元的连接信息。其开关矩阵的绕线和命名方式如图2中所示,此处以五倍线 SE5BEG0为例作简单介绍。SE5BEG0-SE5MID0-SE5END0为某一根线的走线方式,其中SE5BEG0中第一个字母E=east、N=north代表走线方向,EN表示先向东走,再向北走,5代表五倍线,即该线总共跨越5个SWB,BEG代表信号线的起点,即一个SW中某个输出端口,MID代表走线的中间点,END代表走线的结束端,0代表该类线的其中某一条序号。因此绕线方式组成如图2中所示的形式。

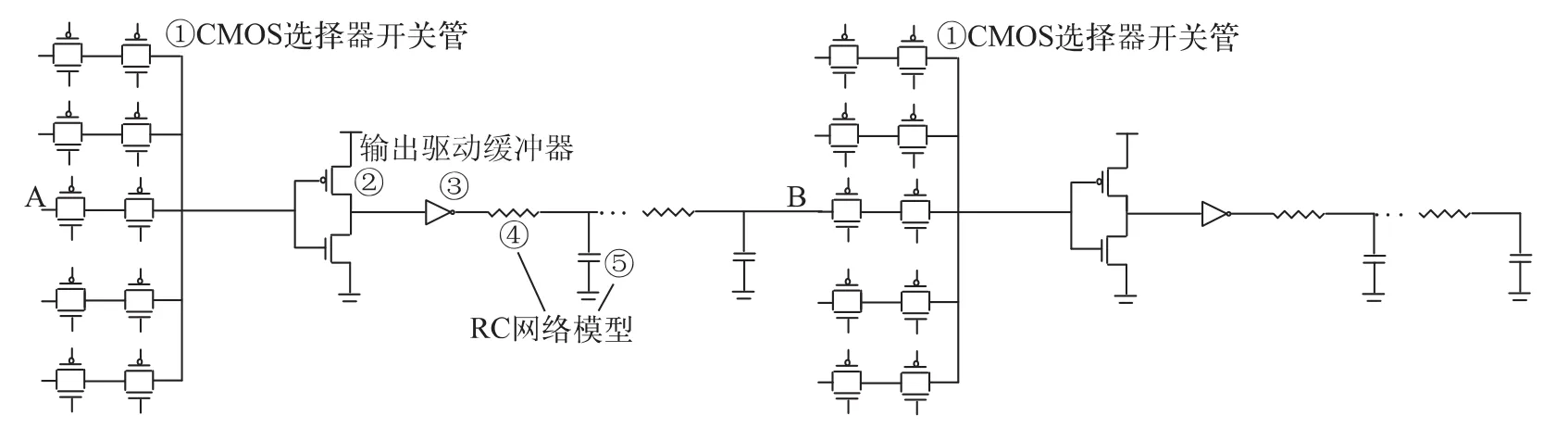

开关矩阵内部由大量的选择器开关组成,构成了水平通道和垂直通道的枢纽,包括水平方向走线的选择器开关、竖直方向走线的选择器开关、内部互连选择器开关以及局部MACRO连接的选择开关等,一种设计方案开关矩阵和绕线资源的简化模型1如图3所示,包含CMOS选择器开关管(图中①),输出驱动缓冲器(图中②和③),绕线资源可以简化成图中④和⑤所示的Elmore的RC网络模型[6]。

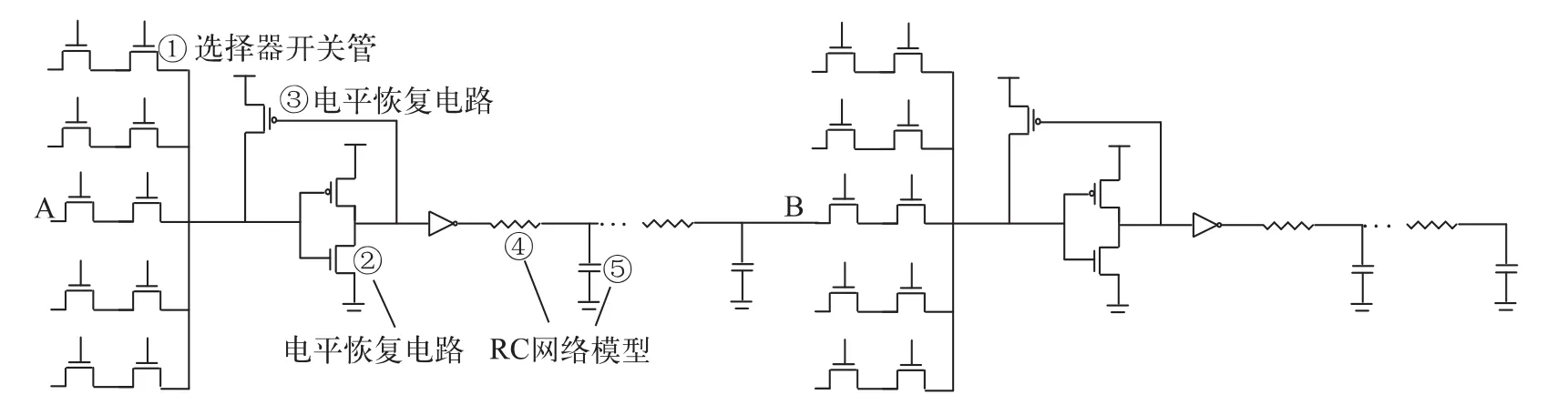

在图3的基础上,另一种开关矩阵和绕线资源设计方案的简化模型2如图4所示,包含选择器开关管①,此处采用NMOS单管作为选择开关,NMOS单管开关速度快、面积小,但NMOS在传输高电平信号时存在阈值损耗,因此需要图中②和③所示的电平恢复电路进行电平还原,绕线资源为④和⑤所示的RC网络模型。

3 仿真与优化

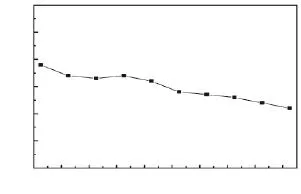

对图3中的结构进行仿真,选择40 nm UMC工艺,电源电压为1.1 V,模型中CMOS选择器开关①的开关电压为1.1 V,仿真结果如图5所示,AB间延时为210 ps,功耗为37.65 nA。AB具有很好的速度,且温度稳定性很好,功耗较小,但是模型1采用了CMOS作为开关,面积增大了一倍,因此该设计方案是以牺牲面积为代价的。

图3 开关绕线资源的简化矩阵和模型1

图4 开关矩阵和绕线资源的简化模型2

图5 延时随温度变化示意图

图4为设计方案2的基本模型,与设计方案1相比,面积缩小了近一半,选择40 nm UMC工艺进行仿真,电源电压为1.1 V,模型中选择器开关①的开关电压为1.1 V,保持方案设计2中的电路结构和尺寸以及仿真环境与设计方案1完全相同,对图4的模型进行仿真,仿真AB间的延时为1.88 ns,功耗为32.27 nA,延时明显增大,因此需要进行优化。

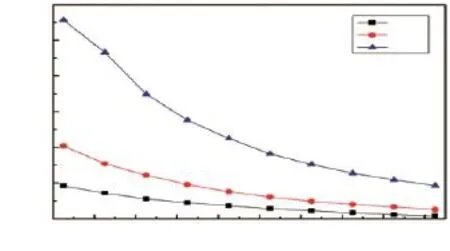

对图4中①的开关控制电压进行调节,对不同开关电压下的延时进行仿真,仿真结果如图6所示,速度随着开关电压的增大有了显著的提高,在1.28 V具有很好的速度和温漂稳定性,因此可以通过采用特殊的工艺,使用高压MOS开关管,升高开关电压进行提速,然而针对普通工艺中的普通管子,工作额度电压允许浮动范围为5%,因此此处设计开关控制电压提升5%。

图6 延时随开关管控制电压关系示意图

由于普通NMOS传输管传输高电平、阈值损失较大、电平回复时严重影响传播速度,因此针对不同阈值管——包括普通RVT管、低阈值LVT管和超低阈值ULVT管的速度进行仿真,仿真结果如图7所示,相对于RVT管,超低阈值ULVT管的速度和温漂性能都得到了明显改善,在-55℃时,RVT、LVT和ULVT的延时分别是750 ps、400 ps和300 ps,因此此处设计采用超低阈值管作为开关传输管。

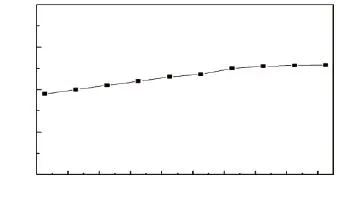

对开关控制管进行微调,对不同沟长和沟宽的开关管进行仿真,如图8所示,速度随着宽长比的增加而增加,因此可以根据版图余量选择适宜的宽长比。

对电平恢复电路进行优化,对图4中②的下拉管采用高速超低阈值管,并对功耗、速度、面积进行折衷考虑,最后得到如图9所示的性能,AB间延时为150 ps,功耗为31.01 nA,与方案设计1和优化前相比,功耗、面积和速度都得到了明显改善。

图7 延时随不同阈值开关管关系示意图

图8 延时随开关管W和L关系示意图

图9 优化后延时随温度示意图

在开关矩阵的设计优化过程中,绕线资源的设计也需重点分析,需要根据不同工艺下金属层的不同方块阻值进行布线。如五倍信号线较长,可以采用上层较厚的金属层进行布线,而短线可以采用下层金属进行布线,时钟线和长线更需采用RC更小的金属层进行走线等。

4 结束语

本文介绍了开关矩阵的架构,提出了开关矩阵的基本模型,对其进行仿真、分析和优化,结果表明优化后的模型具有很好的性能。

[1]Long Zuli,Wang Ziyun.FPGA testing technology and ATE to achieve[J].Computer Engineering and Applications, 2011,47(6):65-67.

[2]E Ahmed,J Rose.The Effect of LUT and Cluster Size on Deep-Submicron FPGA Performance and Density[J].IEEE Transactions on VLSI Systems,2000,2:3-12.

[3]Binlin Guo,Jiarong Tong.An ELUT-Based Programmable Logic Cel[J].Chinese Journal of Computers,2003,10: 26-10.

[4]Xilinx,Inc.Virtex 5 FPGA Device Handbook[P].May. 2010.

[5]Altera,Corp.Stratix 4 Device Handbook[P].Dec.2011.

[6]Jan M Rabaey,Anantha Chandrakasan.Digital Integrated Circuits A Design Perspective Second Edition[M].Oct. 2004:111-112.

Studies of FPGA Switch Matrix

HU Kai,XIE Da,LIU Tong,ZHANG Yanfei,SHAN Yueer

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

Switch matrix is one of the most important structure in FPGA devices.In the paper,the switch matrix of FPGA is analyzed in details.The placement and routing is at first introduced for switch matrix modeling.During the simulation,analysis and optimization of the model performed,the relationship between the velocity and parameters is discussed.The results show that the switch matrix is of better performance after optimization.

FPGA;switch matrix;rout;delay

TN402

A

1681-1070(2016)11-0023-04

2016-5-16

胡凯(1984—),男,江苏常州人,东南大学电子科学与技术专业本科毕业,工程师,现从事集成电路设计工作,在FPGA领域有丰富的经验。