基于ATE的电源芯片Multi-Site测试设计与实现

2016-12-06唐彩彬

唐彩彬

(中国电子科技集团公司第58研究所,江苏无锡 214035)

基于ATE的电源芯片Multi-Site测试设计与实现

唐彩彬

(中国电子科技集团公司第58研究所,江苏无锡 214035)

介绍了电源芯片的多Site测试设计与实现。基于CTA8280测试系统,通过对芯片CP(晶圆测试)要求进行分析,设计了8 Site测试电路外围,能够实现对晶圆进行8 Die并行测试。测试结果显示,该方案能够有效提升该电源芯片的测试效率,降低测试成本。

CTA8280;CP测试;Multi-Site;测试效率

1 引言

近年来,随着电子信息技术的不断发展与模拟集成电路市场的日趋扩大,电源管理芯片的应用也越来越广泛。集成电路产业主要由设计、制造、测试、封装、可靠性5部分组成,而测试是集成电路产业链中重要的一环[1]。

电源管理芯片主要应用于计算机、网络通信、消费电子和工业控制等领域。技术方面,更高的集成度、更高的功率密度、更强的耐压、耐流能力以及更高的能效等一直是电源管理类芯片的发展方向。众所周知,所有的商用化芯片最终都要依赖于ATE(Automatic Test Equipment)设备进行量产测试[2]。在芯片量产过程中,芯片的成本主要来源于流片、测试与封装,其中对Wafer(晶圆)进行CP测试(中测)显得尤为重要。因为,电源管理芯片往往需要在CP时通过trimming来将芯片定向确定做成其系列中的某一款,这也是解决相似电路节省光刻版的最佳方案。除此之外,考虑到降低封装成本,同样也需要通过CP来筛选出晶圆中的不良Die。

本文针对国内某款电源管理芯片,基于ATE、全自动探针台、专用探针卡,搭建了一套完整的晶圆测试平台。该平台实现了对晶圆的高效测试,在缩短晶圆测试时间和降低晶圆测试成本方面有显著成果。

2 测试平台搭建

2.1测试系统介绍

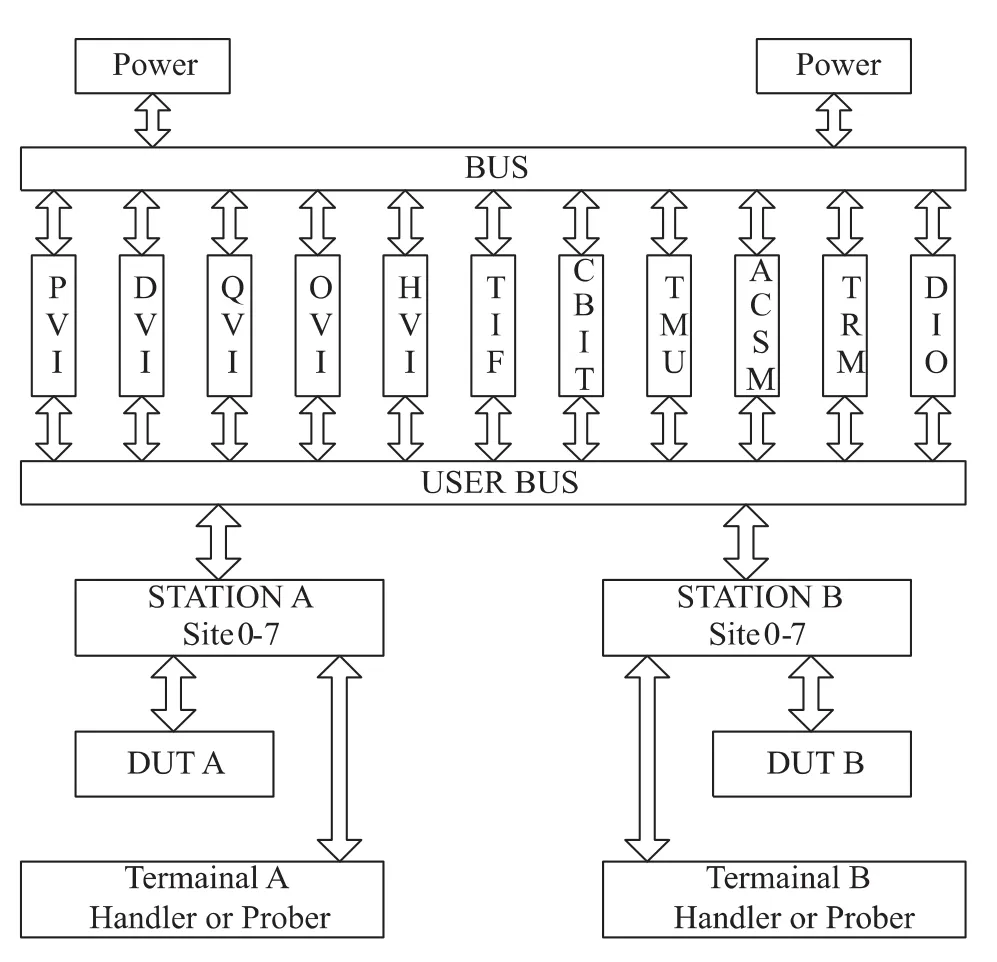

本文采用CTA8280自动测试系统进行CP测试设计,测试系统由PC机、测试主机、DUT盒、测试终端接口、GPIB接口等几部分构成,该系统是以量产测试模拟类IC产品为目标的高性能集成电路测试机,可适应于IC的芯片测试和成品测试。主要可测试运放等线性电路、功放类电路、马达驱动类电路、电源管理类电路、收音机类电路等各类模拟电路和数模类电路。

CTA8280是以测试头为基础的系统,该系统内部主要包括TIF测试接口模块、双路电压电流源DVI、大功率电压电流源PVI、四路电压电流源QVI、OVI八路电压电流源、CBIT 128路用户继电器驱动单元、TMU四路时间测量单元、DACM音频信号及AC测量单元、HKV高压测量单元、TRM修调专用模块、DIO数字测量模块等模块,系统内部结构如图1所示。CTA8280自动测试系统配有TTL和GPIB接口,可连接所有的探针台和分选机,基于C/C++环境编程,具有MAP显示及多种MAP数据保存功能。

图1 测试系统结构图

2.2总体架构设计

基于晶圆CP量产化测试要求,本文设计出一套完整的测试平台,总体设计框图如图2所示。测试站(STATION A/B)是测试机提供给用户的测试总线接口,A站和B站共享测试机的硬件资源,可按需要选择各自的测试产品进行测试。在同一个站中,需要根据被测芯片所需资源和测试机已配有的硬件资源,选择多个电路并行测试,最多可设计8 Site并测。通过对测试机DUT的设计,并通过排线将该测试需要用的资源引到探针卡上。在探针卡上设计芯片测试外围,最终通过探针将电流电压等信号加到每一个待测Die的Pad上。实际的自动并行测试还需要有探针台的配合,同样需要对探针台做相应的设置[3]。

图2 测试平台结构图

2.3探针卡及DUT设计

在绘制DUT及探针卡PCB的过程中,需先对各个电路模块及器件进行合理的布局。布局的总原则是尽可能将元器件按照同一方向排列,选择PCB进入熔锡系统的方向以避免焊接不良;调整元器件位置,使得射频路径长度最小,并使输入尽可能远离输出;为了保证焊接(熔锡)的可操作性元器件最少要保持0.5 mm的间距;对于双面板,应一面放置表贴元件,一面放置过孔元件。设计中需要注意的主要事项有:

(1)根据探针台的实际情况定义探针卡的长度及宽度(本文设计203 mm×114 mm的矩形)。

(2)设计探针卡PCB时在卡中间需预留洞孔(本文设计6 mm半径圆)以方便后期探针制作和探针台对针清针操作。

(3)探针卡上空间有限,本文为了实现8 Site高效测试,将芯片的熔丝修调模块放置在测试机DUT上。

(4)对于芯片中易受干扰的测试Pad,在不加电时需通过继电器与测试机电源彻底断开。

(5)布局布线时由于排列紧凑,遇到大体积的元器件需考虑相互间的配合问题,并且需要控制线的粗细与间距。

在探针卡PCB板制作完成后,需要根据圆片的Pad位置、芯片面积大小、划片槽宽度等信息选择8 Site的排列方式并制作探针。

3 8 Site测试实现

3.18 Site并行测试电路结构

对电源芯片晶圆进行测试需要设计相应的外围电路,将测试机的资源加载到待测管芯的相应Pad上。根据ATE测试系统和外围设计要求来分配测试机资源,需要综合考虑测试方案对ATE测试资源的能力与精度等方面的要求。在测试机资源能满足的基础上,尽量进行多Site测试,使测试机的资源利用最大化。

本文采用8 Site设计方案,Site1测试外围电路如图3所示,Site2~Site8测试外围结构与Site1相同,将测 试机 资 源 分 配 成 DVI0~DVI7、QVI0~QVI7、OVI0~OVI7、OVI8~OVI15、TMU0~TMU7并分别对应每一个Site。该芯片除了熔丝Pad外主要有T0、T11、T15、VDD、DRAIN、CS和GND管脚,其中考虑到芯片测试过程中GND管脚可能会有大电流流过,对GND采取制作双针。该测试方案单Site总计需要使用5路电流电压源和1路时间测试源,由于本文系统只配备了32路电流电压源,所以设计中T11与T15管脚通过继电器K18对OVI8~OVI15电流电压源进行复用。设计中使用双刀双掷继电器,这样2个Site可以共用1个继电器,并且使用同样的控制位,实现了对已有资源的最大利用。

图3 测试外围电路设计图

3.2具体测试电路的设计

电源芯片测试大体上可以概括为直流参数(DC)测试、交流参数(AC)测试和功能测试3个方面。DC测试是一系列测试的统称,其中包括开短路测试、漏电流测试、静态/动态功耗电流测试、静态电流测试、高阻态漏电流测试等;交流参数又称AC参数,AC参数测试的目的是保证制造或设计出来的芯片符合它所有的时序规格;功能测试通常用来验证被设计或被制造出来的芯片是否能够正常执行它被赋予的逻辑功能。本文针对该电源芯片主要做了如下几项测试。

3.2.1开短路测试

开短路测试 (Open/Short Test)又称为Continuity Test或Contact Test,这项测试用来检查芯片的信号管脚电气特性上是否连接正常,有没有发生信号管脚之间短路或者信号管脚和电源或地短路的情况。由于条件限制,本文只对VDD、T11、T15、DRAIN做了开短路测试,通过这些管脚拉100 μA电流测电压的方式来验证这些管脚是否出现开短路,K23继电器需要进行动作以切除电容的影响。开短路测试耗时短,为了节省芯片的测试时间,将开短路测试项放在前面测试是测试过程中通常的做法。

3.2.2VDD开启电压测试

本文通过检测DRAIN脚的电平来测试VDD开启电压,开启电压的测试外围电路如图4所示。通过对VDD管脚进行电压扫描的方式进行测试,VDD由0 V上升为5.1 V,此时DRAIN端为高电平(约5 V),以200 mV的步进增加VDD值,直到DRAIN端电压变为低电平,记录此时VDD的值,即为芯片VDD开启电压值。根据VDD_ON测试值来烧T8、T9两段熔丝对VDD开启电压进行调节(T8、T9为PAD与GND之间的熔丝),烧完熔丝再做一次开启电压测试以确保芯片开启电压的一致性。

图4 VDD开启电压测试

3.2.3Vref(CS检测参考电压)测试

该测试项的测试电流原理如图5所示。VDD加5 V电压供电,对T11脚加-0.3 V电压,对K25继电器进行动作使CS连接到地。为了排除时间测试源的影响,TMU资源需连接到K24继电器的常开端。测试T15端电压值,并通过烧写熔丝将其调整至400 mV。这项测试需要对T10、T1、T2、T3、T4这几段熔丝进行烧写,需要分两次进行Trim,先根据Vref测试初值Vref_bef选择对T4、T10两段熔丝烧写,Trim后再根据Vref_af值选择对T1、T2、T3三段熔丝的Trim方式,最终测试判断第二次Trim后Vref_af2是否在规范的388~412 mV以内。

图5 Vref测试电路

3.2.4Tdem_max(最大退磁保护时间)与Ton_max(最大导通时间)测试

Tdem_max与Ton_max两项的测试电路图相同,如图6所示。VDD接1 μF电容到GND,T0=VDD,CS=0 V,DRAIN端通过1 kΩ电阻接20 V。此时,DRAIN端会周期性地出现脉冲信号,测试该脉冲的高电平时间,即最大退磁保护时间,测试脉冲波形的低电平时间,即为最大导通时间。需要注意的是在这两项测试中要分别进行熔丝烧写,通过烧写T5、T6、T7来调节最大退磁保护时间,烧写T12、T13、T14来调节最大导通时间。

图6 Tdem_max与Ton_max测试

3.2.5IDD(静态电流)测试

静态电流测试电路如图7所示,测试条件为VDD=6.5 V,CS=0 V,GND=0 V,其他端口悬空,测试VDD端电流。

图7 IDD(静态电流)测试

3.2.6Ijfet(高压启动电流)测试

高压启动电流测试电路如图8所示,测试条件为VDD由0 V上升到5 V,DRAIN通过1 kΩ电阻接40 V电压源,测试此时DRAIN端的输入电流。其中,QVI与OVI源理论上最大只能加到20 V电压,而DVI最大能达到50V,所以设计中在DRAIN端使用DVI源。

图8 Ijfet(高压启动电流)测试

3.3测试程序的调试与优化

完成所有测试项的程序开发和参数设置后,按照顺序先依次调试各个测试项,待每个测试项都调试通过后再进行综合调试。综合调试通过后对程序进行优化。程序优化的原则是尽量减少测试时间,主要是去除不必要的等待时间或在不影响测试结果的情况下尽量缩短等待时间和一些冗余的程序。

4 测试结果

通过对某电源芯片测试电路进行设计,实现了对该晶圆的8 Site并行测试。测试完成后,对测试数据进行分析,做出8个Site某关键参数测试值分布图(如图9所示),该项测试值呈现理想的正态分布情况。

图9 关键参数测试值分布

该电源芯片晶圆为8寸片,总管芯数26 000颗左右。8 Site测试时间650 ms左右,单片测试时间在62 min以内;而单Site测试时间500 ms左右,单片测试时间在7 h左右。可见,8 Site并测设计大大缩短了圆片测试时间,有效提升了测试效率。8 Site并测map如图10所示,测试良率在99%左右。

图10 8 Site并测Map图

5 结语

晶圆测试受到利润的影响,对高效测试的要求越来越高。本文针对某款电源芯片的测试要求,合理利用测试系统资源,实现了对wafer的高效测试,在提高晶圆测试效率、降低晶圆测试成本方面有很好的功效。

[1]Geng L,Chen Z M,Zhao M L.A novel regulation technique and its application to design SC DC-DC converters[J]. Chinese Journal of Semiconductor,2004,25(04).

[2]刘新光.后端设备面临更多挑战,高性价比ATE聚焦中国[J].电子产品世界,2004(06B),100-103.

[3]蒋和全.模拟集成电路测试平台建设[J].微电子学,2004, 34(4):363-365.

A Design and Implementation Scheme of Multi-Site Test for ATE-based Power Chip

TANG Caibin

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

The paper introduces a design and implementation of Multi-Site test for power chip.By analyzing the CTA8280 test system and CP(wafer test)requirements,the 8 Site test peripheral circuit is designed for 8 Die parallel test.The results show that the proposed scheme effectively improves the test efficiency and reduce the cost.

CTA8280;CP test;Multi-Site;test efficiency

TN407

A

1681-1070(2016)11-0014-04

2016-6-7

唐彩彬(1990—),男,江苏泰州人,硕士研究生,毕业于江南大学集成电路工程专业,现在中国电子科技集团公司第58研究所从事集成电路测试研发工作。