PCB板内阻抗测试需求与技术

2015-10-24许丽芬

蔡 林 许丽芬

(广东正业科技股份有限公司,广东 东莞 523808)

PCB板内阻抗测试需求与技术

蔡 林 许丽芬

(广东正业科技股份有限公司,广东 东莞 523808)

文章介绍了当前PCB板内阻抗测试需求的原因和趋势,同时对其测试技术进行讲解和普及,可提高PCB企业了解板内阻抗测试技术和发展趋势,为解决阻抗板在生产与测试中存在的问题做理论和技术支持。

板内阻抗;差分阻抗;阻抗测试

1 前言

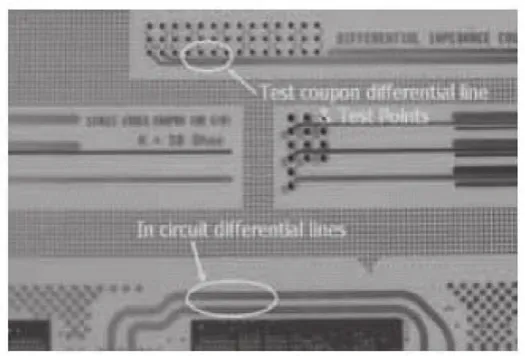

PCB板内阻抗指成品板内迹线的真实阻抗(图1),与传统的附连板(附连板)阻抗条不是一个概念。由于板内阻抗线与附连板阻抗线存在走线间距、走线宽度、走线所处环境、走线所处位置以及设计误差等都会导致板内真实阻抗与附连板阻抗存在差异。然而随着当前线路板朝高密度、高多层、小体积的方向发展,客户对阻抗控制要求越来越严格,控制精度要求也越来越高。这种板内阻抗与附连板阻抗存在的偏差可能会使高端客户难以接受,因此越来越多的客户要求PCB厂家提供真实的板内阻抗。

图1 板内阻抗与附连板示意图

2 板内阻抗与附连板存在的差异与问题

2.1 板内阻抗线与附连板走线物理上的差别

从图2举例PCB我们可以看到附连板与真实板内阻抗线之间的差别。

图2 板内阻抗与附连板

(1)虽然走线间距、走线宽度是一致的,但是附连板测试点的间距固定为2.54 mm(为满足测试探针间距),而板内真实走线的末端(即印制插头)间距是可变的,随着QFP、PLCC、BGA封装的出现,一些芯片的引脚间距都远小于2.54 mm(即附连板测试点的间距)间距。

(2)附连板走线是理想的直线,而板内真实走线往往是弯曲的、多样的。PCB设计人员和生产人员很容易将附连板的走线理想化,但是PCB上的真实走线则会因为各种各样的因素导致走线不规则化。

(3)附连板和板内真实走线在整个PCB上的位置不同。附连板都位于PCB板中间或边沿,在PCB出厂时往往会被生产商去掉。而板内真实走线的位置则是多样的,有的在靠近板子的边沿,有的位于板子的中央等。

(4)板内阻抗走线周围一般分布着过孔、焊盘、屏蔽层等,而附连板走线周围环境都比较单一。

由此可见,板内阻抗线与附连板走线存在着差异,其差异也带来了阻抗测试值的差异。

2.2 阻抗测试值的影响

(1)附连板测试点间距附连板走线的间距不同,会导致测试点与走线之间带来阻抗不连续。而PCB板内的真实差分走线末端(即芯片的引脚)间距往往是与走线间距相等或者非常相近的。由此会带来阻抗测试结果的不同。

(2)弯曲的走线与理想的走线所反映出来的阻抗变化是不一致的。在走线弯曲转折的地方特征阻抗往往是不连续的,而附连板的理想化走线则不能反映由于走线弯曲所带来的阻抗不连续现象。

(3)附连板与真实的走线在PCB上的位置不同。目前的PCB都采用多层走线的设计,在生产时需要经过压制。当PCB压制时,板子不同的位置所受到的压力不可能做到一致,不同位置的介质层厚度有差异,这样制成的PCB在不同的位置上介电常数往往不相同,特征阻抗也当然不同。

(4)板内阻抗受其周围的过孔、焊盘、屏蔽层等影响反映出来的阻抗是不连续的,而附连板因走线环境单一,不能反映阻抗真实变化情况。

可见附连板反映的阻抗值是不能完全反映PCB板内真实走线的真实特征阻抗的。

2.3 测试对比

2.3.1 测试环境

测试环境温度:23 ℃;湿度:55%RH;测试板(中间板内阻抗线、边缘附连板阻抗线)

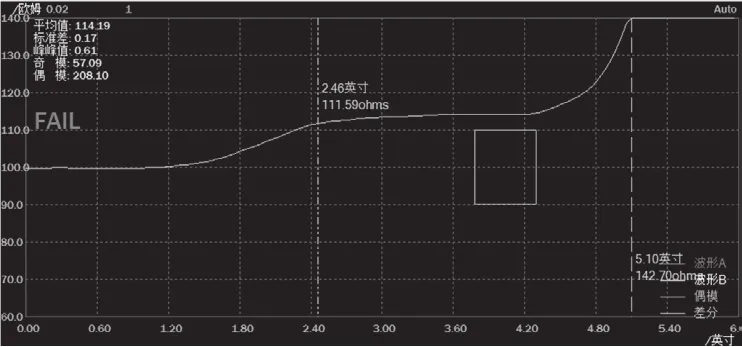

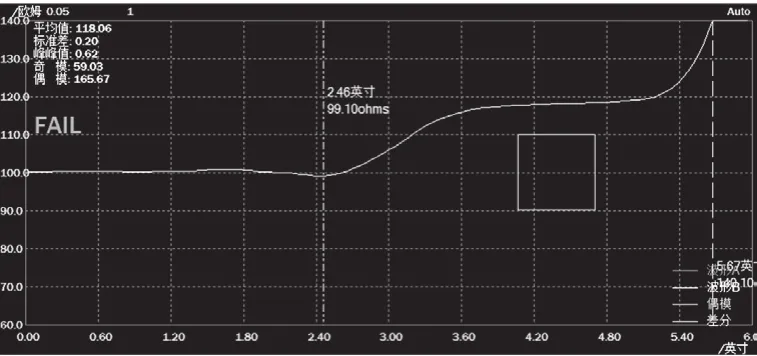

2.3.2 测试波形对比(图3、图4)

图3 附连板测试波形

图4 板内测试波形

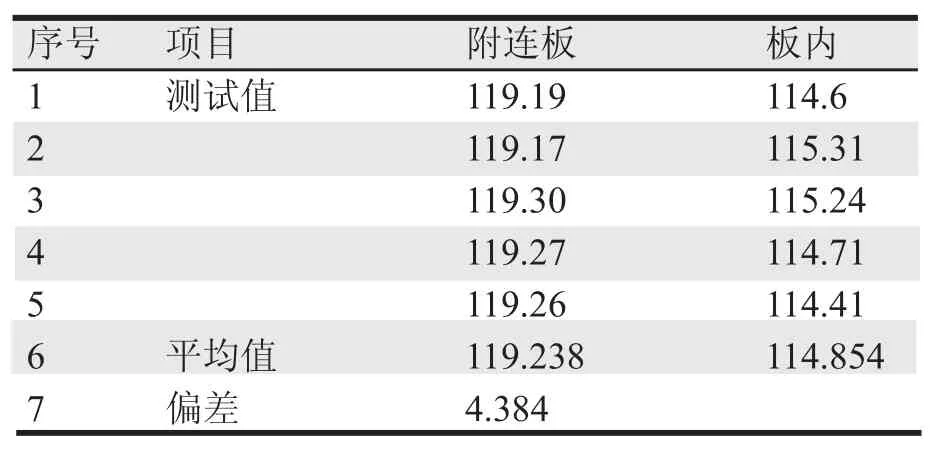

2.3.3 测试数据对比(表1)

表1 附连板与板内阻抗测试数值对比

从图4、图5以及表1数据来看,板内阻抗与附连板阻抗波形虽然差异不大,但测试数值却存在偏差,偏差数值的大小与测试板的不同而不同。

3 板内阻抗测试需求与阻碍

3.1 板内阻抗测试需求

(1)随着当前线路板朝高密度、高多层、小体积的方向发展,客户对阻抗控制要求越来越严格,控制精度要求也越来越高,例如精度要求小于± 5%。板内阻抗与附连板阻抗存在的偏差可能会超出控制精度要求,而且控制精度要求越高,采用附连板评估阻抗的风险就越大。

(2)无论是PCB的生产商还是高速电路设计者、制造者都希望能对PCB板内的真实高速差分走线直接进行TDR测试,获得最准确的特征阻抗信息。

3.2 板内阻抗测试的阻碍

阻碍板内阻抗测试的主要原因有以下两个:

(1)难以找到差分TDR探头的接地点,高速PCB设计人员不会在设计高速差分走线时在走线的末端(即芯片引脚)附近放置固定间距的接地点。

(2)差分走线的末端(即芯片的引脚或金手指或焊盘)间距是多变的,必需要一个间距可调的差分探头来实现探测。

4 板内阻抗测试技术

4.1 TDR的基本原理

阶跃脉冲发生器发出一个快上升沿的阶跃脉冲。同时接收模块采集反射信号的时域波形。如果被测件的阻抗是连续的,则信号没有反射,如果有阻抗的变化,就会有信号反射回来。根据反射回波的时间可以判断阻抗不连续点距接收端的距离, 根据反射回来的幅度可以判断相应点的阻抗变化。

图5 TDR原理示意图

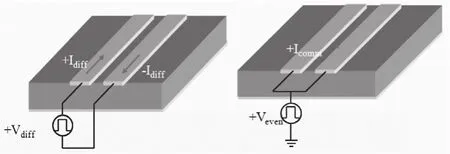

4.2 常用阻抗模型(图6、图7)

图6 奇模和偶模阻抗

图7 差分和共模阻抗

对于比较常见的差分阻抗来说,测试中只需要2个幅度相同、方向相反的阶跃信号即可,不需要接地,其采用的是虚拟接地,支持这种板内差分阻抗测试的阻抗机型有泰克、安捷伦和爱思达。其它类型阻抗必须接地。

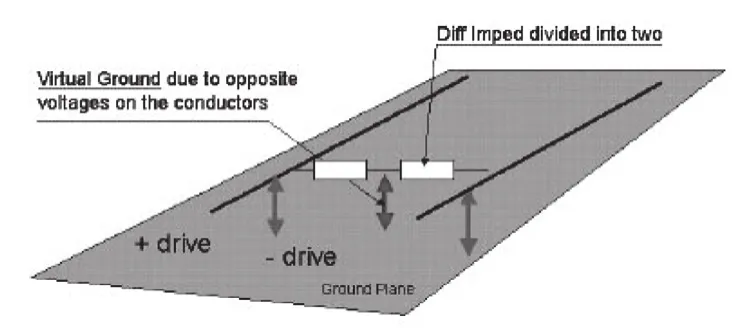

4.3 虚拟地的原理(图8)

由于差分走线和差分信号是平衡的,差分信号的中心电压点和地平面是等电势的,因此在使用差分阶跃信号进行差分TDR测试时,只要保证探针A和探针B共地,即无需与DUT之间接地。

图8 虚拟地原理

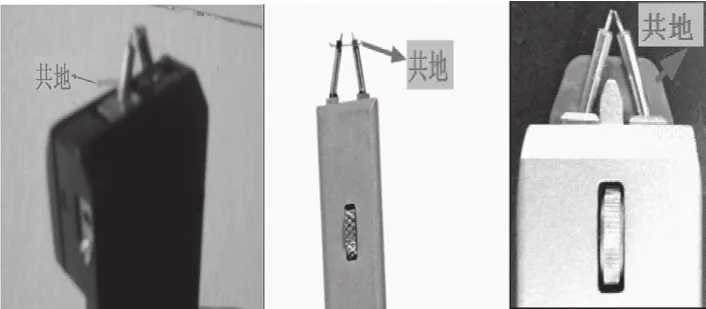

需要注意的是:探针A和探针B必须要共地,如图9是可调探头的共地图。

图9 泰克、安捷伦、爱思达可调共地探头

由图7可知,探针A和探针B需要完好共地,如果共地不良或共地连接线断掉都不能进行测试,测试前必须认真检查共地是否良好。

4.3 板内阻抗测试注意事项

(1)所选用的特性阻抗测试仪必须支持板内阻抗测试功能。

(2)需配备可调探头,可调间距一般要求在0.5 mm ~3 mm之间,可满足不同测试点的需求。

(3)差分测试前必须检测信号针是否良好共地。

(4)间距过小的测试过程中探针与测试点必须稳定接触。

5 总结

通过以上论述和测试对比,结论概括如下:

(1)附连板与板内阻抗测试值存在偏差,这种偏差主要由阻抗线的走线环境、位置、工艺有关。

(2)板内差分阻抗测试采用虚拟地原理,有效避免了测试中寻找接地点,2个信号针就可以完成差分阻抗测试。

[1]IPC-TM-650 阻抗测试标准及方法

蔡林,时域反射(TDR)技术总工,主要负责特性阻抗测试仪产品的研发工作。

PCB internal impedance test requirements and technology

CAI Lin XU Li-fen

This paper introduces the reason and trend of the current PCB internal impedance test requirement. At the same time, this paper carries on the explanation and popularization of the test impedance technology, which can help the PCB enterprises to solve the production and testing of impedance board problem existed.

PCB Internal Impedance; Differential Impedance; Impedance Test

TN41

A

1009-0096(2015)11-0048-03