一个帧可控通用LCD 驱动电路的设计

2023-08-03朱培敏兰亚峰

朱培敏,兰亚峰

(中国电子科技集团公司第五十八研究所,江苏 无锡 214035)

1 引言

液晶显示(LCD)技术出现于20 世纪70 年代,其凭借工作电压低、工作寿命长、功率损耗小、集成方便、电磁辐射低、显示信息量大等优良特性,被广泛应用在显示仪器中[1]。近年来,随着物联网技术向低功耗、低成本方向的快速发展,功耗低的LCD 模块在产品设计、科研生产等领域中发挥的作用也越来越大,受到众多学者的关注[2-3]。LCD 屏有单色和彩色2 种[4-5],与彩色相比,单色屏有成本与功耗更低等特点,更适合应用在一些特定的领域,如单纯数字、图标、文本、字符显示等。本文提出的LCD 驱动电路主要针对低功耗应用场景而开发,其成本低、功能强,更适合日常生活场所。本电路采用平均电压法来消除交叉效应[6],采用电阻分压法以及频率与死区的选择实现功耗与性能的最优解。

2 LCD 驱动电路

本文提出的LCD 驱动电路的数据输入基于APB协议,LCD 驱动器结构如图1 所示,主要包括地址和数据总线、频率发生器、电压发生器电路、对比度控制电路等。

图1 LCD 驱动器结构

SEG31~SEG0 是列输出口,COM7~COM0 是行输出口,LCDCLK 是MCU 提供的系统时钟,COM[7:4]、SEG[31:28]、SEG[15:12]是复用端口,可提供多种驱动方案以供选择:

1/8 占空比-1/4 偏置,最大点阵:8×27=216;

1/4 占空比-1/4 偏置,最大点阵:4×32=128;

1/3 占空比-1/4 偏置,最大点阵:3×32=96;

1/2 占空比-1/4 偏置,最大点阵:2×32=64。

2.1 频率发生器

降低动态功耗的重要途径之一是降低工作频率,在保证显示屏有足够刷新率的前提下使LCD 模块工作在低频率下,动态功率消耗自然就下降了。

根据视觉暂留原理[7],当帧频达到12 帧/s 时,LCD 屏幕点亮的像素可被视为连贯显示。MCU 内置的低速外部RC(LSE)与低速内部RC(LSI)提供的频率为32 kHz,为了使频率自由调节,本模块使用PS 位与DIV 位来分频系统时钟。

PS 为粗分频,可实现0~32 768 分频,分频后得到的粗分频时钟频率fCK_PS=fLCDCLK/2p;DIV 位用来再次分频fCK_PS,为细分频,可实现16~31 分频,分频后得到的细分频时钟频率fCK_DIV=fCK_PS/(16+D)。因此,通过PS 位粗调频率,再通过DIV 线性细调频率,最后频率发生器输出给整个系统的时钟频率fCK_DIV可表示为

其中,p 代表PS 调节位,D 代表DIV 调节位,fLCDCLK是MCU 为该模块提供的时钟频率。由式(1)可知,系统时钟频率可调跨度大且精细,在满足LCD 屏幕像素显示不发生闪烁的前提下,可最大限度降低功耗。

PS 位与DIV 位的存在使得可供给LCD 模块正常工作的时钟频率fCK_DIV非常多。考虑到功耗和刷新速率,本设计的帧频率可工作在30~100 Hz。

2.2 平均电压法驱动行与列

在液晶显示中为了避免电泳现象出现,一般采用交流驱动信号。目前比较被业内认可的有行反转、列反转、像素反转以及帧反转等技术[8]。由于帧反转具有功耗低,适合单色小屏幕等特性,本设计采用帧反转技术。帧反转在LCD 像素点激活的一个周期由一个奇数帧与偶数帧组成,偶数帧是奇数帧的倒相,奇数帧与偶数帧如图2 所示。VLCD为LCD 模块的输入电压,本设计中当一个像素点被点亮时,奇数帧行端口的偏置电压为VLCD,列端口的偏置电压为VSS,即像素点2端电压最大时,该像素点被激活。与被激活像素点处于同一行或者列的像素点称为半选择点,不处于同一行或者列的点称为非选择点。如果半选择点的偏置电压处于液晶的阈值电压附近,屏幕上会出现半显示现象。为了避免半选择点出现半显示现象,本驱动采用平均电压法驱动行与列[6]。将驱动电压分为若干档,假设档次为a,平均电压法会使未激活像素点电压为(±1/a)VLCD或(±2/a)VLCD,远小于VLCD。其本质是将半选择点的电压与非选择点的电压之差平均化,在提高选择点显示对比度的同时,又使半选择点与非选择点的显示更均匀、一致。

图2 奇数帧与偶数帧

2.3 电压发生器电路

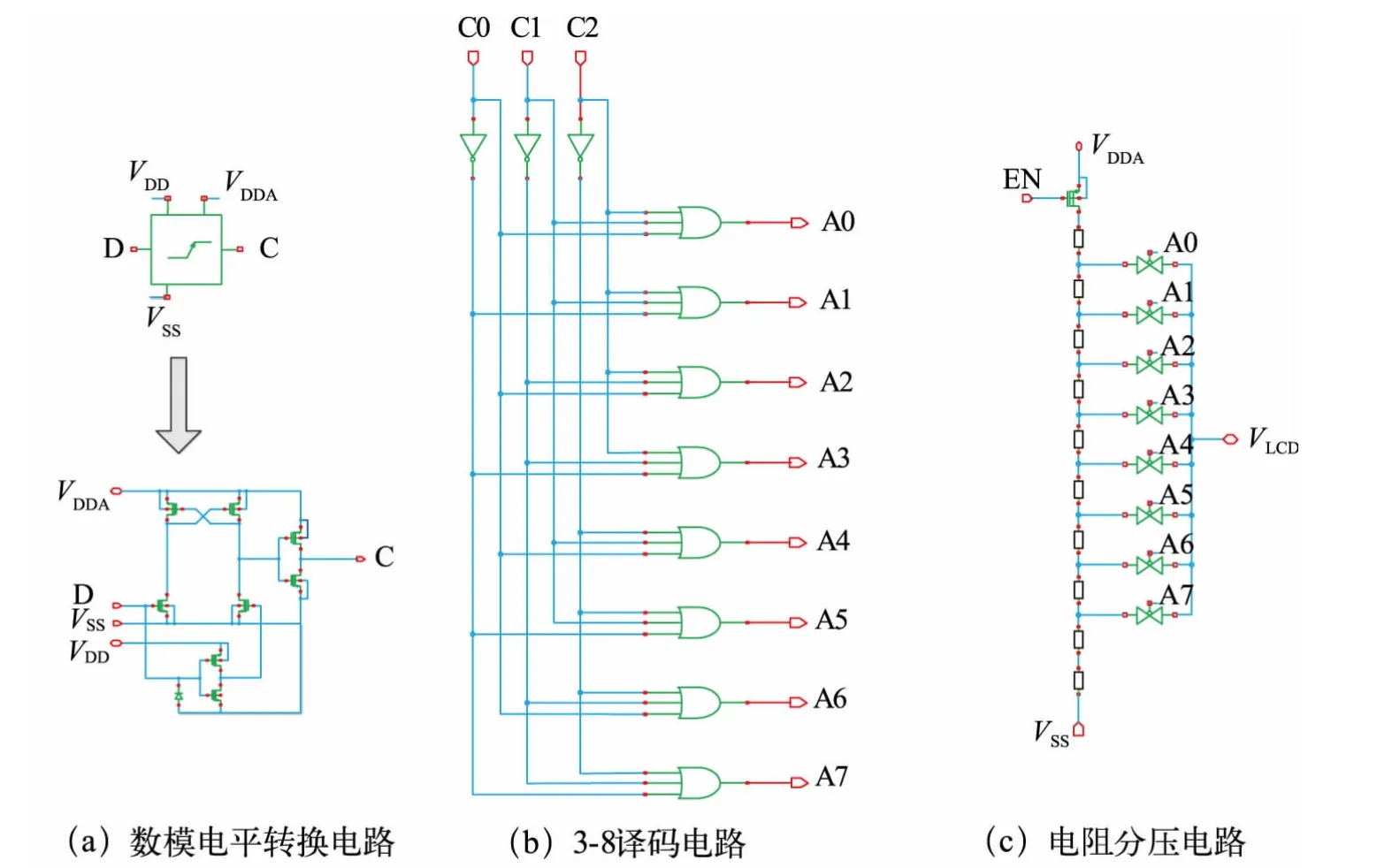

电压发生器电路如图3 所示,各电压的输出依靠电阻分压电路实现。图3 中,“!”表示电压通过一个反向器,其功能与初始作用相反。EN 为使能位,EN 为高时,开启电路。HD 为高驱动位选择开关,可使电路在低功耗与高性能间切换。当HD 有效时,左边低通网络有效,为电路提供高驱动;当HD 无效时,右边高阻网络有效,为电路提供低功耗。

图3 电压发生器电路

根据电阻阻值的不同,再配合档次选择开关A、B、C,使电路能输出2、3、4 档。当选择开关C 有效时,在Vout2 上输出1/2 VLCD;当B 有效且C 无效时,在Vout2 上输出2/3 VLCD,在Vout3 上输出1/3 VLCD;当A与C 均有效时,在Vout1、Vout2、Vout3 上分别输出3/4 VLCD、2/4 VLCD和1/4 VLCD,并提供给输出引脚。

2.4 对比度调整电路

对比度调整电路如图4 所示。串行输入控制数据通过一个数模电平转换器将数字电压VDD转换成模拟电压VDDA,再通过一个3-8 译码器来选择电阻分压电路电压的输出,使其在VLCDmin和VLCDmax之间变化,从而达到对比度控制。

图4 对比度调整电路

3 数据输入控制

本文采用APB 总线负责寻址以及控制数据与显示数据的输入,在显示数据上,使用双缓冲存储器来保证显示数据的连贯性,第一级缓存用来存储APB 总线上的列显示数据RAMx,当请求更新开关UDR 置1时,列显示数据会从第一级缓存输入到第二级缓存。在此期间,第一级缓存中的数据被写保护,更新完成后,UDR 数值清零,之后才能通过APB 总线修改第一级缓存中的数据。当UDR 不开启时,即使通过APB总线修改了第一级缓存数据,列端口依旧输出第二级缓存寄存器的值。

3.1 数据对引脚电压的控制

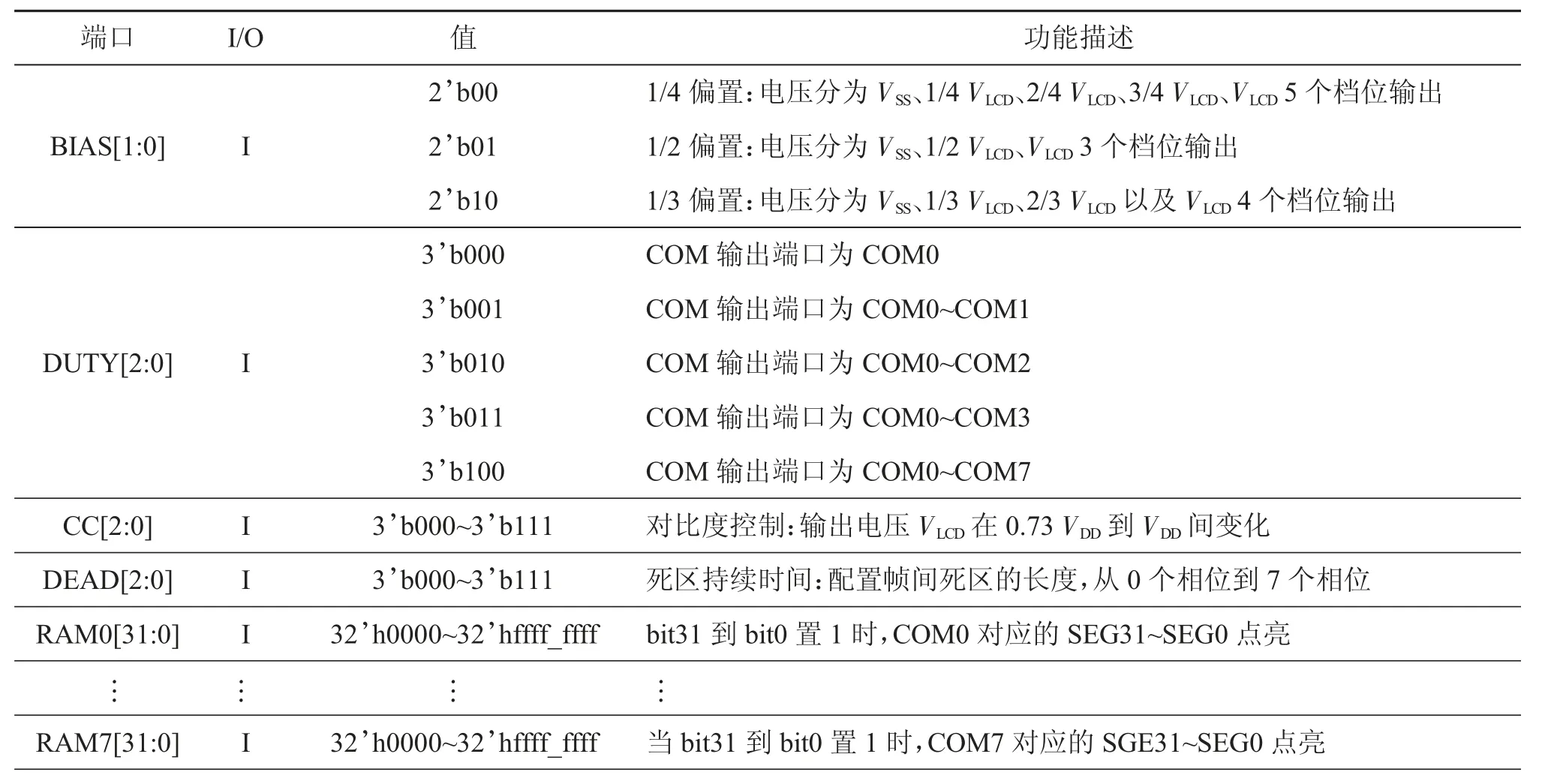

数据对输出引脚的控制如表1 所示。BIAS[1:0]控制输出偏置;DUTY[2:0]控制占空比,即控制行端口数;RAM0[31:0]~RAM7[31:0]控制列端口;CC[2:0]与DEAD[2:0]控制对比度。为实现2.2 节平均电压法驱动的行与列,行输出用COM[2:0]表示,列输出用SEG[1:0]表示。

表1 端口功能描述

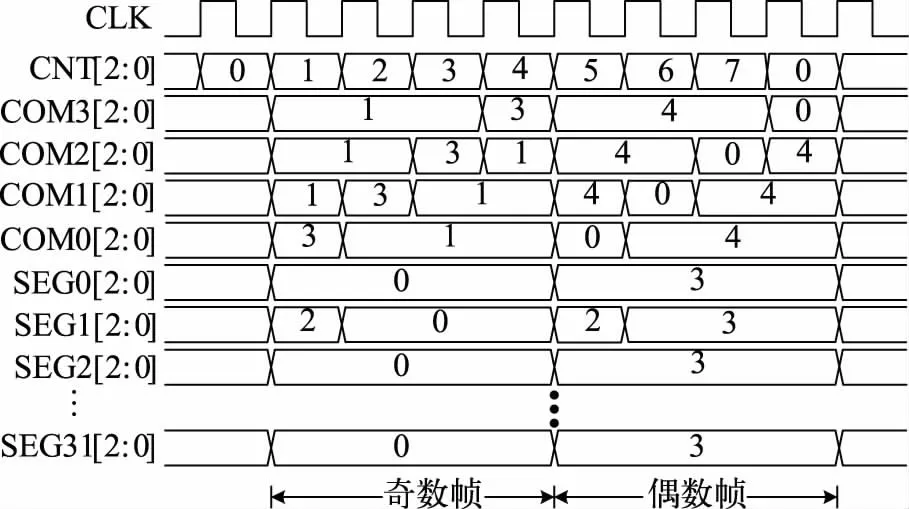

当选择1/4 偏置与1/4 占空比时,BIAS 为2’b00,DUTY 为3’b011,行输出端口为COM0~COM3,列输出端口为SEG27~SEG0。当RAM0 为32’hffff_fffd、RAM1~RAM3 为32’hffff_ffff 时,1/4 偏置、1/4 占空比下COM 与SEG 的输出如图5 所示。

图5 1/4 偏置、1/4 占空比下COM 与SEG 的输出

计数器循环从0 计数到7,0~3 为奇数帧前控制信号,4~7 为偶数帧前控制信号。在奇数帧期间,当CNT为0 时,下一个时钟周期里行只有COM0 有效,为VLCD,其余COM1~COM3 为1/4 VLCD。依次类推,CNT为1 对 应COM1 为VLCD,CNT 为2 对 应COM2 为VLCD,CNT 为3 对应COM3 为VLCD,而在此期间的其余COM 都为1/4 VLCD。在偶数帧期间,当CNT 为4,下一个时钟周期里行COM0 为VSS,其余COM1~COM3 为3/4 VLCD。依 次 类 推,CNT 为5 对 应COM1 为VSS,CNT6 对应COM2 为VSS,CNT7 对应COM3 为VSS,而在此期间的其余COM 都为3/4 VLCD。

而SEG27~SEG0 由RAMx[27:0]的bit 位控制,即RAMx 与COMx 是对应的,因此,配置RAMx 的数值可控制对应COMx 下的SEG 输出是开启还是关闭。如RAM0[0]置1,则COM0 对应的SEG0 在奇数帧时为VSS,在偶数帧时为VLCD,从而使得COM0-SEG0在COM0 对应的位置上处于最大电压,点亮像素点。RAM0[1]置0,则COM0 对应的SEG1 在奇数帧时为2/4 VLCD,在偶数帧时为2/4 VLCD,该像素点不点亮。

1/3 偏置与1/3 占空比以及1/2 偏置与1/2 占空比下COM 与SEG 的输出如图6、7 所示,由循环的计数器来划分奇数帧与偶数帧。在奇数帧下,COMn 激活时处于VLC(Dn 为计数器CNT 的数值),未激活时处于1/3 VLCD(1/3 偏置),1/2 VLCD(1/2 偏置),而SEGn 激活时处于VSS,如SEG0 未激活时处于2/3 VLCD(1/3 偏置),VLC(D1/2 偏置),如COM0 激活时对应SEG1。在偶数帧下,COMn 与SEGn 的电压为VLCD减去奇数帧下的有效电压。

图6 1/3 偏置、1/3 占空比下COM 与SEG 的输出

图7 1/2 偏置、1/2 占空比下COM 与SEG 的输出

3.2 死区对对比度的调节

对比度除了通过CC[2:0]控制外,也可以在偶数帧之后插入一个由DEAD [2:0]控制的死区来调节对比度,当DEAD[2:0]有效时,CNTx 计数值的归零点由其原本的值加上DEAD[2:0]控制的周期时间,DEAD 为2,1/3 偏置、1/3 占空比下COM 与SEG 的输出如图8所示。

图8 DEAD 为2,1/3 偏置、1/3 占空比下COM 与SEG 的输出

当DEAD[2:0]为2 时,CNTx 在原本计数周期后增加了2 个周期,在这2 个周期内,COM 与SEG 都置为VSS,实现无需修改帧速率即可降低对比度与功耗。

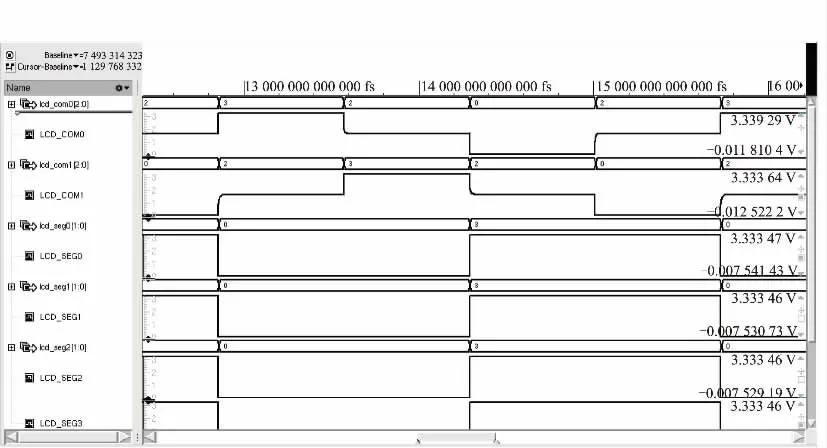

4 整体仿真

该模块的输出行与列端口众多,存在多种组合方式,在系统仿真过程中对众多组合进行一一仿真,记录了大量相关波形,1/2 偏置与1/2 占空比、1/3 偏置与1/3 占空比以及1/4 偏置与1/4 占空比的仿真波形分别如图9~11 所示。在1/2 偏置与1/2 占空比下,COMx 在奇数帧激活时为VLCD,未激活时为1/2 VLCD,在偶数帧激活时为VSS,未激活时为1/2 VLCD;在1/3 偏置与1/3 占空比下,COMx 在奇数帧激活时为VLCD,未激活时为1/3 VLCD,在偶数帧激活时为VSS,未激活时为2/3 VLCD;在1/4 偏置与1/4 占空比下,COMx 在奇数帧激活时为VLCD,未激活时为1/4 VLCD,在偶数帧激活时为VSS,未激活时为3/4 VLCD,均符合设计需求。

图9 1/2 偏置、1/2 占空比仿真波形

图10 1/3 偏置、1/3 占空比仿真波形

图11 1/4 偏置、1/4 占空比仿真波形

5 结论

本文提出了一种高度灵活、帧速率可控的LCD 驱动电路的设计方案,电压发生器的使用使模块在功耗与性能间自由切换。在偶数帧后插入可调死区,可更精准地调节对比度和功耗。此外,在平均电压法下,多种偏置条件的调用为用户提供大量适用于不同状况的可选偏置。最后,灵活的COM 和SEG 引脚配置为用户提供了最适宜自己的驱动方案。