基于FPGA的片上系统设计研究

2021-08-18杨翠娥

杨翠娥

(太原工业学院,山西 太原 030008)

0 引言

FPGA是一种超大规模可编程逻辑器件。通过EDA软件设计平台,采用符合业界标准的HDL语言对FPGA芯片进行设计开发,使得电子工程师逐步从使用硬件转向设计硬件,把想设计的电路直接设计在自己的专用芯片上,使设计者通过设计芯片实现电子系统功能。近年来越来越多的IP核的出现,尤其是IP CPU核的使用,使得FPGA设计更加集成、快捷与高效。相对于简单的单片机系统,基于FPGA的SOC系统由于集成度高,具有良好的抗干扰性能,同时也使信号传输的速度大幅提高。以Intel的Cyclone 4E为例,其单片机核的工作频率最高可超过200MHz,远远高于一般的单片机的工作速度。另外,FPGA系统升级便捷,开发效率高,低成本及低功耗的特点也使得基于FPGA的SOC应用越来越得到业界的认可,成为现代电子工程师进行产品设计的重要手段[1]。

1 FPGA片上系统基本组成

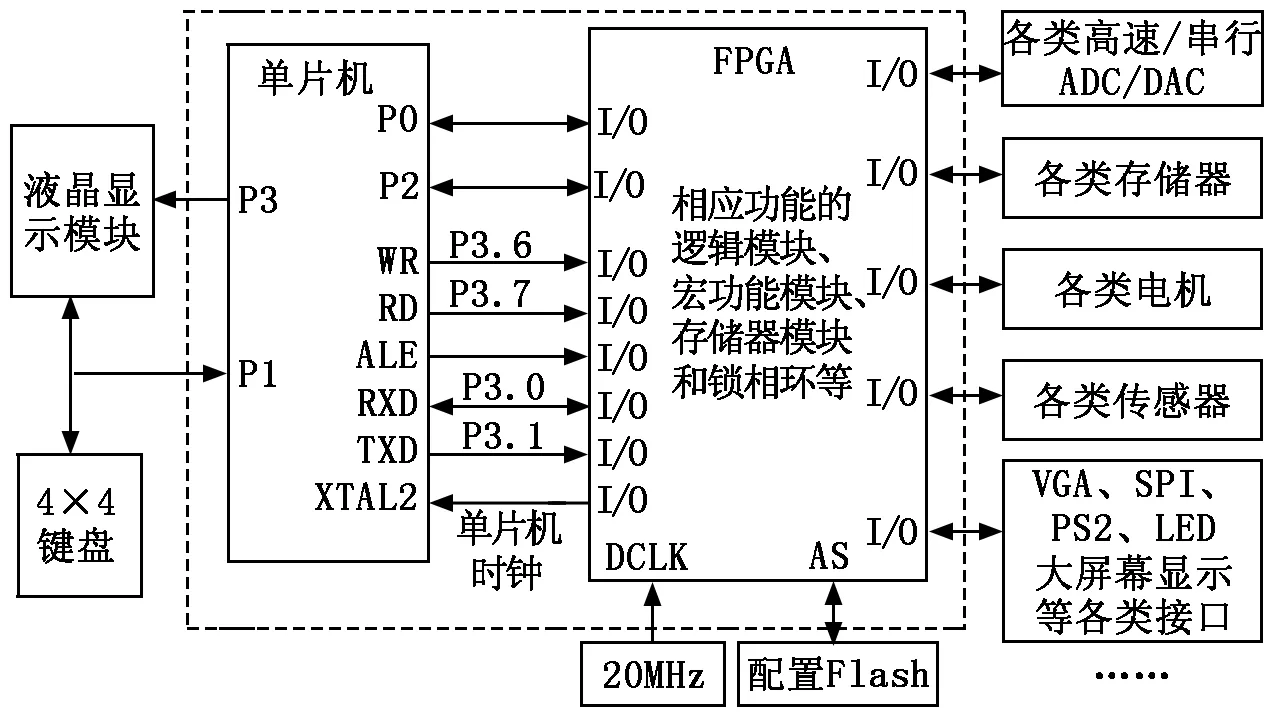

图1所示为基于FPGA的SOC系统组成框图。虚线框内部分可以组成一个单片机系统且可以集成在一片FPGA芯片中,构成FPGA片上系统(SOC)。片上系统是一个软硬件相结合的可综合系统模块,其中单片机部分一般是一个开源的软核处理器,然后在FPGA上设计或定制相应功能的逻辑模块,其中包括所有必须的存储器,控制模块、通信模块和接口模块等。片上系统可以和外围输入、输出接口相连接,构成一个完整的电子应用设计。基于FPGA的SOC系统设计流程主要包括设计规划、硬件控制模块设计及仿真、软件运行平台构建、完整硬件系统构建、系统软件设计与调试等。与基于单片机的纯软件系统设计不同,FPGA的SOC设计涉及硬件设计、软件设计及二者的相互替代及渗透,是一个系统软硬件联合设计与综合调试的过程[2]。

图1 基于FPGA的SOC系统组成框图

2 基于8051 IP核的片上系统设计

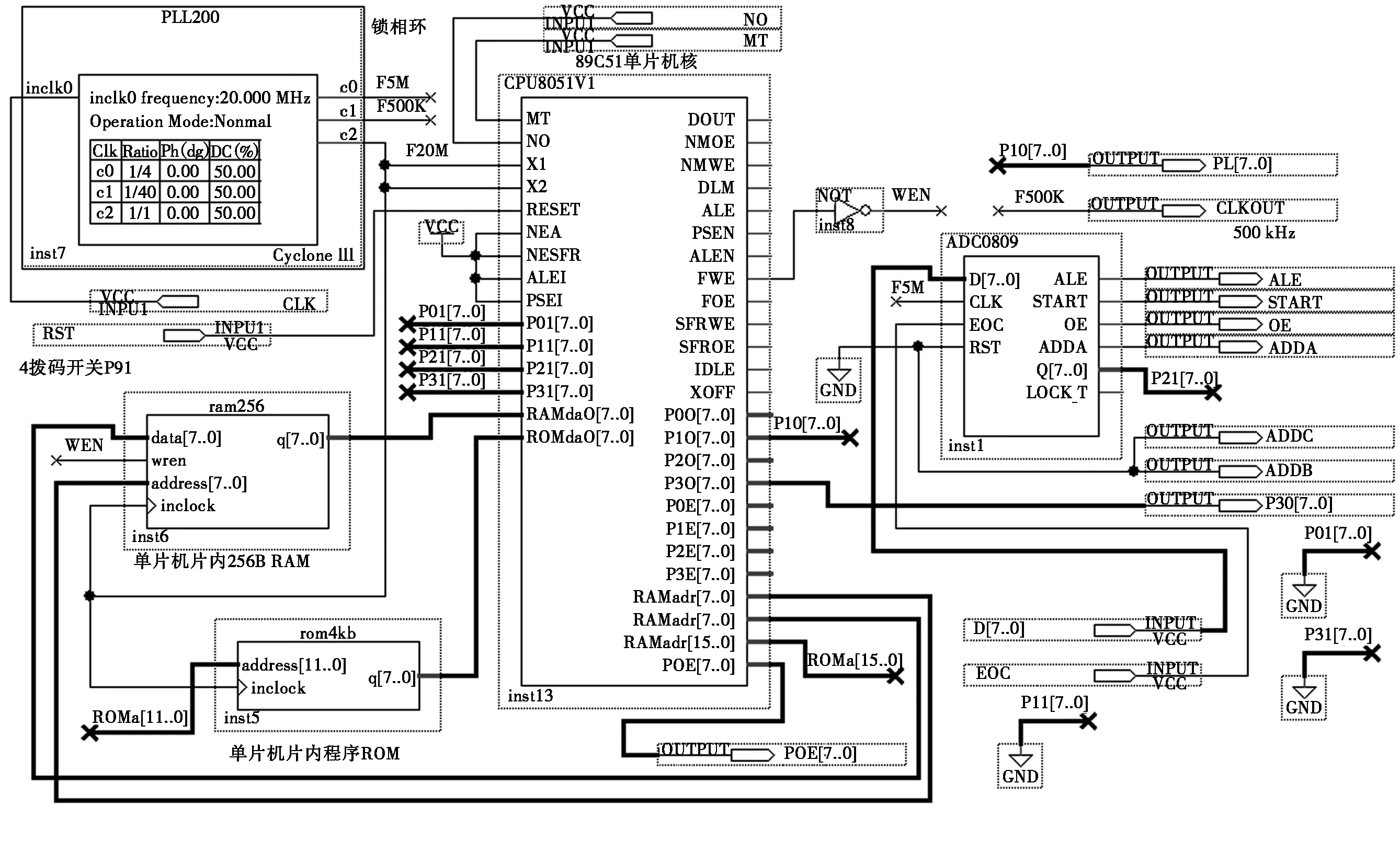

图2所示为在Quartus II设计环境下给出的基于8051 IP核的数字电压表顶层电路图。

图2 基于8051 IP核的数字电压表顶层电路图

其中8051单片机核是由VQM原码经过例化方式生成的,外围配接上程序存储器ROM和数据RAM后就成为一个完整的8051单片机最小系统了。该8051 IP核与标准的8051指令系统完全兼容,大部分控制信号及数据传输接口也与单片机系统相同。

由于FPGA有良好的高速性能,FPGA与高速ADC接口十分常见。在FPGA中,可以使用状态机的形式来控制ADC的采样,并实时地将每一采样周期获得的数据及时地存入FPGA内部的RAM中,在适当的时候由单片机读取处理。本设计给出了基于8051 IP核的数字电压表的设计,其中锁相环模块为系统提供了三个时钟信号;ADC0809控制模块由Verilog语言设计完成[3],用于实现对外部ADC0809芯片的时序控制;ADC0809控制模块的数据输出端口Q[7..0]在FPGA内部与单片机核的P2口的输入口P2I[7..0]相接。在ROM模块中,可通过定制初始化文件LCD1602.HEX实现ASM程序的调用及运行。

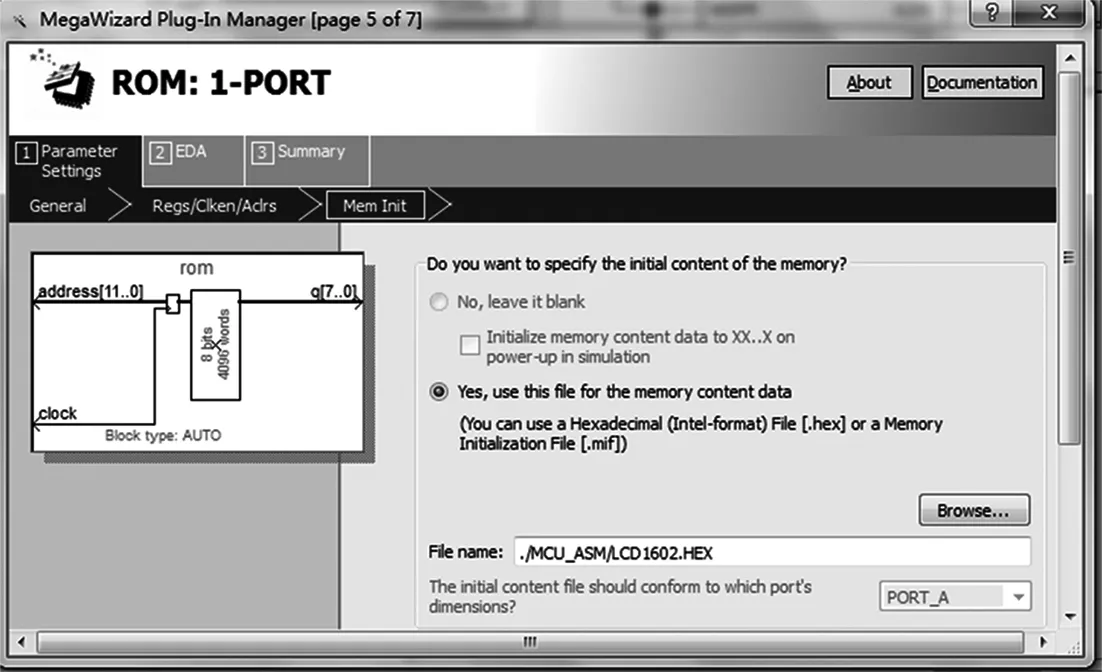

图3为ROM模块初始化文件定制界面。LCD1602.HEX是LCD1602.ASM程序经过汇编软件编译生成的可执行文件。LCD1602.ASM的主要功能是将来自ADC0809采样数据从P2口读入,最后转换为BCD码显示于液晶。以下是一段关于数据采集、转换并显示于液晶的部分ASM程序:

图3 ROM模块初始化文件定制界面

……

GGGG: MOV A, P2;将来自ADC0809采样数据从

P2口读入

PUSH A

MOV 4FH,A

MOV 4EH,#00H

MOV 5FH,#OF4H

MOV 5EH,#01H

LCALL MULNM;将此数乘以500(1F4H)

MOV 4CH,5CH

MOV 4DH,5DH

MOV 4EH,5FH

MOV 4FH,5FH

MOV 5EH,#00H

MOV 5FH,#0FFH

LCALL DIVD;乘积除以255(FFH)

;HEXBCD : 7 BYTE HEX TO

8 BYTE BCD : HEX(3XH-30H)

-->BCD(4XH-40H)

MOV 30H,4FH

MOV 31H,4EH

MOV 32H,#00H

MOV 33H,#00H

MOV 34H,#00H

MOV 35H,#00H

MOV 36H,#00H

MOV 37H,#00H

LCALL HEXBCD;最后转换为BCD码显示于与液晶

……

在Quartus软件设计环境下,对顶层文件编译,然后下载到开发板上的FPGA芯片中,FPGA输出数据端口连接LCD1602液晶显示器,图4为实测的液晶显示数据。

图4 实测的液晶显示数据

3 结语

基于FPGA的片上系统设计应用越来越广泛,其中核心CPU核可以是一个51单片机核,也可以是其他类型的的单片机核,甚至是功能更强大的ASM处理器。目前基于Nios嵌入式核处理器的应用已经成为现代处理器应用的一个重要方向。基于FPGA的SOC片上系统设计技术不论在功能、速度、成本、灵活性,还是开发效率、系统升级可行性等方面,对应电子工程师们来说都是一个上佳的选择。本设计以8051核为例在FPGA芯片上设计了一个基于SOC的数字电压表,其设计过程与方法适合其他类型的CPU核的设计,具有一定的设计参考价值。