基于MK.1TE测试系统对芯片静电放电(ESD)测试分析

2021-04-04吕友成陈仲永聂帆宇叶武剑

吕友成 陈仲永 聂帆宇 叶武剑

摘 要:ESD是指“静电释放”。静电是一种客观的自然现象,不均匀分布在芯片本身、人体和机器上以及芯片能够存在的环境及周围的事物上。这些静止的电荷随时都可能通过某种方式释放出来。静电释放的特点是高电压、低电量、小电流和作用时间短。随着电子学系统和集成电路,比如专用集成电路(ASIC)或“片上系统(SOC)”的复杂度增加,测试和分析集成电路对静电释放的防护能力是非常重要的。该文将介绍集成电路产品基于MK.1TE测试系统的ESD测试方法和分析。

关键词:静电放电;ESD;MK.1TE测试系统;ESD击穿的临界电压

中图分类号:TN40 文獻标识码:A 文章编号:2096-4706(2021)18-0035-05

Abstract: ESD refers to “electrostatic discharge”. Static electricity is an objective natural phenomenon, which is unevenly distributed in the chip itself, human body and machine, as well as the environment and surrounding things where the chip can exist. These static charges may be released in some way at any time. Electrostatic discharge is characterized by high voltage, low electric quantity, small current and short action time. With the increasing complexity of electronic systems and integrated circuits, such as specific integrated circuits (ASIC) or “system on chip (SOC)”, it is very important to test and analyze the protection ability of integrated circuits against electrostatic discharge. This paper will introduce the ESD test method and analysis of integrated circuit products based on MK.1TE test system.

Keywords: electrostatic discharge; ESD; MK.1TE test system; critical voltage of ESD breakdown

0 引 言

在半导体工业中,这几十年来,集成电路(IC)一直按照摩尔定律前行,芯片的制造工艺已从早期的微米级,经历纳米级,发展到今天的深纳米级。芯片上晶体管的数量呈指数增长,其性能更好,价格更便宜。 因半导体器件的集成度越来越高,工艺越来越复杂,IC中潜在的破坏性的ESD(Electro-Static discharge)变得越来越重要和典型。有数据表明,在硅器件失效模型分布中,在接近50%的EOS案列中大约有10%是ESD引起的。因此,在芯片量产前测试其静电放电电压是非常必要的。

1 MK.1TE测试系统

1.1 MK.1TE测试机台

MK.1TE测试系统是一种基于继电器的超快ESD和静态闩锁测试系统,用于评估高级IC器件。MK.1TE ESD和静态闩锁测试系统为用户提供高级功能,用于按照当今的人体模型(HBM)和机器模型(MM)ESD标准测试中等引脚计数的器件,MK.1TE测试机台如图1所示。

1.2 Scimitar软件

基于Windows的MK.1TE Scimitar软件直观而且全面,如图2所示。可以快速设置测试。通过使用Scimitar的用户可编程插件功能,不但可以控制外部器件,还可以控制事件触发器输出,后者为外部器件(例如电源)提供TTL控制信号或提供用于触发示波器的控制信号,可以在可执行测试计划内的任意位置定义并布置灵活的参数式测试。

2 静电放电的模式以及工业测试标准

根据ESD产生的原因及其对集成电路放电的方式不同,目前被分类为以下四类。

2.1 人体放电模式

人体放电模式(Human-BodyModel, HBM)用于集成电路因与带电人员接触而产生的放电类型。它由一个充电的100 pF电容组成,通过一个1500欧姆的电阻释放到集成电路中。MK.1TE测试系统在25 V至8 kV电压下使用HBM。由于相对缓慢的上升时间和大的串联阻抗,HBM是集成电路在器件设计中最容易处理的常用模型。适用标准MIL-STD 883 G,Method 3015.7、JEDEC EIA/JESD22-A114、ANSI/ESDA/JEDEC JS-001-2017、AEC-Q100-002。其等效电路图如图3所示。

2.2 机器放电模式

机器放电模式(MachineModel,MM)用于测试集成电路对其他类型ESD损伤的敏感性,包括几种不同的机器模型标准。这些标准都是基于200 pF电容直接放电到IC(通过0 Ω)和串联电感的固有系统设计小于500 nH。这种放电的破坏性是HBM的许多倍。它的波形具有更高的峰值电流,有效地受到集成电路内部阻抗的限制(50~500 Ω)。适用标准JEDEC EIA/JESD22-A115、AEC Q100-003。其等效电路图如图4所示。

2.3 器件充电模式

是指IC先因磨擦或其他因素而在IC内部积累了大量的静电电荷,但在静电积累的过程中没有释放通路,IC并未受到损伤。当这种带有静电的IC在碰触到接地面或其他接地良好的物体时,IC内部的静电电荷就会从自身向外流出,造成静电释放,此种模式的放电时间可能只在几ns内。适用标准ANSI/ESDA/JEDEC JS-002-2018、AEC-Q100-011、EIA/ESDA-5.3.1。

2.4 电场感应模式

电场感应模式(Field-InducedModel, FIM)模式的静电放电发生是由于外在电場影响芯片电荷引起的。过程类似于器件充电模式(Charged-DeviceModel, CDM),这种模式一般在消费类电子中不会有考量,很少有芯片去进行这种测试。在国际电子工业标准(EIA/JEDECSTANDARD)中,对此电场感应模式订定测试规范(JESD22-C101)。

MK.1TE测试系统支持HBM和MM测试。

3 建立有效的测试计划

3.1 适配测试装置Socket

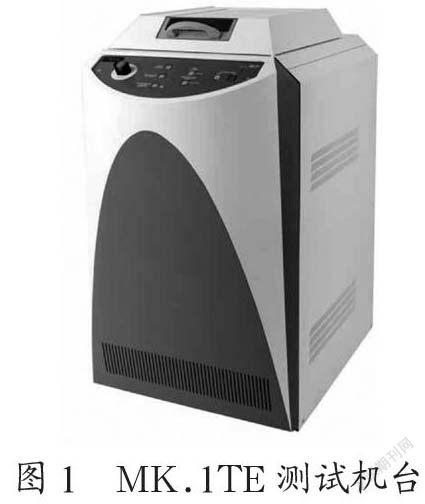

根据被测芯片(DUT)的引脚和封装,匹配不同的Socket,如图5所示。

3.2 静电放电测试组合

静电的累积有正的或负的电荷,导致电流释放通路的方向不同,因此静电放电测试对同一Pin脚而言是具有正与负两种极性。HBM与MM静电放电对IC的放电,有下列测试组合:

(1)All Other Pin TO VSS(±):把所有分组的每个Pin脚分别对每组VSS进行ZAP,脉冲包括正、负,ZAP要求1至3次,间隔100 ms~1 s,不同标准有不同要求。

(2)All Other Pin TO VDD(±):把所有分组的每个Pin脚分别对每组VDD进行ZAP,脉冲包括正、负,ZAP要求1至3次,间隔100 ms~1 s,不同标准有不同要求。

(3)I/O TO I/O(±):把所有分组的每个Pin脚分别对I/O进行ZAP,脉冲包括正、负,ZAP要求1至3次,间隔100 ms~1 s,不同标准有不同要求。

一样数量的样品不同的测试组合,每个组合至少三个样品,或者所有组合放在一颗样品上,但每个ZAP水平至少3个样品。

3.3 具体实现步骤

根据所编写的程序可以快速自动的对所有芯片管脚组合进行ESD应力测试:

(1)创建Device:进行任何测试之前,将DUT信息输入系统。可以从外部文件导入Device信息,也可以通过从头定义布局来创建新的Device,如图6所示。

(2)Pin脚的定义:根据芯片Datasheet对DUT各个引脚分组定义INPUT、OUTPUT、I/O、POWER、GROUND、N/C、CLOCK、AUX等,如图7所示。

(3)Mapping:根据测试夹具的网标,填写Channel Map,它标示测试夹具Pin和ZapMaster MK系列测试通道Pin之间的连接,如图8所示。

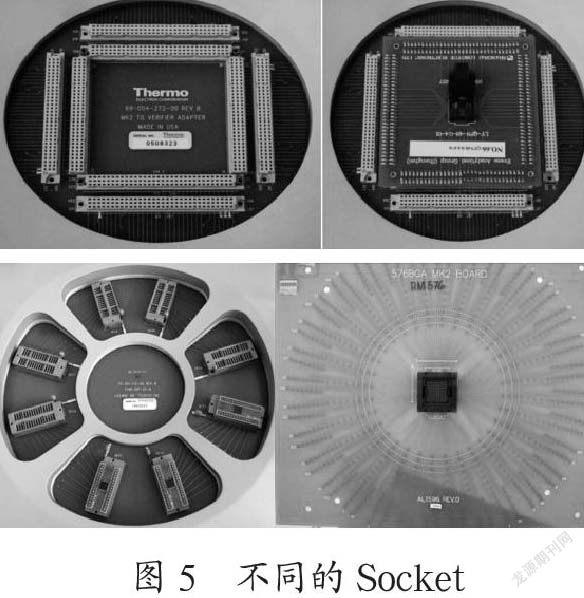

(4)设置参数化数据:参数化数据用于确定指定的引脚组是否已损坏。在进行静电测试前使用参数获取预测试结果,在进行静电测试后重复使用参数,确保在进行静电测试时不会损坏DUT引脚,虽然每个引脚接受相同的ESD应力,参数测试方法可以是不同类型的引脚。每个引脚组可以有自己的一组参数测试条件和极限,如图9所示。

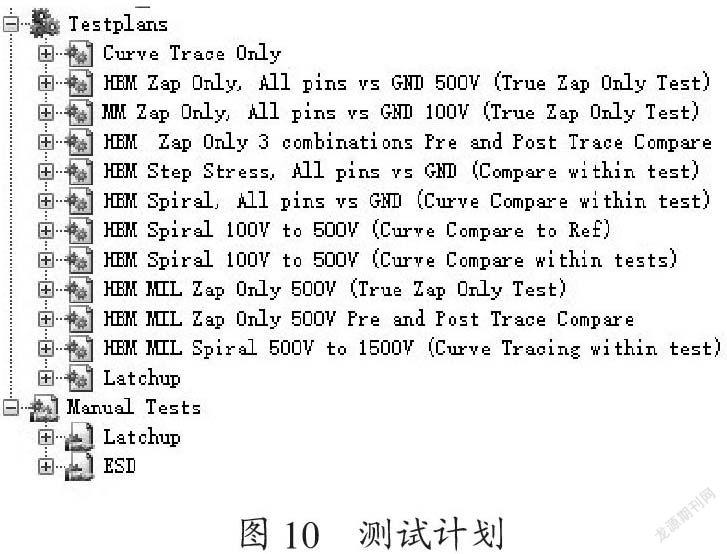

(5)创建Tests和Testplans:对于每个DUT,可以创建多个测试计划;对于每个测试计划,必须指定要包括哪些测试;对于每个测试,都可以修改测试的属性,如图10所示。

在每一测试模式下,DUT的该测试脚先被系统扫描一次I-V特性曲线,然后Zap一个ESD电压,之后系统再次扫描该Pin脚I-V特性曲线,并且系统自动把Zap前后扫描的I-V特性曲线对比,检测该测试脚是否己被ESD所损坏,若该Pin尚未被损坏再去加一个step的ESD电压,再扫I-V特性曲线与第一次的曲线对比,如此反复直至击穿,此时的击穿电压为ESD击穿的临界电压(ESD failure threshold Voltage)。为了降低测试周期,通常起始电压用标准电压的70% ESD threshold,每个step可以根据需要在测试计划中调整。

4 静电放电故障判断

IC经ESD测试后,常见的有以下三种方法判断IC是否被ESD损坏。

4.1 绝对漏电流

在DUT进行ESD测试前,先测试其Pin脚的漏电流,将该数据与最终经过ESD测试后的Pin脚漏电流进行比较,以确定偏移值。超出允许偏移值(Pin脚的漏电电流超过1 μA (或10 μA))的将被定义为失效。表1列出不同组件类型的特定关键参数的允许位移值。

4.2 相对I-V漂移

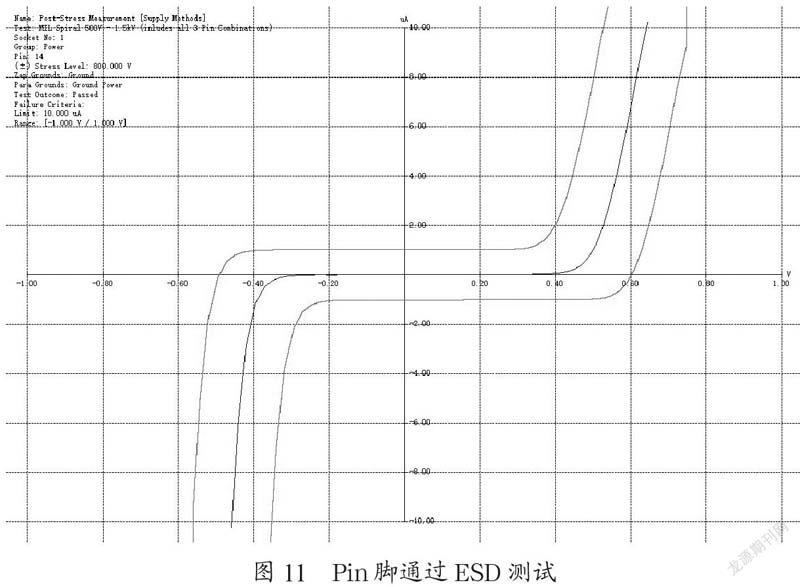

当IC被ESD测试后,IC的Pin脚内部的I-V特性曲线漂移量在30%(20%或10%)。图11为Pin脚通过ESD测试,图12中Pin脚经过ESD测试后Pin脚I-V特性曲线超过规定漂移量。MK.1TE测试系统支持I-V曲线跟踪对比。

4.3 功能参数测试法

在IC进行ESD测试之前,应进行完整的功能参数测试,然后打上ESD测试电压,再拿去测试其功能是否仍符合原来的规格,对于高速数字电路、高性能混合电路、微波/射频电路、通讯接口电路、CPU芯片、嵌入式存储器等各类芯片复杂的测试,可以使用ATE机进行测试。

IC经静电放电后失效类型分为两大类:

(1)致命失效:介质击穿、金属溶断、PN结穿刺、接触孔金属电迁移等,它会直接造成开路、短路或漏电增大,导致芯片永久性失效。

(2)性能退化:会造成芯片内部电路参数漂移、寿命降低,影响芯片的工作性能但一般不会立刻导致芯片失效。因此要结合不同的判定准则标注芯片ESD临界电压才更有意义。

图13为某IC在相对I-V漂移准则下的ESD临界电压结果,几个测试脚的耐压值不同,每一Pin脚都有其ESD击穿的临界电压。而此颗IC脚中最小的ESD击穿的临界电压值被定为此颗IC的ESD击穿的临界电压。因此,芯片的ESD设计应该从整体网络去考虑,在不同的网络节点注意内部模拟器件的保护,提升芯片所有Pin脚的ESD击穿的临界电压,不要让其他非ESD保护器件去分担ESD应力。

5 结 论

集成电路基于MK.1TE测试系统的ESD测试参照I-V特性曲线相对漂移的判断准则,可检测IC每个Pin脚的ESD击穿的临界电压,但是由于制造的工艺特性,每颗IC的ESD耐压值也会有差异,所以在相同批次IC的每组Pin脚测试时,原则上抽样的IC数量不少于3颗,其中Pin脚最低的ESD击穿的临界电压为本批次IC的ESD击穿的临界电压,如果抽样数越多,芯片ESD的击穿的临界电压值就越精确。

随着COMS工艺水平的提高,芯片ESD的防护也越来越困难,ESD的保护已经不是输入脚或输出脚的ESD保护问题,而是全芯片的静电防护问题。

参考文献:

[1] 柯明道. ESD靜电防护(台湾柯明道教材) [EB/OL].(2011-10-17)[2021-07-03].https://www.docin.com/p-274717358.html.

[2] Thermo Fisher Scientific Inc.ZapMaster MK Series Operations ManualMA-70-000-005-10-B[EB/OL].[2021-08-10]. https://www.doc88.com/p-69416038364262.html.

[3] U.S.A.Department of Defense. MIL-STD-883G method 3015.7 [S].Washington D.C.,2006.

[4] Automotive Electronics Council. AEC-Q100-002/003 REV-E [S].AEC Component Technical Committee,2013.

作者简介:吕友成(1990—),男,汉族,广西南宁人,测试工程师,本科,研究方向:芯片测试验证;陈仲永(1983—),男,汉族,广东阳江人,系统工程师,研究方向:集成电路系统验证;聂帆宇(1991—),男,汉族,江西抚州人,技术中心副总经理,硕士研究生,研究方向:芯片设计、测试验证项目管理;叶武剑(1987—),男,汉族,广东韶关人,讲师,博士研究生,研究方向:计算机体系结构深度学习。