基于序列部分频点匹配的跳频自同步方案

2019-09-06赵祥武全厚德崔佩璋

赵祥武,全厚德,崔佩璋

(陆军工程大学石家庄校区,河北 石家庄 050003)

0 引言

跳频同步技术作为跳频通信的关键核心,跳频电台性能的好坏跟同步性能的优劣有着必然的关系,同时直接决定着跳频通信系统能否正常工作,对于能够及时使用跳频电台传输有用信息提供了良好的保障,所以跳频同步需要尽可能小的同步时间,对于干扰能够及时地抵抗,抗干扰性能要好,跳频同步信号要足够的隐蔽,避免敌方侦测干扰[1]。传统跳频同步方法主要有四种,分别为参考时钟法、独立信道法、同步字头法和自同步法等。自同步法是指利用发射端中信息带有同步信息,接收端提取到同步信息,进而达到同步的目的。常见的自同步方法有串行自同步捕获方案与并行自同步捕获方案,但是串行捕获方案同步捕获时间较长,并行捕获方案系统太复杂。

自同步方案虽然可以节省信道资源的优点,但是需要多次发送同步引导码进行同步,易被敌方干扰。所以本文提出了基于序列部分频点匹配的自同步方案。

1 工作原理

传统同步方案包括同步捕获、同步识别、同步跟踪三个方面[2]。同步捕获阶段需要依靠同步引导码来输送跳频同步的信息,这样才能实现跳频同步。本文就提高同步信息的隐蔽性,提出了新型的跳频同步方案。

1.1 序列部分频点匹配自同步方案同步原理

序列部分频点匹配的自同步方案中接收机处于三种工作状态,分别为同步捕获状态、正常跳频状态、同步保持状态。同步捕获阶段不需要同步引导码,接收机处于同步捕获状态时,各支路按某种算法选择各支路的频率与本地跳频序列产生器生成的频率进行混频,通过能量比较输出各支路最佳频率,接收端通过搜索这些同步频率并与接收端本地跳频序列产生器进行相位的移动调整跳频信号的相位,实现收发双发的同步。序列部分频点匹配的自同步方案同步捕获的原理框图如图1所示。

图1 序列部分频点匹配的自同步方案同步原理框图Fig.1 Synchronization schematic block diagram of self-synchronization scheme with partial frequency point matching in sequence

设发射机发射的跳频序列设为N,跳频序列N中有部分序列f1,f2,f3,…,fn已知,接收机在进行同步捕获时,通过能量比较后捕获到一条跳频同步序列设为N1,序列N1中只有用来完成同步的部分频率f1,f2,f3,…,fn已知,f1,f2,f3,…,fn是接收端本地伪随机码发生器产生的每一条支路用来进行混频的频率,这些频点的时频对应关系通过分析可知,而同步序列中其他未知的频点不影响同步过程,此时认定N1为发射的跳频序列其中的一段短序列,通过相位移动可以准确地完成跳频同步。

1.2 同步捕获搜索匹配算法原理

跳频同步开始之前,收发双方首先会进行粗略地时间调整,保证时间误差在有关跳频规定的误差时间之中。新型跳频同步方案的接收机设置依然采用并行的同步支路设置,利用有限量的支路进行并行接收,设支路数为S。同步开始前,发射机在空中发射没有被调制的跳频信号N,接收端进入同步捕获状态,接收到的信号经各支路与本地频率合成器产生的频率进行混频后,进行能量比较,通过一段时间之后,接收端可以通过能量比较确定出接收到的跳频同步序列,该跳频同步序列按一定的时间顺序的本地频率合成器的混频所组成,它是发射机在空中发射的跳频信号的某部分的序列,记为N1。接收机通过对本地频率合成器的跳频频点进行快速地扫描,扫描结果是收发两端在相位误差最大的时间范围内的跳频序列P,在跳频序列P中使用某种特定的算法对接收到的序列N1进行匹配,肯定会匹配到似然度最大的跳频序列N2,通过N2在P中的相对位置,可以算出接收机与发射机的相位差的大小,然后调整本地时钟,这样才可以实现同步捕获。接下来接收机进入跳频工作状态,同步识别完成以后,接收机进入跟踪状态,依靠锁相环的技术完成相位误差的进一步缩小,缩小到规定误差范围,这样才算完成了同步跟踪工作,跳频电台完成了同步捕获和跟踪之后,收发双方转而进入正常通信状态。同步捕获搜索匹配算法原理如图2所示。

图2 同步捕获搜索匹配算法原理框图Fig.2 Principle block diagram of synchronization acquisition search matching algorithm

当外界存在干扰时,如果接收端通过能量比较后得到的序列N1与发射端向空中发射的跳频序列N出现差异时,此时认定跳频同步捕获存在误码,然后再从序列P中搜索匹配N1,将出现两种状况:第一种是序列P中并没有搜索匹配到N1,跳频电台重新进行同步捕获,直到完成跳频同步过程;第二种情况是序列P中出现了序列N1,系统发生虚警,跳频电台在经过同步识别模块时会处理掉这种情况,然后重新进行捕获,然后完成同步。

根据有关国家标准对于跳频电台的捕获时间的具体设定,在本节中假设如下:收发两端最大时间误差为5 min,设定跳速为200跳/s,跳频频点设为512个,由于收发双方不能明确相位前后关系,通过前后各5 min快速扫描,所以最大的相位误差为120 000跳,扫描得到的跳频序列为P,我们假设接收机跳频序列P1滞后于发射机P,对序列部分频点匹配的自同步方案进行详细说明,同步捕获完成后,接收端根据当前相位快速扫描P得到序列P2,并且发射机用于进行同步的序列也在P2中,由图2中可以看出发射机超前的相位时长为T,接收机在T1时开始捕获到跳频同步序列N,在T2时完成对同步序列的捕获,并且对序列N在接收端的序列P2中进行匹配,在T3时刻,序列N匹配完成,得到序列N在P2中的位置信息,最后利用计算可以得到T的具体值,然后调整接收端的相位,完成同步捕获,即收发双方相位相同。

2 同步方案设计

2.1 同步捕获方案设计

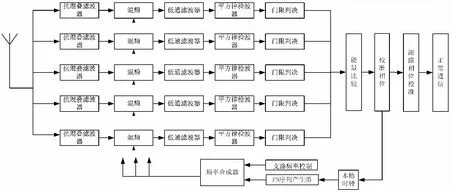

序列部分频点匹配的自同步方案的系统框图如图3所示。接收端共有S条混频支路,每条支路的设计与构造相比于并行自同步方案的支路设计并无差别,使用相同的滤波器以及平方律检波器,每条支路进行混频的频点都是发射机中随机抽选的,保证了跳频序列的随机性[3]。接收端本地频率合成器受支路频率控制,工作处于三种工作状态:一是同步捕获状态,支路频率控制器控制频率合成器合成S条支路频率;二是正常跳频通信状态,本地支路频率控制器不发挥作用,本地PN序列生成器控制频率合成器进行工作;三是同步保持状态,同步完成之后,本地频率控制器控制频率合成器避免由于时间误差的增加导致失同步。频率合成器由S路DDS完成。

图3 序列部分频点匹配自同步方案系统框图Fig.3 System block diagram of sequence partial frequency matching self-synchronization scheme

接收端进行跳频同步捕获时,本地支路控制器进入同步捕获状态,从而使得频率合成器进入工作状态,控制其产生S路混频频率,假定接收端使用支路数S=21,同步序列N分为21个小组,本地支路频率控制器随机从每组频点中抽出一个频率作为混频的频率,如果接收端在一段时间内没有完成跳频捕获,系统则自动重新选择每组中的频点进行频点更替,替换下来的频率被标记下来,以后不再进行更替。接收机支路数的选择在接下来的分析中会有说明,不在此进行叙述。接收端进行信号频率判决后,经过对支路判决后的频率进行能量比较,选取的规则是每跳中能量取得最大,这就表明此频率为有用信号的频点,然后进行频率的捕获,通过一段时间的捕获,依据时间先后顺序确定各支路最佳频率选择,这样可以得到用于同步的跳频序列N,其中序列包括n个频点,这n个频点的位置关系确定了同步序列的唯一性,如果在序列P中出现好多相似的同步序列N,跳频通信系统会发生虚警,所以利用n的多少以及n个频点在序列里的位置关系来唯一确定同步序列N。由于同步序列N是随机选择的,n作为序列N的唯一变量,n的选择很关键,n的数值越大,同步序列N出现相似的概率会很小很小,但是同样也会影响到整个同步系统的时间,n的数值越小,同步序列N出现相似的概率会增加,但同时捕获时间很明显减少。

由于无法确定接收机与发射机的相位到底是超前或滞后,所以接收端需要在最大双方时间误差T前后都进行扫描,序列P的序列长度为120 000跳。FPGA的时钟频率数量级为109,对于序列P来说扫描时间的数量级为10-4,对于同步捕获来说微乎其微,不影响实时性的要求。

同步捕获流程如图4所示,系统进行同步捕获时,由于收发两端相位差最大是5 min,所以接收端进行了前后5 min的扫描得到了序列P,并明确了序列P中各个频点与时间的对应关系。

图4 同步捕获流程图Fig.4 Flow diagram of synchronization acquisition

2.2 同步保持方案设计

跳频电台完成同步后,进入正常工作状态,当跳速为200跳/s时,对于时钟为±10-6漂移一个周期所用的时间为41.6 min;对于时钟为±10-5漂移一个周期所用的时间为4.16 min,证明时钟越稳定,漂移时间越长,在序列部分频点匹配同步方案中,不使用勤务频率传递同步信息,跳频电台在正常通信中利用锁相环技术进行跟踪相位的校准,在通信双方静默的时期,收发两端的时钟会由于时钟稳定性的差异发生时钟漂移,本文所提的方案所允许的静默时长最多为41.6 min[6]。

接收端正常跳频工作时,接收信息的支路固定不变,收发双方静默结束后,跳频电台会进行同步保持,而频率合成器也进入同步保持状态。由本地支路频率控制产生混频频率,设此支路为S1,而其他支路(S-1条)的混频频率与相邻支路的频率差在一个相位上,即如图中5所示,接收端进行同步保持时,每条支路的频率都相差一个相位,由于时钟的漂移,假设某一时刻支路Sn接收有用跳频信号,而相邻支路Sn-1没有接收到任何信号,所以利用相邻两条支路的相位差从而校准收发两端的相位差,从而完成同步的保持。

同步保持流程框图如图6所示,收发两端静默结束之后,跳频电台进入同步保持,而且支路频率控制器投入到保持状态,各支路开始收到跳频信号,经过能量比较之后,频率能量最大的支路被认定作跳频信息的接收支路,经过同步识别确定是否与发射机发射的跳频频率相同,由此可以得到本地跳频信号相位与发射机的跳频信号相位差,通过调整频率的时间位置关系,跳频电台进入到正常工作状态,完成同步识别。

2.3 序列的唯一性分析

根据国家标准的规定,超短波跳频电台的周期不少于十年,所以该跳频电台的周期设定为236-1,在跳频通信中收发双方传递信息仅会使用很短的跳频序列,而收发双方相位差确定的序列P的随机性会直接决定通信性能的优劣,本方案所需的序列P=120 000,可以满足实际的需要[7],所以本节就序列N的唯一性进行统计分析,在序列P中随机选择一段短序列N,其中序列N含有n个跳频频点,以此作为标准频率,标准频率随机选取,且n个跳频频点时间位置信息随机。

图5 同步保持方案设计Fig.5 The design of synchronization maintenance scheme

图6 同步保持流程框图Fig.6 Flow diagram of synchronization hold

图7 频率间隔随机的同步序列示意图Fig.7 Synchronization sequence diagram of random frequency intervals

表1 同步序列N在10条长序列P中出现次数

3 无干扰条件下捕获性能分析

本同步捕获方案在没有干扰环境中,假设跳频频点为256个,由跳频速率可得到跳频周期为0.005 s,接收机共有支路S条,即有S个跳频频点来进行混频。跳频同步时间为t=tr+ts,其中tr为接收端捕获到跳频同步序列N所用的时间,而ts为能量判决后进行序列搜索匹配以及调整收发两端相位差所用的时间,ts主要由计算机硬件处理速度以及搜索算法的快慢来决定,本文主要考虑对tr进行理论分析并进行仿真分析。

在没有干扰的情况下,本同步方案的同步捕获时间的概率密集度函数f(x)表示为:

(1)

同步捕获时间的分布函数F(x0)表示为:

(2)

捕获时间期望表示为:

(3)

由图8,图9中可知当接收机支路数S越大,跳频电台在短时间内捕获的概率越大;但是支路越多,相应的系统复杂度越高。如何选择合适的支路数,既能满足同步捕获的需要,又能尽可能地减少系统复杂度,是当前需要解决的问题。对跳频同步方案捕获期望进行仿真分析,当S=21时,同步捕获时间为0.6 s,经过理论计算与仿真结果进行对比,满足某标准规定,即超短波跳频电台的同步捕获时间不应大于0.6 s。仿真结果如图10所示。

图8 不同支路数捕获时间的概率密度函数Fig.8 Probability density function of acquisition time for different branches

图9 不同支路数捕获时间的概率分布Fig.9 Probability distribution of acquisition time for different branches

图10 不同支路数下同步捕获时间期望Fig.10 Synchronization acquisition time expectations for different branches

4 结论

本文提出了基于序列部分频点匹配自同步方案,该方案在不使用同步引导码的情况下,按照序列部分频点匹配的同步方案,任意设定接收频点,根据频点间隔特征信息在本地已知跳频序列中进行搜索匹配,进而计算出跳频序列收发两端的相位差,从而调整相位差实现跳频同步。理论分析与仿真实验结果表明,该方案在捕获时间上优于串行同步捕获方案,就复杂度而言,相较于并行同步捕获方案有了很大的降低,同时该方案不需要同步引导码,提高了抗干扰的性能。