基于AT89S52的多路数据采集系统的设计与实现

2017-04-06董亚男

董亚男

(吉林动画学院,吉林长春130011)

基于AT89S52的多路数据采集系统的设计与实现

董亚男

(吉林动画学院,吉林长春130011)

设计了一种基于AT89S52的多路数据采集系统.该系统由两路串行A/D转换器ADC0832、单片机AT89S52、外扩62256 RAM和LED数码显示等组成,其中给出了系统设计原理框图、硬件接口电路图和软件设计流程图.通过对两路波形信号进行采集、处理和显示,结果表明该系统能实现多路数据的实时采集、数据处理和显示输出等功能,具有较好的通用性,可广泛应用于工业自动控制领域.

单片机;串行A/D;数据采集;存储器

单片机以控制功能强、可靠性高、速度快、功耗低等特点被广大电子设计爱好者所青睐.数据采集是实现智能控制重要环节,被广泛应用于工业、医疗、测量、自动控制等领域.近年来,随着电子技术、信息技术的不断发展,数据采集技术也呈现出速度更快、数据量更大、通道更多的发展趋势.实际中对现场信号所采集的大量数据需要保存和处理,在此情况下对系统存储空间大小和处理能力要求很高,由于普通单片机存储空间的限制,其自身的内部空间难以满足大量数据存储要求.为了实现既能有效完成实时数据采集,又能进行数据的运算和处理功能,本文设计看了一种基于AT89S52的多路数据采集系统.该系统由两路串行A/D转换器ADC0832、AT89S52单片机、外扩62256RAM和LED数码显示等组成,给出了系统设计原理框图、硬件接口电路图和软件设计流程图.通过对两路波形信号进行采集、处理和显示,结果表明该系统能实现多路数据的实时采集、数据处理和显示输出等功能,具有较好的通用性和兼容性,可广泛应用于各种自动控制领域.

1 多路数据采集系统总体设计

1.1 系统结构体系

该数据采集系统主要由A/D转换器ADC0832、单片机AT89S52、数据存储器62256和LED数码显示等组成.图1为系统总体设计原理框图.系统主控芯片AT89S52有8k字节Flash,256字节RAM,32位I/O口线,看门狗定时器,2个数据指针,三个16位定时器/计数器,一个6向量2级中断结构,全双工串行口,片内晶振及时钟电路.

图1 系统结构体系框图

1.2 系统硬件电路设计

如图2所示,采集系统通过单片机P3.5、P3.4和P3.3三个引脚来分别控制ADC0832的CS片选使能端、CLK时钟脉冲端和DI、DO端达到对ADC0832的A/D转换控制,随后数据传入,单片机对采集数据进行处理,存入扩展数据存储器62256中,系统使用单片机通用的外扩数据存储器方法,然后通过P1.6与P1.7两个引脚来控制74HC164芯片,用于通过LED显示采集数据.采集系统也可以通过芯片MAX232与PC机进行串行通信.采集系统电路结构图如图2所示.系统工作时通过前端AD对模拟信号进行采集,然后经过单片机进而将数据存储到扩展存储器,方便进行数据的处理和再利用,然后LED数码管显示采集结果.同时,可根据串行口通信方式发送给PC机,使用PC机进行后续的结果处理.

图2 系统电路结构图

2 A/D转换器ADC0832

ADC0832是美国国家半导体公司(NationalSemicon-ductor)生产的8位的双通道串行A/D芯片.它的体积小,兼容性强,功耗低,性价比高.它的输入输出电平与TTL/CMOS相兼容,工作频率为250KHZ,转换时间为32us.芯片工作温度最大可达-40℃~+85℃.

2.1 A/D转换器接口

转换器接口如图3所示,串行A/D转换器所用引脚少,线间干扰小.1脚CS为片选使能端,当CS为低电平有效.2脚和3脚分别为CH0,CH1是两路模拟信号输入端,用于接受要将要输入转换的电压信号.4脚为GND是芯片工作的参考0电位和电源地.5脚6脚分别为DI和DO端,DI为信号输入,两路模拟通道选择输入端.当工作时,首先由DI端输入信号选择转换器工作方式.DO为信号输出,模数转换结果串行输出端.当转换完成后,DO端依次输出转换结果.因为DI端与DO端并未同时使用所以可以复用一根数据线,如图3连接所示.7脚为CLK是串行时钟输入端,用于提供转换器工作时许脉冲.8脚为VCC是正电源端和工作时的参考电压输入端.

图3 ADC0832引脚结构图

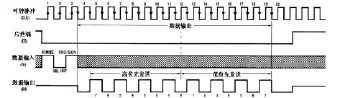

2.2 A/D转换器工作时序

当CS为低电平选通时,选择转换器,DI作为通道工作方式选择的输入端,首先输入高电平开始位,然后输入两位工作方式选择地址,随后变成高阻态.因此DO和DI端在工作时并未同时有效,所以电路设计时可将DO与DI并联在一根数据线上使用,如图3所示.当不需要ADC0832工作时,CS片选使能端为高电平,芯片禁用,其它引脚电平任意.当ADC0832工作时,CS片选使能端必须为低电平,并且保持到AD转换结束.芯片开始工作,由CLK为芯片提供时钟脉冲,转换时序如图4所示.

图4 ADC0832时序图

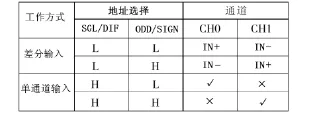

在第1个时钟上升沿来临时,DI作为通道工作方式选择端,首先必须置位为高电平表示开始位,之后两个时钟上升沿时输入两位工作方式选择位,其工作方式选择如图5所示.此2位配置位数据为“0”“0”时,进行差分输入,CH0为正输入端,CH1为负输入端.当2位数据为“0”“1”时,进行差分输入,CH0为负输入端,CH1为正输入端.当2位数据为“1”“0”时,只对CH0进行单通道数据转换.当2位数据为“1”“1”时,只对CH1进行单通道数据转换.当第三个脉冲下降之后DI端输入就不再工作直至下一次选中芯片.转换开始后,经过一个时钟周期的延时,随后输出数据.数据输出先从高位到地位依次输出,然后再从地位到高位依次输出,数据输出两次可用作数据校验,数据输出完成后CS片选使能端置为高电平,一次AD转换结束.

图5 ADC0832工作方式选择

3 外部并行数据存储器62256

单片机扩展系统中,数据存储器由随机存储器组成,最大可扩展64K.静态RAM62256为32KBX8静态RAM.由于面向控制,实际需要扩展容量并不大,所以一般采用静态RAM较方便.

3.162256 接口

选用静态RAM62256扩展32K数据存储器.引脚为28脚,连接外部数据存储器如图2所示,用P0口和P2口连接15位A0-A14地址引脚,其中P0口接373地址锁存器和8位数据端,用于地址和数据发送复用.RD和WR分别连接62256的22脚OE和27脚WE,访问外部RAM时采用MOVX@DPTR指令,同时P0和P2传送15位地址.

3.2 外部数据存储器操作时序

访问外部数据存储器的读/写操作时序如图6所示.图6(a)所示为外部RAM的读时序,第一个机器周期的S1状态若地址允许信号ALE由低电平变高电平(1),开始了读周期.在S2状态CPU由P0口送出低8位地址,P2口送出高8位地址,在ALE的下降沿(2)把低8位地址存入外部锁存器,而P2口的高8位地址保持不变(3).在S3状态,P0口总线驱动器进入高阻状态(4).在S4状态,读控制信号RD变为有效(5),被寻址的RAM存储器62256略过片刻后把有效数据送总线上(6),当RD由低电平变高电平后(7),被寻址的存储器62256其本身的总线驱动器悬空(8),使P0总线又进入高阻态.

图6 外部存储器读/写时序

如图6(b)所示为外部RAM的写时序,与上类同.但写的过程是CPU主动把数据送到总线上,因此在S3状态总线不会出现高阻态,而是送出数据.在S4状态,写控制信号WR有效,选通被寻址的存储器单元,P0口上的数据就写入到该单元中.

4 系统工作原理及软件设计

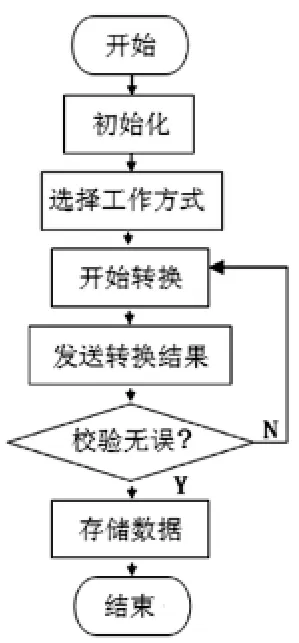

本数据采集系统程序设计思想为软件部分由4大模块组成,主要包括数据采集部分、数据处理存储部分、LED显示部分和串行口通信部分.主程序逻辑流程图如图7所示.

系统工作开始时,首先拉低ADC0832的CS片选使能端,选中芯片开始工作,然后设置开始位为高电平,工作开始.对DI输入2位数据设置工作方式,之后经过一个CLK脉冲准备接受数据.DO端首先从高位到低位发送8位数据,然后再次从低位到高位发送8位数据(如图4所示),单片机接收两次发送数据用于校验转换数据是否准确,当确认数据转换正确无误后存储数据.AD采集过程程序流程图如图8所示.当确定接受数据无误后,采集得到数据转存入外部存储器,通过置地址指针DPTR来进行数据存储.之后可调用LED显示程序对转换数据进行显示.数码管显示程序流程图如图9所示.后续处理也可调用串行口通信程序数据发送给上位PC机进行处理.

图7 主程序逻辑流程图

图8 AD采集逻辑流程图

图9 LED显示逻辑流程图

5 实验数据及结论

表1 测试数据

表1为数据采集器输入信号、实际信号与结果显示数据,如表中结果显示该数据采集器在误差允许范围内工作良好,存储器读写顺利,实物图如图10所示.

此多路采集系统由两路串行A/D转换器ADC0832、单片机AT89S52、外扩62256RAM和LED数码显示等组成,其中给出了系统设计原理框图、硬件接口电路图和软件设计流程图.通过对两路波形信号进行采集、处理和显示,结果表明该系统能实现多路数据的实时采集、数据处理和显示输出等功能.在应用中可以对电压信号进行直接采集,也可对传感器信号进行采集.在以上设计基础上还可以将双路采集系统扩展成为差分采集数据采集系统,也可根据需求实现更多路的数据采集,同时可以选择更大的外部扩展存储器来进行更大的数据存储.这种可扩展电路具有高性价比,无需选择更昂贵的大容量控制芯片,有较好的通用性和兼容性,可广泛应用于各种自动控制领域.

图10 多路数据采集器实物图

〔1〕National Semiconductor Corporation.DS005583 DATASHEET[R].2002,7.

〔2〕马俊.一种基于DSP和MCU的双CPU数据处理系统设计[J].测控技术与仪器仪表,2008(3):79-82.

〔3〕陈学煌.一种新型非接触式速度测量装置.传感器技术[J]. 2004,23(1).

〔4〕马俊.基于DSP的多路数据采集系统[J].测控技术与仪器仪表,2007(12):79-85.

〔5〕ATMEL Corporation.AT89S52 DATASHEET[EB/ OL].http://www.alldatasheetcn.com.

〔6〕胡汉才.单片机原理及其接口技术(第3版)[M].清华大学出版社,2010.

〔7〕马忠梅.单片的C语言应用程序设计(第三版)[M].北京航空航天大学出版社,2003.

〔8〕李刚民.单片机原理及实用技术[M].高等教育出版社,2005.

〔9〕谷树忠.Altium Designer教程:原理图、PCB设计与仿真[M].电子工业出版社,2010.

TN707

:A

:1673-260X(2017)03-0048-03

2016-11-08

教育部重点实验室开放基金和青海省135高层次人才工程项目资助的课题;教育部春晖计划Z2011019