一种基于FPGA的PWM防错输出控制电路

2022-02-28朱耀国屈盼让蔡晓乐

朱耀国,屈盼让,蔡晓乐

(中国航空工业集团公司西安航空计算技术研究所,陕西 西安 710068)

0 引言

随着航空工业的发展,多电飞机目前代表着先进飞机的发展趋势,多电飞机是使用电力系统部分取代原来的液压、气压和机械系统的飞机[1]。随着多电飞机的发展,机载电气设备占机载设备比例不断提升,采用PWM脉冲宽度调制技术的机载电气设备,如步进电机、电液伺服阀、风机、调光灯等,在多电飞机中广泛使用。

PWM利用半导体开关器件的导通与关断,将直流电压变为电压脉冲列,通过控制电压脉冲列的周期与电压脉冲的宽度,即占空比,达到变压变频及控制和消除谐波的目的的一种控制技术[2]。以电机调速为例,在脉冲作用下,电机断电时,速度逐渐减小;当电机通电时,速度增加,只要按照一定规律,改变电机的通电时间,就可实现电机的速度控制[3]。但是在实际应用中如果未作处理,立即更新参数,那么在当前的PWM输出周期可能会发生错误输出。

1 控制电路

1.1 电路简介

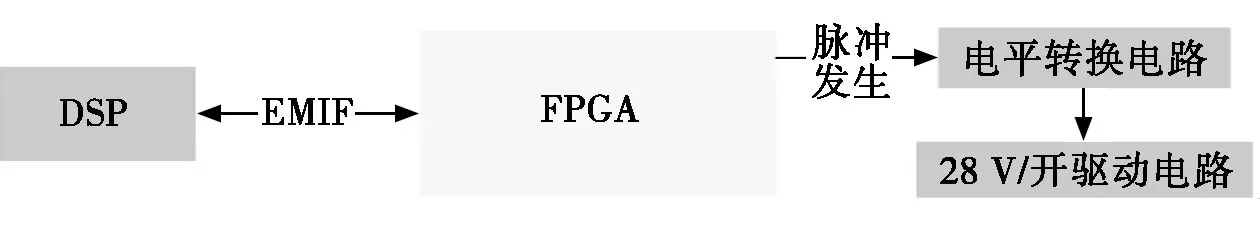

基于FPGA的PWM输出控制电路结构框图如图1所示,电路由DSP、FPGA、电平转换电路、28 V/开驱动电路组成。DSP通过EMIF总线与FPGA间通讯,对PWM控制的参数进行读写;FPGA根据DSP写入的PWM控制参数生成PWM驱动脉冲;电平转换电路将FPGA的输出引脚上发出的3.3/0 V驱动脉冲转换为28V/开驱动电路的输入控制电平;28 V/开驱动电路根据输入脉冲发出相应的PWM输出。

图1 基于FPGA的PWM输出控制电路结构框图

1.2 EMIF总线数据传输

外部存储器接口(EMIF),External Memory Interface,是DSP器件上的一种接口。对于一些对存储空间超过DSP自身片上存储资源的应用,EMIF控制器可以用来访问额外的片外存储器资源,额外的外部存储资源既可以用来保存程序指令,也可以用来保存数据[4]。EMIF总线属于并行总线,具备分开的16位并行地址总线/数据总线,以及片选使能、读使能、写使能信号[5]。

在本文的设计中,FPGA作为EMIF总线的从机被DSP访问,由DSP通过EMIF总线向FPGA写入PWM周期、高电平时间数据,以及PWM使能信号。其中PWM周期PWM_PERIOD及PWM高电平时间PWM_HIGH均为32位数据,需要EMIF总线分两次依次写入高16位及低16位以配置数据,1 lsb数据表示20 ns,支持配置时间20 ns~85 s; PWM_ENB为16位数据,最低两位被写为"11"时表示PWM输出使能,"00"、"10"、"01"表示不允许PWM输出使能。

2 控制策略

2.1 无防错机制的PWM输出策略

在无PWM输出防错机制下,当PWM输出使能时,FPGA内部的计时器开始工作;内部计时器从0开始计数,当计数器的值等于周期值时重新归零计数;当计数器的值小于等于高电平时间的值时,PWM输出为高;当计数器的值大于高电平时间的值时,PWM输出为低,这样就生成了PWM波。

但是在PWM输出过程中,如果DSP突然对周期或高电平时间修改,可能产生如下问题:

1) 当计数器的值大于旧的高电平时间,小于最新的高电平时间时,当新的高电平时间更新后,原本已由高变低的波形,在该周期内将再次由低变高,在计数器达到新的高电平时间后,波形再次由高变低,这样实际占空比发生了错误;

2) 当计数器的值小于旧的高电平时间,大于新的高电平时间时,当新的高电平时间更新后,原本为高的波形将瞬间变为低,直至本次周期结束,这样实际占空比发生了错误;

3) 无论计数器的值运行至多少,当高电平时间不变,而周期值瞬间变化时,实际输出的PWM的波形的占空比发生了变化,发生了错误。

2.2 具备防错机制的PWM输出策略

图2 信号流图

在了解了不具备防错机制的PWM输出策略可能产生的原因后,对PWM输出的策略进行了修改,增加了周期及高电平时间缓存寄存器并择时刷新,作为PWM波发生的依据,而不直接使用EMIF总线写入的周期及高电平时间寄存器,具体的信号流图如图2所示,具体策略如下:

1) 当PWM波正在输出时,如果仅高电平时间发生了变化,此时FPGA将对新旧高电平时间进行对比,若计数器均小于两者,那么新的高电平时间将直接刷新缓存,参与PWM波的生成;若计数器均大于两者,或者介于两者之间时,那么新的高电平时间将在本次PWM周期结束后再刷新缓存,参与下一次的PWM波生成;

2) 当PWM波正在输出时,如果周期值发生了改变,新的周期值永远在本次PWM周期结束后再刷新缓存;

3) 当PWM输出不使能时,如果周期或高电平时间发生了变化,那么直接刷新缓存。

经过上述措施,可有效避免在参数瞬变的过程中导致PWM波形的输出错误。

3 结论

本文提出了一种基于FPGA的PWM防错输出控制电路,能够自由配置PWM输出的周期及占空比,且具备防错输出机制。经过实际测试,在基于FPGA的PWM输出电路基础上引入防错输出机制后,PWM输出因参数瞬变带来的错误输出现象消除,尤其在需要对PWM输出占空比监测的使用场景中,有效避免了占空比的突变。