数据链系统中高性能通信处理模块的设计与实现

2015-11-28韩振国

高 毅 韩振国 沈 华

(中航工业西安航空计算技术研究所,陕西 西安 710015)

数据链系统中高性能通信处理模块的设计与实现

高 毅 韩振国 沈 华

(中航工业西安航空计算技术研究所,陕西 西安 710015)

通信处理模块是某数据链系统中的关键模块,负责系统中通信数据的采集和处理。文章从数据链的发展趋势和需求出发,介绍了通信处理模块的设计和实现,着重介绍了基于FPGA的8路RS422信号接口的设计实现与测试。

数据链;通信处理;RS422;FPGA

1 引言

现代联合作战中,海陆空各作战单元之间要共享战场态势必须依靠数据链传送海量信息和指令,从而实现指控系统和武器系统间的无缝连接,达成真正意义上的联合作战行动。通信处理模块作为某型数据链系统的关键模块主要负责处理系统中各个功能模块间的RS422通信数据。

2 技术分析

数据链系统是现代高科技战争中获取信息协同作战的关键,通信处理模块作为某型数据链系统中的关键模块,负责处理系统中对外数据的通信,通信接口采用RS422串口通信协议,因其具有抗干扰能力强、通讯速率高、距离远的特点,在数据链系统中得以广泛应用。

2.1数据链的发展及需求

随着飞机、导弹、舰船等高机动武器的广泛应用,作战方式的改变,作战节奏的加快,单一的通讯方式已不能满足现代化战争的需要。数据链首先应用于地面防空和海军舰艇之间随后扩展至飞机,逐步实现了各军种之间的,从各种传感器到武力打击的闭环。某型数据链系统包含了雷达、短波通信、导航和战术话音通信等系统,各个系统通过RS422通信互联,因此系统需要一款处理功能强大,体积小,接口众多的通信处理模块来完成系统内各模块的数据信息采集和处理工作。

2.2RS422协议简介

RS422是一种常用的串口通信协议,通信只需要两条信号线(RXD、TXD)就可以完成接收与发送的全双工通信,其中TXD 是发送端,RXD 是接收端。信号线上有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。在发送器空闲时,数据线保持逻辑高电平状态,发送器通过起始位来开始一个字符的传送,起始位使数据线处于逻辑低电平状态,提示接收器数据开始传输,数据位一般为8 位一个字节的数(也有6 位、7 位的情况),低位( LSB)在前,高位(MSB)在后,校验位一般用来判断接收的数据位有无错误,一般是奇偶校验,停止位在最后,用以标志UART一个字符传送的结束,它对应于逻辑1 状态。

3 技术方案

3.1实现方式

传统RS422接口多采用总线协议芯片加总线收发器的形式,这种形式集成度低、成本高,越来越不适应航电系统小型化,轻量化,通用化的发展趋势。本文介绍的通信处理模块采用高性能处理器加大规模 FPGA的结构实现了 8路RS422信号的采集和处理,有效减小的系统规模,降低了系统功耗,深度可调的数据缓冲有效的提高了系统处理效率。

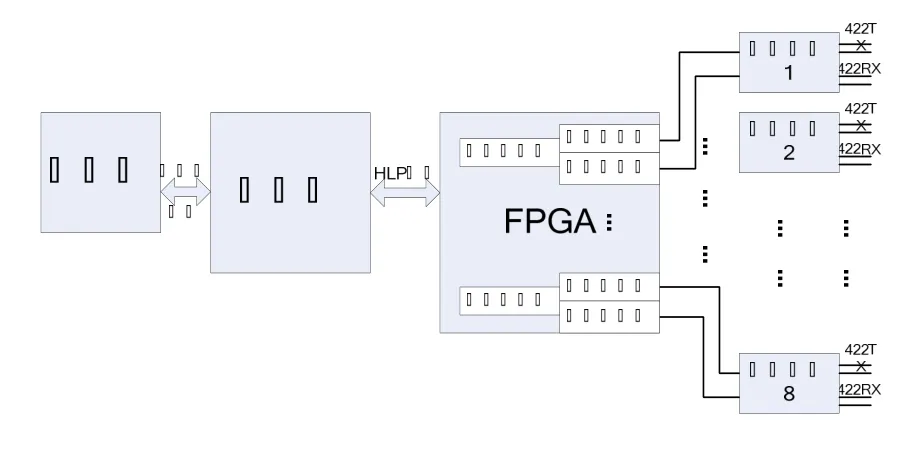

通信处理模块的基本功能框图如图 1所示,处理器实现422信号处理,通过处理器总线和桥接器连接;桥接器完成访问控制,通过HLP总线访问FPGA;FPGA通过逻辑实现8路标准RS422接口,线收发器完成信号转换。对开发层来说,只需配置FPGA寄存器值就可以实现对RS422接口的控制。

图1 RS422通信框图

3.1.1处理器选型

通信处理模块采用的处理器为MPC7447A,是PowerPC系列中的第四代高性能的处理器,主频设置为650MHz,集成高性能、超标量处理器;11个独立的执行单元和3组寄存器类;32kbytes 指令Cache和32kbytes数据Cache;32位或36位地址线,64位数据线;整型数据类型有 8, 16, 和 32 位;浮点数据类型有 32 和 64 位;完全可以满足数据链系统的处理需求。

3.1.2逻辑设计

FPGA内部资源丰富,通过FPGA实现RS422双异步端口电路功能及其控制可有效提高系统集成度,缩小体积,降低成本。

FPGA逻辑实现的 RS422异步端口电路功能等同于TL16C552芯片,但是通道数量达到8个,每个通道接收和发送FIFO达128B,在FIFO工作模式下,每个通道的接收发送FIFO深度可调节,从而减少CPU中断查询的频率,提高系统效率。波特率从9600bps到921.6kbps可设。

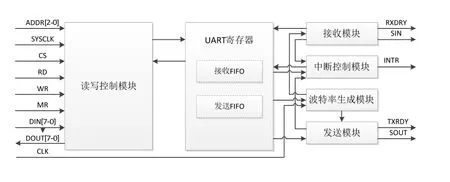

FPGA同时还实现对RS422 通道的访问控制,接收CPU的指令,对RS422通道进行初始化,将接收到的数据由CPU指定的通道输出,输出RS422中断信号,提醒CPU接收相应通道的总线数据。依据该设计原理,FPGA中提供了时钟发生模块、读写控制模块、寄存器模块、接收模块、发送模块、波特率生成模块、中断控制模块,各模块主要功能如下:

(1)读写控制模块负责实现与CPU的通讯,所有内部寄存器的读写都通过该模块完成。

(2)寄存器模块包括了本器件所有的内部寄存器。

(3)接收模块按照编程好的数据格式接收和检验串行数据的输入,数据将根据编程模式被置入接收缓冲寄存器或者接收FIFO中。

(4)发送模块负责发送写入发送保持寄存器或发送 FIFO的数据,它为待发送数据添加必要的起始位、校验位、停止位,这样接收设备就可以进行正确的接收和校验。

(5)波特率生成模块根据分频因子(从1到216-1)对波特率生成时钟分频,其结果将再被16分频以产生波特率。

(6)中断控制模块根据FIFO的状态和接收或发送的数据向处理器发出中断信号。中断标识寄存器将提供中断等级。

图2 RS422接口内部功能模块示意图

3.1.3收发器

SM3490是一款低功耗收发器,可用于RS-422 等串行数据接口标准系统中,内部有驱动和接收两个模块,与外部串行接口进行数据的传输,将外部的逻辑信号通过驱动器转化为差分信号,再由接收器中的比较器将接收的差分信号耦合到比较器的输入端,利用比较器将差分信号转换为单端的逻辑电平信号。

3.1.4中断控制

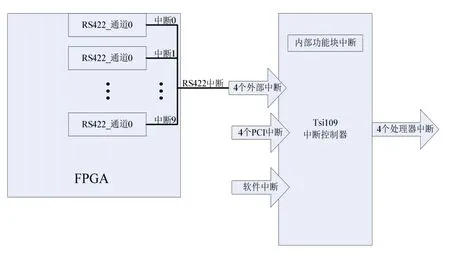

通信处理模块的中断控制主要由桥接器实现,桥接器采用TSI109,可以根据中断源的特点设置中断的优先级、电平有效方式及中断向量。中断的优先级可以通过软件进行设置。中断控制器示意图见图3。

中断控制器支持4个外部中断,4个PCI中断,软件中断和内部功能模块中断,FPGA实现的10路RS422产生一个中断输出挂接在Tsi109的外部中断上,经过中断控制器处理产生处理器中断。

图3 中断控制示意图

4 RS422通信测试

4.1接收数据分析

以接收RS422数据为例,讨论在8路RS422通道同时不间断接收数据的极端情况下,波特率不同时是否会发生数据丢失。

RS422的FIFO大小为128字节,通过设置FPGA寄存器可设置为收满108字节发送中断。HLP总线频率为133MHz,通信处理模块的HLP读周期设置为200ns,每次从FIFO中读一个字节需读一次状态寄存器,取光一路FIFO内的108字节需要43200ns。(200ns*108*2=43200s)

当RS422波特率为115200即115200bit/S时,收满108字节发送中断需要9375000ns(108*10/115200=9375000ns)。9375000ns远大于43200ns,由此可见从FIFO取数据要比收数据快的多。

假设8路RS422同时连续不断的接收数据,当一路FIFO收满 108字节发送中断后还可以接收 20字节数据(128-108=20),若在这20字节数据溢出之前处理器能收完其余 7路 FIFO内的数据则不会发生数据丢失。当波特率为115200时,装满20字节数据需1736000ns(20*10/115200),远大于取光7路FIFO的时间302400ns(43200*7=302400ns)。即当波特率为115200时,8路RS422同时接收数据,不会造成数据丢失。

同理,当波特率设置为460800时,FIFO收满108字节需要 0.002344000ns(108*10/460800=2344000ns),收满 20字节需要347200ns(20*10/460800=434000ns),取光7路FIFO需要302400ns,收满20字节的时间大于取光7路FIFO的时间,所以也不会造成数据丢失。

然而,当波特率为921600时,依照此算法就只能支持5路RS422同时连续接收数据。

4.2测试方法

RS422通信测试主要以三种方式进行,自环绕方式,多串口卡方式,外环方式。

FPGA内的RS422调制解调器控制器提供一个环绕自测试模式,可以对接收和发送通道进行简单测试。当调制解调器控制器的第四位被置位时,发送移位寄存器输出接到接收移位寄存器的输入端。调制解调器输出控制信号内部连接到调制解调器输入控制信号。在环绕自测试方式中,发送的数据立即被接收。通过这种方式CPU可以检查串行通道的发送和接收。

通过多串口卡加串口调试助手的测试方式可以排除RS422传输中电器性能和异步传输可能产生的问题。测试方法是,通过多串口卡接口1模拟一路RS422发送信号发往通信处理模块串口1;串口1接收到数据后再将接收到的数据通过串口2发送回多串口卡接口2,比较接口1和接口2的数据,确认RS422通信收发正常。分别设置波特率为9600,115200,460800,通信处理模块都能正常工作。

外环测试可以充分模拟用户在使用中多串口大数据量传输的情况,测试方式是将每一路串口的收发短接,编写测试程序进行循环收发测试,设置波特率从9600到460800,通信处理模块可正常工作。

5 小结

本文介绍了数据链系统中通信处理模块的设计和实现,重点讨论了基于FPGA的8路RS422信号的实现和测试。用FPGA实现数据通信,能够减小系统规模,降低系统功耗,同时可调节大小的 FIFO也有效提高了处理效率避免了数据丢失。通信处理模块已成功应用于某海陆空数据链系统。

[1] 李肇庆,韩涛.串行端口技术[M].北京:国防工业出版社, 2004.

[2] 江思敏.VHDL 数字电路及系统设计[M].北京:机械工业出版社,2006.

[3] 刘璞,王春平,徐艳.基于 FPGA 的串口与链路口联合通信设计与实现[J].计算机测量与控制,2014,22(2):903-913.

Design and implementation of high-performance communications processor module in Data Link system

High-performance communications processor module collects and processes communication data, it is the key module in Data Link system. This paper, starting with the development tendency and requirement of Data Link, describes the design and implementation of high-performance communication processor module, and puts emphasis on the implementation of 8 channel RS422 interface on FPGA.

Data Link;communications processor;RS422;FPGA

TN911

A

1008-1151(2015)10-0001-03

2015-09-11

高毅,供职于中航工业西安航空计算技术研究所,研究方向为计算机系统结构。