UART 波特率检测电路的FPGA 设计算法与实现

2022-10-15吴朝晖曲立国

吴朝晖,曲立国

(安徽师范大学 物理与电子信息学院,安徽 芜湖 241000)

0 引 言

通用异步接收发送器(UART)是最常用的异步通信时钟的串行通信方式,使用时通信双方需要设置相同的波特率、数据位、校验位、停止位等参数。波特率发生器是UART 接口电路中的重要组成部分,它用于产生接收和发送信号时所需的时钟信号。

近年来,出现了一种自适应波特率发生器,可以检测信号发送方的通信波特率,然后产生相应的波特率。这种自适应的波特率发生器设计方法主要有硬件法和软件法。其中用FPGA 硬件实现的方法主要体现在:方案1 特征值匹配法,要求发送方发送特定的数据帧,比如0x55,0xAA 或0x00,然后检测脉冲周期,算出波特率;方案2 要求发送方在发送第1 个数据时,确保其第1 位码元为1;方案3 不要求特定数据,不断检测时间间隔,找到最小的时间间隔作为计算波特率的依据。方案1,2 都要求特定数据帧,而方案3 得出的最小时间间隔不一定就是实际最小的时间间隔。

本文首先分析所有可能的信号波形,得到每种波形特征参数并进行分类;再基于FPGA 设计出波特率检测电路,遇到可确定唯一的波特率的波形,就根据脉宽计算出波特率,否则可以忽略等待下一个波形。

1 波形特征分析

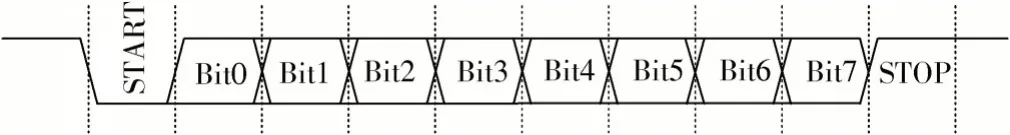

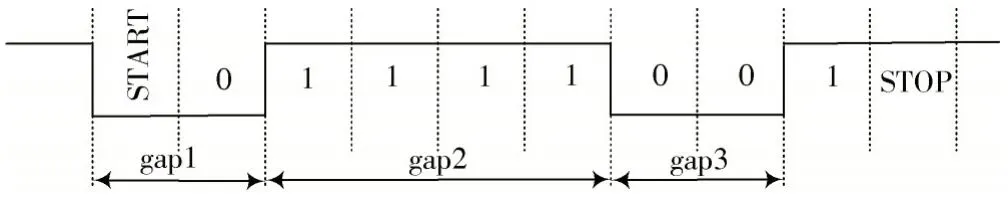

为了进行波形分析,假设通信时一帧数据由1 位起始位、8 位数据位、1 位停止位共计10 个数据位构成,其中数据位的低位在前,高位在后。UART 信号波形如图1 所示。

图1 UART 信号波形

1.1 波形特征参数

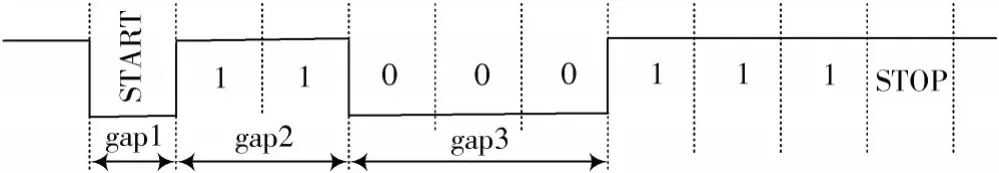

8 个数据位共有256 种不同的信号波形。波形的上升沿与下降沿之间的时间间隔(gap)等于1 个或多个位(bit)周期。每个波形都有确定的间隔数(gaps)和各个间隔宽度比例(gap ratio),这两个参数是波形的特征参数。例如数据“0xE3”的信号波形含有3 个时间间隔(3 gaps),各时间间隔宽度比例为1∶2∶3。波形图如图2所示。这个信号的波形特征是唯一的,最小时间间隔是间隔1(gap1),其宽度就是一个bit 位的宽度,根椐宽度就可计算出波特率。

图2 数据“0xE3”的信号波形

1.2 无法确定波特率的波形

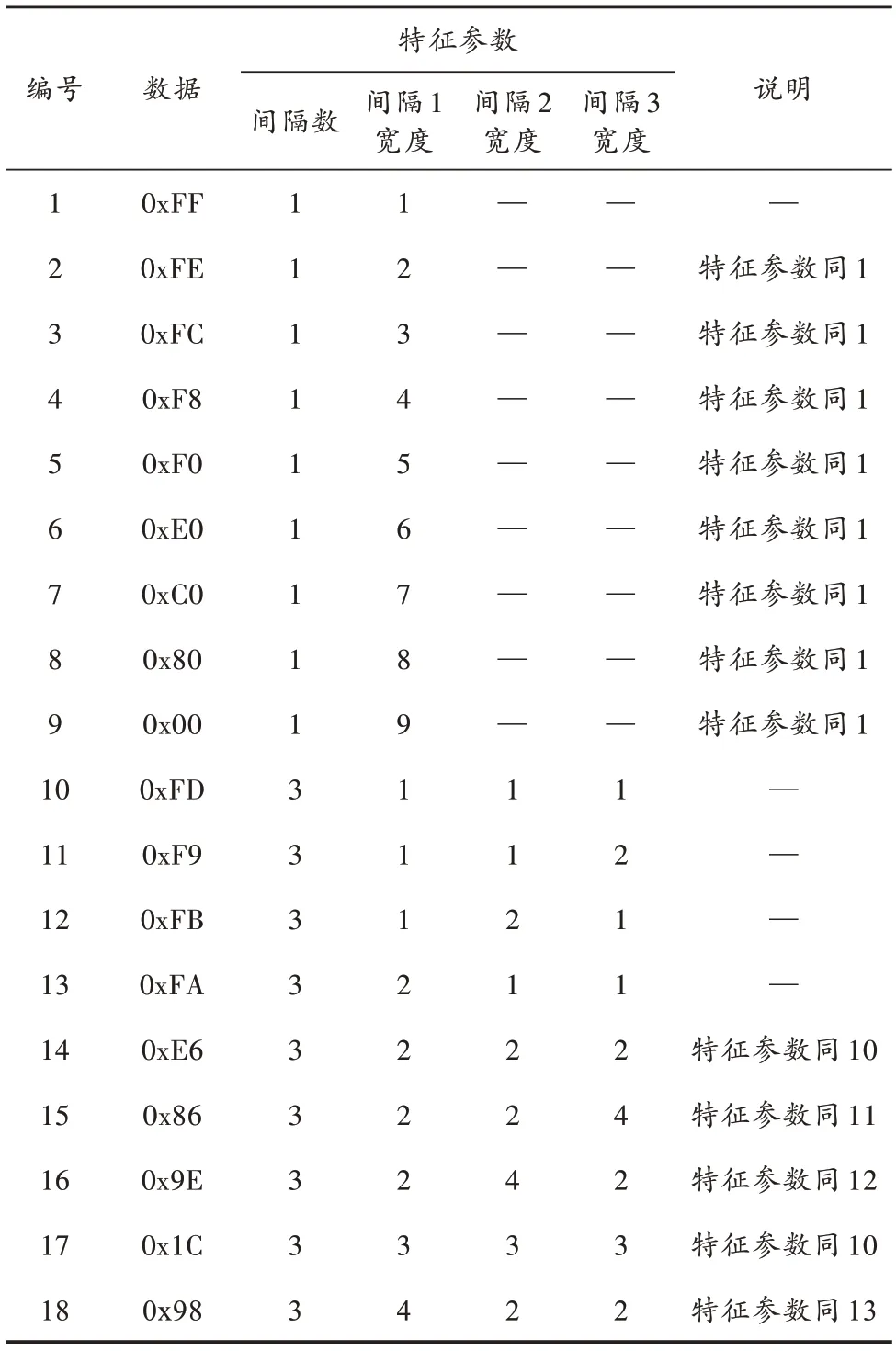

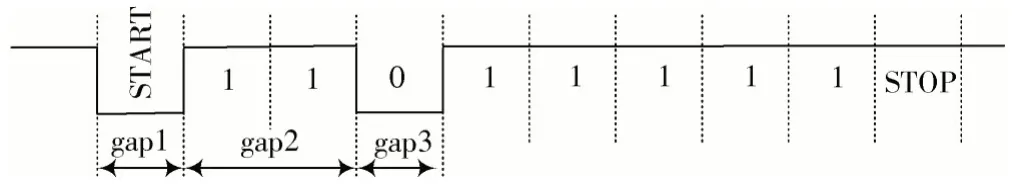

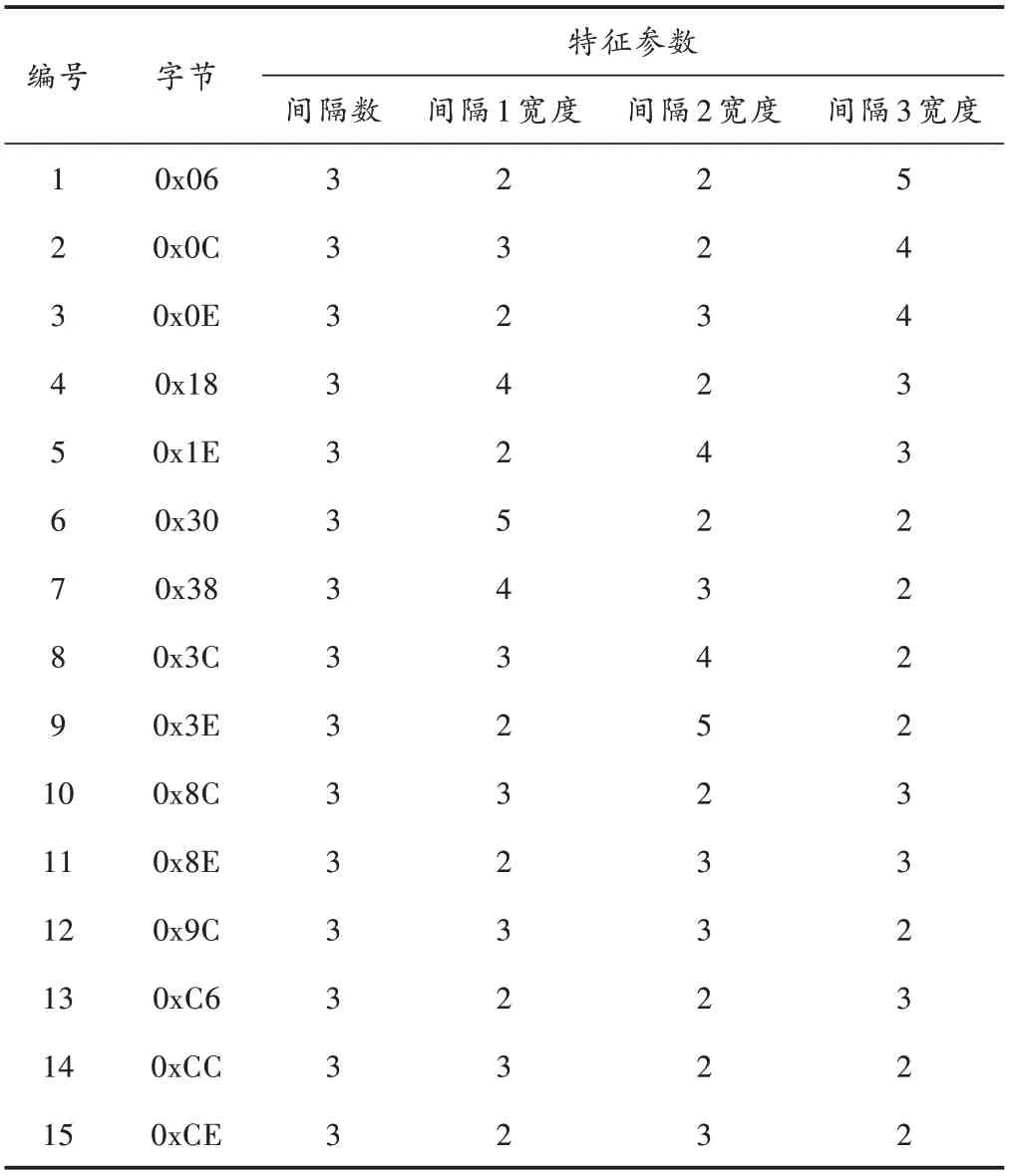

并非所有数据的信号波形都是唯一的,例如:数据“0xFB”和“0x9E”的波形都含有3 个时间间隔数,如图3和图4 所示。“0xFB”的波形间隔宽度比例都是1∶2∶1,“0x9E”的波形间隔宽度比例为2∶4∶2,化简后也是1∶2∶1,因此2 个波形看起来是相似的,特征参数完全相同,无法区分。按最小宽度计算的波特率可能是正确的,也可能是实际波特率的1/ 2。计算结果表明,在256个数据中,有18 个数据波形特征参数不唯一,无法确定唯一的波特率,见表1,占比约为7.03%。其波形特征又分两种情况:

表1 特征参数不唯一的信号

图3 数据“0xFB”的信号波形

图4 数据“0x9E”的信号波形

1)间隔数为1 时,有9 种情况,波形都相似,特征参数全部相同,无法区分。

2)间隔数为3 时,也有9 种情况,化简后有4 种比例关系,分别是1∶1∶1,1∶2∶1,1∶1∶2 和2∶1∶1。由于存在不同数据对应相同的间隔宽度比例,特征参数相同,无法区分。

1.3 可确定波特率的波形及波特率计算

除了前面的18 个数据之外,其他238 个数据都具有唯一的特征参数,即可以确定唯一的波特率,间隔数分别为3,5,7,9。可分两种情况:

1)间隔数为5,7,9 的波形,特征参数都是唯一的,并且由最小时间间隔宽度决定其波特率。比如数据“0x7B”,时间间隔数为5,时间间隔宽度的比例为1∶2∶1∶4∶1。其最小间隔宽度就是1 bit 宽度,此宽度可决定波特率。

2)间隔数为3 的波形,除去前面所说的9 种无法确定唯一的波特率的波形外,还有15 种波形的间隔宽度的最小比例为2,在计算这些波形的波特率时,应将最小间隔宽度减小1/ 2,具体数据如表2 所示。

表2 特征参数唯一,但计算波特率时宽度要减小1/ 2 的数据

对于256 种可能的数据波形,其波形特征由间隔数(gaps)和间隔宽度比例(gap ratio)两个参数决定。而间隔数只有1,3,5,7,9 五种可能,可分为以下3 类:

1)间隔数为1 的,有9 种相同波形,无法确定波特率。

2)间隔数为5,7,9 的,有163 种不同波形,其波特率由最小间隔宽度决定。

3)间隔数为3 的,有84 种波形,分3 种情况:9 种波形无法确定波特率;60 种波形的波特率由最小间隔宽度决定;而另外15 种波形则要将最小间隔宽度减半才能得到正确的波特率。

2 算法设计及FPGA 实现

本设计采用Verilog HDL 语言建模编程实现对通信发送方的信号波特率的检测,并用FPGA 芯片实现。首先需要根据通信发送方的波形提取2 个重要特征参数,即间隔数(gaps)和各间隔宽度比例(gap ratio);然后根据波形特征识别出18 种无法确定的波特率和15 种需要将最小间隔宽度减小1/ 2 才能正确计算波特率的波形。

2.1 边沿检测电路设计

利用快速的clk信号(比如50 MHz)对信号进行整形,利用两级D 触发器可消除亚稳态;再通过两级D 触发器,获取2次时钟的采样值,判断上升沿与下降沿。部分源码如下:

…

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

tmp0_Rx <=1′b0;tmp1_Rx <=1′b0;

end

else begin

tmp0_Rx <= s1_Rx;tmp1_Rx <= tmp0_Rx;

end

assign nedge=!tmp0_Rx && tmp1_Rx; //检测上升沿

assign pedge= tmp0_Rx && !tmp1_Rx; //检测下降沿

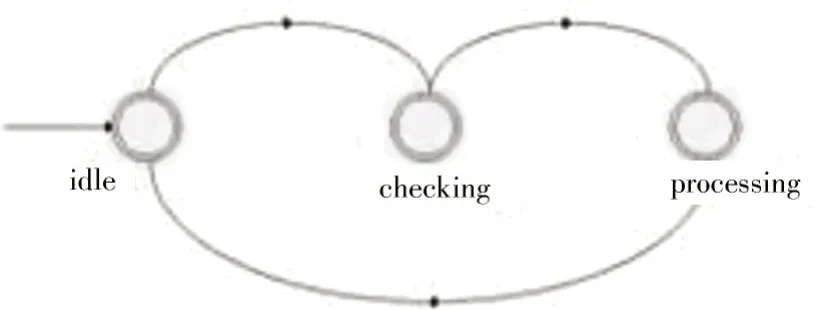

2.2 有限状态机

电路按有限状态机设计,分为空闲状态(idle)、信号检测状态(checking)和数据处理状态(processing)。状态转换图如图5 所示。

图5 状态转换图

1)在空闲状态(idle),信号为初始化状态。信号脉冲宽度计数(gap[10:0])清零,时钟计数(clk_cnt)清零,信号边沿计数(edges)置1。一旦检测到信号上升沿或下降沿,即进入信号检测状态。部分源码如下:

gap[0]<=22′b0;

…

gap[10]<=22′b0;

clk_cnt=22′b0;

edges<=4′b1;

if(pedge||nedge)state<=checking;

2)在信号检测状态(checking),每次时钟上升沿到来时,信号脉冲宽度计数值(gap[edges])递增。如果检测到上升沿或下降沿(nedge||pedge),信号边沿计数值(edges)递增,同时记录最小信号脉冲宽度(min_gap)。部分源码如下:

if(nedge||pedge)edges<=edges+4′b1;

gap[edges]<=gap[edges]+22′b1;

if(edges==2) min_gap=gap[edges-1];

else if(edges>2 && gap[edges-1] min_gap=gap[edges-1]; clk_cnt=clk_cnt+22′b1; if(clk_cnt>min_gap*10 && edges>1) state<=processing; 3)在数据处理状态(processing),根据边沿数(edges)和信号脉冲宽度计数值(gap[edges]),判断是否可计算出波特率(chk_ok)。部分源码如下: chk_ok=1′b1; if(edges==2||edges==0) chk_ok=1′b0; else if(edges==4) begin if(equals(gap[1],gap[2],1))begin if(equals(gap[1],gap[3],1)) chk_ok=1′b0; else if(equals(gap[3],gap[1],2)) chk_ok=1′ b0; end else if(equals(gap[1],gap[3],1)) if(equals(gap[2],gap[1],2)) chk_ok=1′b0; else if(equals(gap[2],gap[3],1)) if(equals(gap[1],gap[2],2)) chk_ok=1′b0; end 2.3 计算波特率 另外,还有辅助进程,用于判断是否将最小信号脉冲宽度除以2(div)等。部分源码如下: if(div) Baud<=(50 000 000/min_gap)<<1; else Baud<=50 000 000/min_gap; 使用Quartus 13.1 开发工具和相应的ModelSim 仿真器对电路进行仿真,如图6 所示。 图6 波特率检测的仿真 仿真时采用时钟clk 为50 MHz 方波,输入各种不同信号,信号RxD 的波特率为9 600,38 400,115 200 等,对于可以判断波特率的信号,均可计算出正确的波特率,其中chk_ok 是检测成功的标志。利用内置ALTERA公司EP4CE10F17C8 芯片的FPGA 开发板进行下载验证,通过串口调试助手发送不同波特率的信号,显示并设置波特率,与预想的一致。 根据UART通信发送方发送的特征,约7%的信号无法正确识别,处理方法是忽略并继续等待。约93%的信号可以准确计算出波特率,识别并进行设置,同时发送检测成功标志。本文只针对最通用的信号进行分析(即1 帧数据由1 位起始位、8 位数据位、1 位停止位组成),有一定的局限性,对于其他情况还需对算法进行修改。3 仿真与实现

4 结 语