固态硬盘性能优化研究与实现

2015-04-14罗桂娥

罗桂娥,康 霞

中南大学 信息科学与工程学院,长沙 410083

1 引言

随着计算机的普及及其处理问题复杂程度的增加,人们对计算机的存储容量、存储速度以及存储数据的完整性和灵活性提出了更高的要求。目前市场上比较普遍的存储设备为传统的机械硬盘、U盘以及固态硬盘。传统的机械硬盘由于自身固有的特性,还存在诸如存储速度慢,不稳定,体积大和功耗大等缺点[1]。U盘虽然小巧轻便,但是其可扩展性差[2]。固态硬盘是采用闪存芯片构成的块存储设备,由于内部不需要机械硬盘那样的机械结构等,在读写性能、能耗、尺寸、存储容量等方面有着明显的优势[3]。

硬盘接口是计算机硬件架构的一个重要组成部分,与传统基于并行接口的硬盘相比,SATA接口具有优异的电气特性和传输速度[4]。其主要优点如下:(1)有效解决了串扰问题;(2)带宽增加;(3)具有热插拔的性能;(4)精确性高;(5)工作电压降低;(6)向上与并行接口兼容。因而SATA接口成为目前硬盘接口的主流。

基于闪存的固态硬盘具有高性能、低功耗等诸多优点,因而迅速得到了学术界以及工业界的重视。国内外先后涌现了很多的固态硬盘生产厂商,国外厂商如希捷等,国内如源科等。目前市面上也能看到很多基于SATA2.0、SATA3.0的固态硬盘产品。但是目前国内对于固态硬盘技术的研究还不成熟,具有自主知识产权的比较少,同时,由于固态硬盘的主控芯片以及Flash存储介质的选型不一样,固态硬盘的性能也有所区别,因此开发出具有自主知识产权,性价比又比较高的固态硬盘产品具有重要意义。

基于以上背景,设计了一种基于SATA3.0接口的多通道并行架构的固态硬盘存储系统,以FPGA芯片XC5VFX130T为核心,采用高速并行的硬件架构,结合先进的软件调度算法,对固态硬盘存储系统的实现及速度优化进行了研究。优化后的实验结果表明,该系统具有存储速度快,并行性和扩展性强等特点。

2 固态硬盘相关技术分析

2.1 SATA协议的体系结构

在此设计中,固态硬盘存储系统采用的是基于SATA3.0协议的硬盘存储接口。SATA3.0体系结构共分为4层:应用层、传输层、链路层和物理层[5]。其中应用层主要负责ATA(Advanced Technology Attachment)命令的解析和对控制命令寄存器的访问;传输层主要负责组装与解析帧;数据链路层通过维持数据的完整性来保证数据包通过链路可靠地传输;物理层包含串行器/解串行器,提供OOB(Out of Band)带外号并处理加电顺序和速度协商[6]。

2.2 NAND Flash存储特性分析

NOR和NAND是现在市场上两种主要的非易失性存储技术[3]。其中NOR闪存主要用来存储少量的代码以及需要多次擦写的场合,而NAND则是海量数据存储密度的理想解决方案,设计中采用基于NAND的闪存技术[7]。NAND Flash存储介质由多个存储面(Plane)组成,其中每个存储面又由多个存储块(Block)组成,而每个存储块又可以分成一定数量的存储页(Page)。每个存储页中包含了相应的数据、ECC信息[8]。存储过程中对Flash共有读、写和擦除3种操作,其中“块”是擦除操作的基本单位,“页”是读写操作的基本单位。每个块的擦除次数有限,当超过擦除次数后,存储块上的数据将变得不可靠。与传统的磁盘存储器不同之处是NAND Flash不支持定点更新,即一个存储页被写入过数据后,它只有在进行了擦除操作后才能再次写入新的数据,这个特点称为写前擦除[9]。NAND Flash的这种存储特性使得其不能像磁盘存储器一样被传统文件系统直接使用,需要设计专门的控制器。同时,为了能访问闪存的数据,固态硬盘中存在一个闪存转换层(Flash Translation Layer,FTL),用于实现上层文件系统逻辑地址到物理地址的转换[10]以及对闪存进行相应的管理。

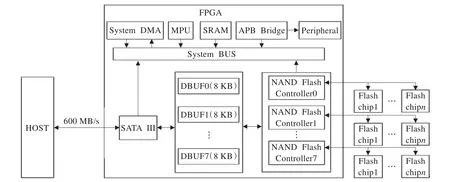

图1 固态硬盘存储系统架构图

3 固态硬盘系统设计

3.1 系统硬件的基本构架

存储系统的访问速度是存储系统的重要性能指标,提高SSD(Solid State Disk)的速度对于整个系统具有重要的意义。良好的硬件架构能为系统速度的高速要求奠定基础,固态硬盘主要由固态硬盘控制器和存储单元构成[11]。本文对基于SATA3.0接口的固态硬盘存储系统进行了设计,并且以Flash[12]作为主要的存储介质。根据SATA3.0协议标准,硬盘接口的速度能达到600 MB/s[6],但由于单片NAND Flash的访问速度比较慢,两者之间速度不匹配。所以,如何保证SATA与NAND之间的速度匹配是系统架构设计的核心所在,系统的总体构架如图1所示。

从图1分析可知,系统主要由SATA接口、FPGA和Flash芯片阵列构成。其中FPGA内部集成了ARM、SATA控制器、NAND控制器、DMA控制器、DBUF(Data Buffer)、SRAM以及通过系统总线进行内部模块的连接[13],在APB总线上挂了一些常用的外部设备,如GPIO等。其中,SATA接口的作用是实现与主机互联,有效地保证主机设备间的通信效率;ARM的作用是对整个系统进行管理,包括工作模式管理和文件系统管理;FPGA的作用是实现ARM、SATA和FLASH芯片阵列之间的逻辑接口转换,并对FLASH阵列进行数据读写。

3.2 系统构架的核心技术分析

在固态硬盘存储系统中,实现主机与存储单元Flash之间的通信是系统最主要的任务。其通信过程主要分为两个步骤:第一,主机设备间通过高速数据接口进行数据传输;第二,系统与NAND Flash芯片之间通过NAND Flash接口进行数据传输。硬件架构主要通过以下几个方面的技术来高效的实现上述任务:

(1)多通道NAND Flash的并行流水机制接口与有效配置DBUF相结合的方法。其中,NAND控制器内置DMA和可配置的ECC。在系统架构中,共有8个NAND Flash控制器和外接的Flash芯片一起组成8路NAND Flash访问通道,每个通道上的NAND Flash共享一条I/O总线,各个控制器能独立工作。采用8通道并行操作方法,能将数据总线的带宽扩展到单个通道带宽的8倍,实现了数据宏观上的并行操作。同时,为了满足用户对存储容量的需求,对其扩展性进行了设计,每个通道上能挂多片Flash芯片,因而能设计出不同容量的固态硬盘。

(2)针对NAND Flash读写访问操作不同的特点,设计中加入了DBUF作为缓存。设计中的DBUF有独立的寻址空间,这样SATA以及NAND控制器通过DMA进行数据传输时,能有效地进行动态地址映射,同时,也减轻了系统管理数据的复杂度。设计中的DBUF的个数为8个,能有效利用乒乓缓冲策略。以主机对设备发出写请求为例,由于SATA接口的数据传输速度高于NAND Flash接口的数据存取速度,当NAND控制器对DBUF0进行访问时,SATA能对DBUF1进行数据传输,这样当NAND控制器将DBUF0的数据读完之后,DBUF0空闲,SATA能重新对DBUF0进行访问,提高了主机与系统之间数据传输的并行度。此外,在主机发送读数据请求时,NAND控制器内部的DMA具有灵活性,为了减少控制器缓存到DBUF之间的数据传输时间,可以跳过DBUF而直接将数据传送给SATA,同时,若NAND给出的数据量足够大的情况下,而SATA来不及对所有的数据进行处理时,也能通过DBUF缓存来保证数据传输的连续性以及准确性,提高了系统硬件资源的利用率。

(3)在系统功能设计过程中,由于主机设备间接口标准速度为600 MB/s,所以对主控芯片的时钟频率要求比较高,因而系统内部MPU模块采用ARM9,它能支持的频率最大能达到400 MHz。实际设置MPU的时钟频率为300 MHz,系统内部总线时钟为150 MHz,根据系统的硬件架构,8DBUF以及8NAND控制器的理论频率能达到1 200 MHz,从而能满足SATA3.0的接口速度需求。若从系统的成本出发,即使系统采用4通道架构,缓存以及NAND接口理论并行时钟频率为600 MHz,也能满足系统内部速度的匹配。但是在实际FPGA的实现过程中,由于系统内部的时序约束等要求,实测频率大约为理论频率的80%左右。

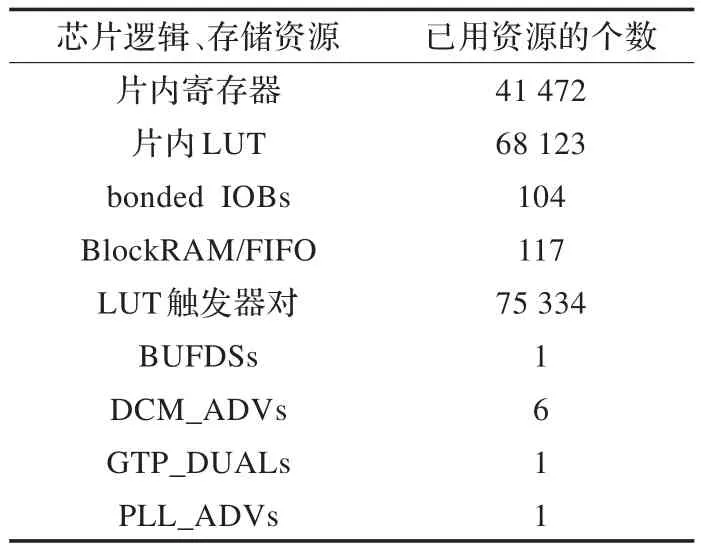

根据上述分析,在4通道架构下,给出了在Xilinx ISE环境下的FPGA主要的逻辑资源以及存储资源的分布如表1所示。从表1中可以看出FPGA内部的主要逻辑资源片内LUT的已用个数为68 123个(LUT为6输入),LUT触发对的已用数目为75 334个,主要实现信号同步和锁存;主要的存储资源寄存器的已用个数为41 472个以及FIFO的已用个数为117;BUFDS主要用来实现门控时钟和划分时钟树,其中高速收发口为SATA接口。

表1 FPGA内部主要资源使用分布图

4 固态硬盘系统速度分析与优化

固态硬盘存储系统是一个高度集成的嵌入式系统,不仅需要处理器和接口等基本硬件,而且还需要完备的系统控制软件[14]。系统控制软件主要负责以下几个功能:系统初始化,处理来自SATA接口的命令,控制存储系统内命令队列机制,控制数据并行传输,维护闪存地址映射表等。图1的硬件架构具备的高速并行存储的能力奠定了良好的硬件基础,下面将从系统控制软件的角度上分析并优化系统的性能。

4.1 系统速度分析

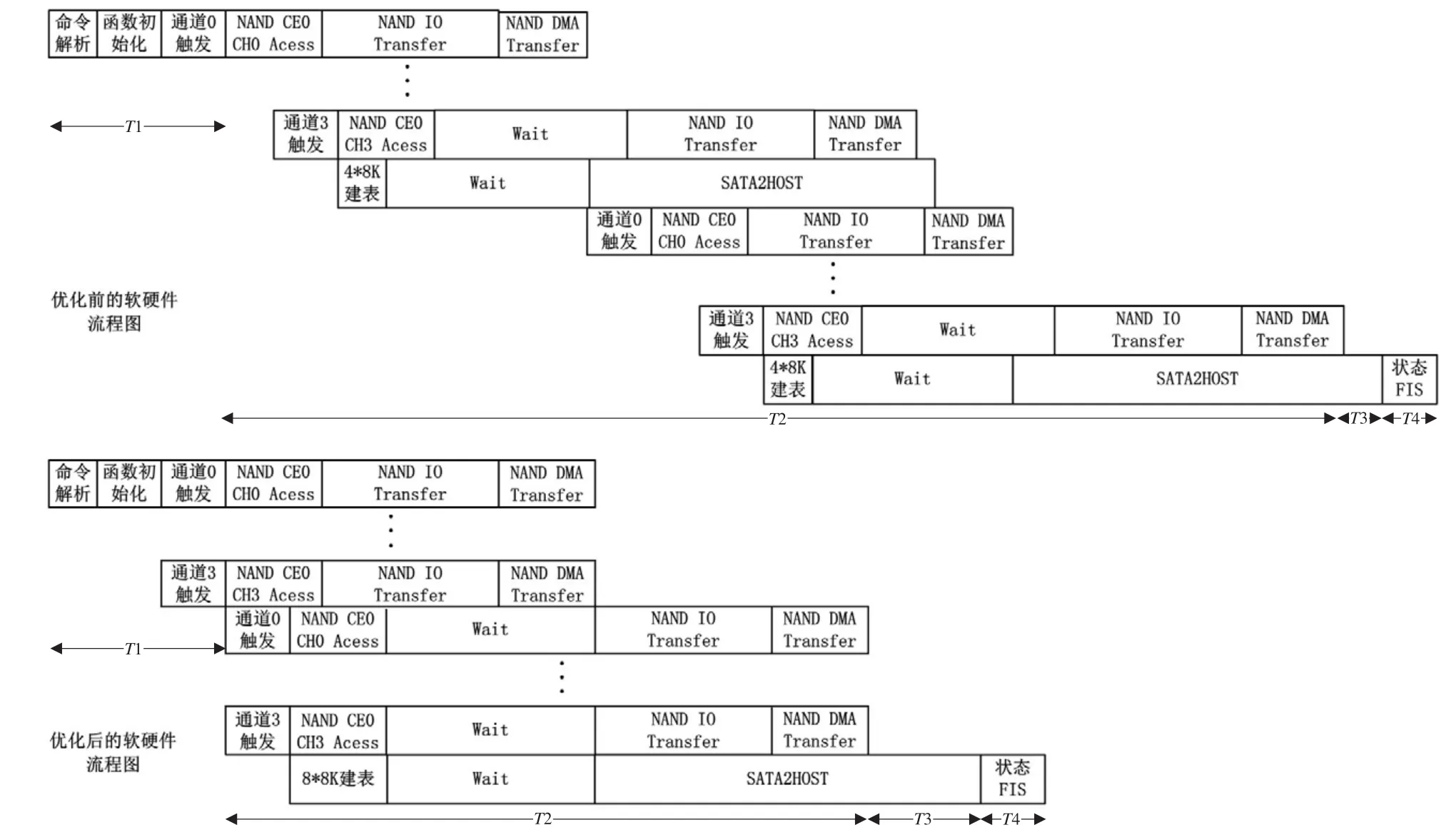

系统速度的影响因子主要是存储容量与系统时间,其中,系统时间包含软硬件处理时间。因此,如何提高单位时间内数据的吞吐量,以及在主机一次命令传输数据大小不变的情况下减少系统时间,能有效地提高系统的读写效率。为了充分体现NAND Flash的并行流水机制,设计分析系统速度时,以NAND Flash采用4通道2CE(Chip Enable)构架为例来分析系统的软硬件工作流程。在HOST一次DMA Read Command[15]命令处理64 KB数据时,从图1的多通道并行架构角度出发,得到优化前后系统的软硬件流程图如图2所示。

从图2可以看出,系统的总体任务主要分为以下几个部分:对主机发来的读命令进行命名解析,函数初始化,触发NAND通道,FTL建表,通过SATA接口往主机传输数据。同时,通过分析可以看出优化前后的流程的区别:(1)优化后流程比较简单,减少了控制流程的复杂度;(2)优化后采用超级页进行传输,因而在传输数据时间不变的情况下大大增加数据的吞吐量;(3)对系统的任务调度的优先级不一样,优化后先进行通道触发后建立FTL表,这样NAND Flash能提前准备数据,隐藏了NAND Access的时间;(4)优化后充分利用了NAND之间的并发与流水机制。

图2 SSD系统4通道2CE优化前后软硬件流程图

在图2中,多处采用时间隐藏机制,充分利用系统的软硬件资源,减少系统时间,提高了系统的性能。同时,根据传输的过程中出现的针对连续地址读取数据时LBA(Logical Base Address)中存在地址偏移的情况,设计采取了数据补偿策略。即CPU第一次触发NAND 4个通道时的实际读取数据少于32 KB,为了满足主机DMA Read Command[16]需要的64 KB,此时CPU必须进行3次触发操作,从而大大延长了系统时间。设计中采用数据补偿法,在读取少于8 KB数据的地址时,将少于8 KB数据的这页先放在DBUF中进行等待,与读取最后一页的数据构成8 KB数据才开始往SATA传输。这样只是主机的第一次命令数据传输时间较长,对文件数据大小大于64 KB的系统时间不会产生大的影响,避免了由于地址偏移造成NAND通道的浪费,提高了系统的速度,也有效地减少了系统的成本。同时,在实际操作过程中可对数据进行预取,即假设数据量大于64 KB,提前对NAND通道进触发,而将T1与T3的时间隐藏在下次命令中,因而系统实际消耗的时间只有T2,实现了软硬件的最佳平衡。

此外,将时间进行细化分析,还可以从以下几个方面进行改进提高整体性能:(1)提高系统时钟;(2)增加NAND通道数;(3)选择支持同步模式的Flash芯片与NAND控制器,从而优化NAND IO时间;(4)优化ECC;(5)NAND采用多级流水,比如采用 Read Page Multi-plane命令等;(6)优化软件时间,比如说优化FTL算法等,因为FTL算法的优劣直接决定了系统的开销和性能,也决定了整个固态存储系统的使用寿命[17]。

4.2 速度优化实验结果对比与分析

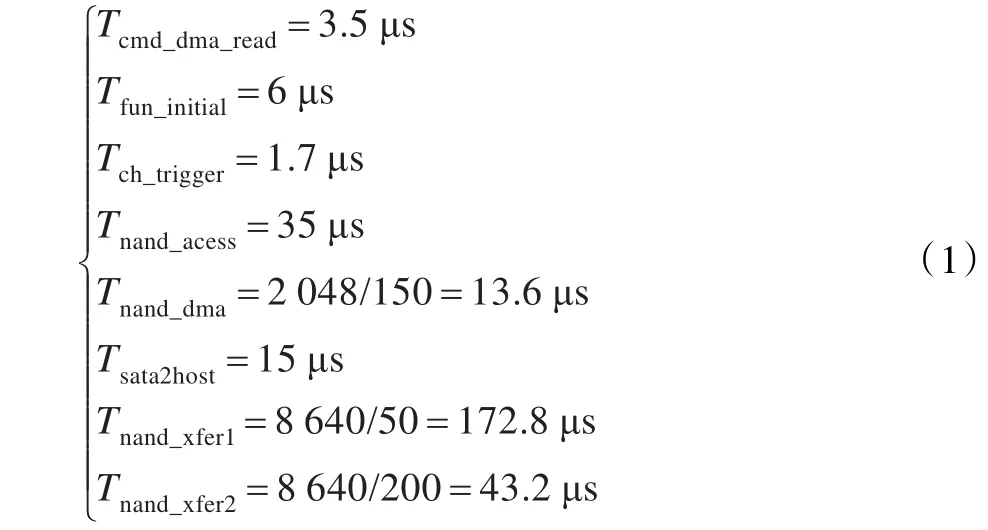

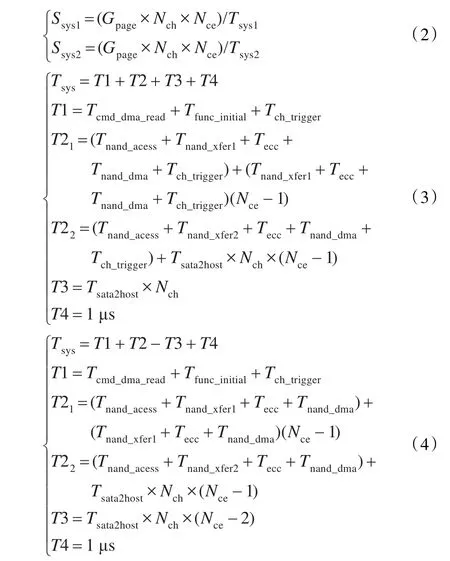

根据以上分析以及改进方法,假设命令解析时间、函数初始化时间、通道触发时间分别为Tcmd_dma_read、Tfunc_initial和Tch_trigger;Nce表示NAND CE数,Nch表示NAND通道数;Tsata2host表示数据从SATA接口传输到主机的时间;Tnand_acess为NAND传输数据的准备时间,Tecc为ECC校验时间以及Tnand_dma为DMA传输时间,Tnand_xfer1,Tnand_xfer2为NAND工作在异步与ONFI(Open Nand Flash Interface)模式下NAND IO的传输时间;Tsys1,Tsys2与Ssys1,Ssys2表示不同模式下的SSD系统总的消耗时间以及主机发一次命令的系统读速度。

根据图1的系统硬件架构以及图2的软硬件工作流程,在主机一次DMA Read命令取64 KB数据,且NAND采用4通道2CE,Flash芯片采用MT29F32G08ABCAB,并设置Flash的每页大小为8 KB,当NAND Flash分别工作在异步模式与ONFI模式时,即设NAND的IO时钟分别为50 MHz与200 MHz。结合软硬件测试,得到系统参数的大小如下:

在NAND工作在同样模式的前提下,系统主要采取的优化方法为:数据补偿策略,数据预取,利用超级页进行传输。根据以上分析可以得到NAND不同工作模式下系统速度为式(2),以及优化前后的系统总体消耗时间为式(3)和式(4):

其中Gpage表示NAND每个page的大小,Nch取1,2,3,4以及Nce取1,2。在异步模式下T2取T21,Tsys取Tsys1;ONFI模式下T2取T22,Tsys的值为Tsys2。从式(3)和式(4)中可以看出优化前后的对系统速度的不同算法,主要是为了减少系统总时间,优化了参数T2和T3。同时,将式(1)代入式(2)、式(3)、式(4),得到式(5)、式(6)如下:

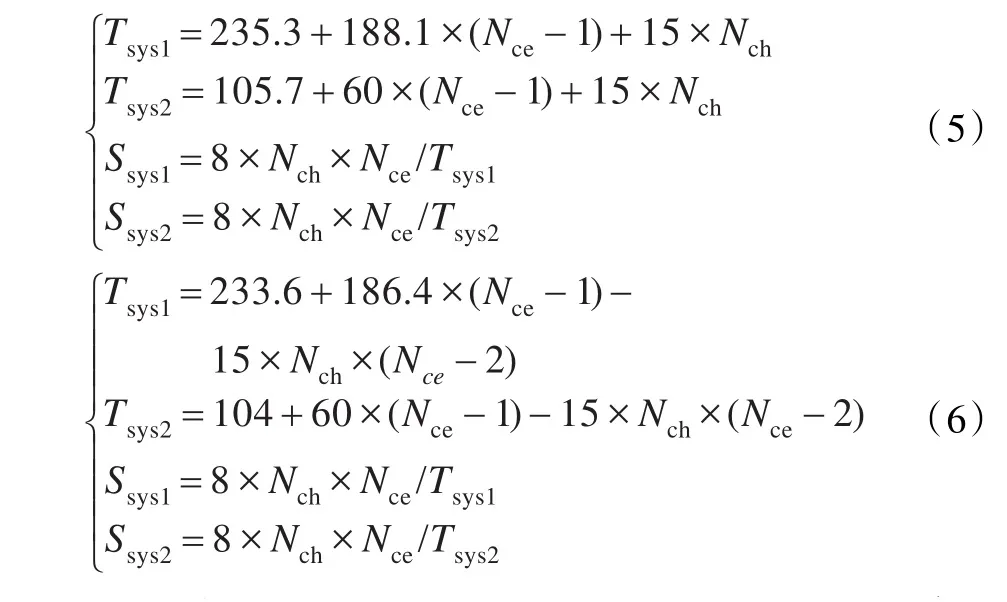

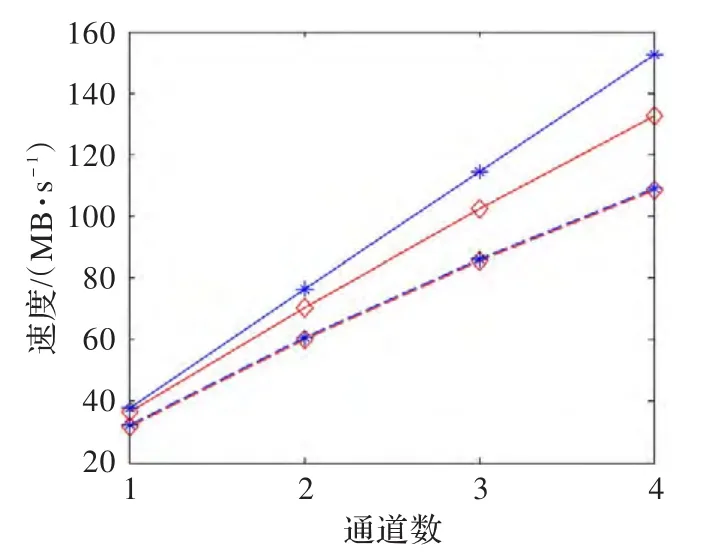

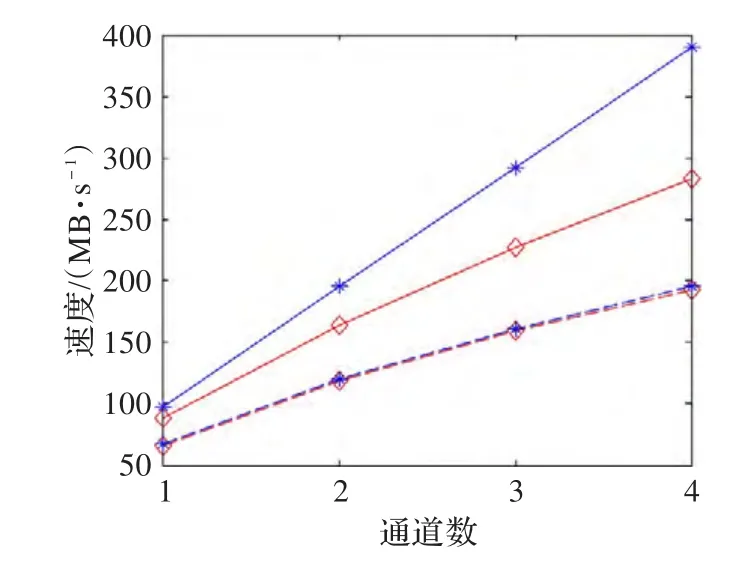

将参数Nch、Nce的值分别代入式(5)和式(6)可以得到SSD读速度,根据算出来的值画出SSD读速度图如图3与图4所示。

图3 异步模式下优化前后的SSD读速度

图4 同步模式下优化前后的SSD读速度

从图3与图4中可以看出:(1)在CE数为2时,优化前后的速度明显,因为这时候对数据进行预取,将T3时间进行了隐藏,CE数为1时,数据量少,只是隐藏了通道触发时间,因而优化效果不是很明显。(2)在CE数不变的情况下,增加NAND通道数大大提高了系统的速度;同时通过图3和图4对比可以看出支持ONFI模式下的SSD速度基本是异步模式下的2倍。(3)在异步模式,传输数据量大小为64 KB,即NAND CE数为2,通道数为4时,通过计算优化后速度相对于优化前提高了15%,ONFI模式提高了38.8%。

5 系统功能与性能测试

5.1 功能测试

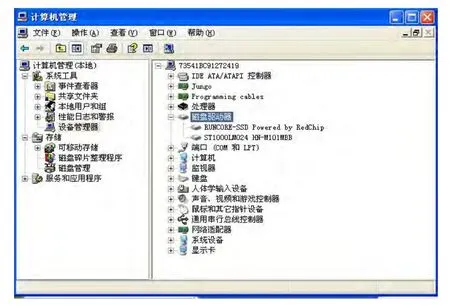

固态硬盘存储系统的功能测试是测试固态硬盘能否被主机的主板正常识别。在各种操作系统下对硬盘进行测试,分别通过硬盘识别,对硬盘进行读写数据操作以及通过文件系统对文件进行建立、修改、保存和删除操作来验证固态硬盘的功能。在WINDOWS XP系统下对固态硬盘进行测试,测试结果的识盘图如图5所示,测试结果表明,固态硬盘工作正常。

5.2 性能测试

图5 固态硬盘识盘图

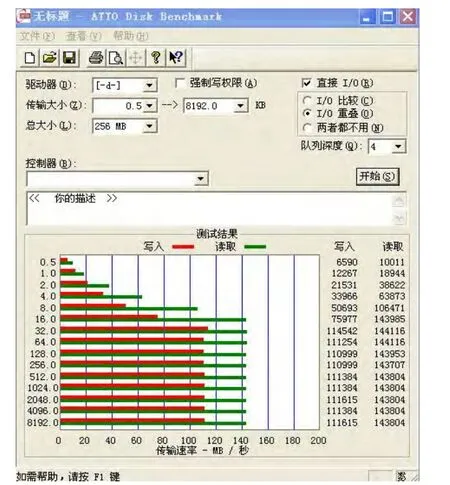

图6 固态硬盘性能测试图

固态硬盘性能测试包括对固态硬盘的读取速度和写入速度测试,振动环境下以及高低温环境下对读写数据的影响。以系统在NAND取4个通道,工作在异步模式为例,在测试软件ATTO下得到测试,得到优化后固态硬盘的读写性能图如图6所示。通过图6可以看出在文件大小为64 KB的条件下,测试读取速度为143 MB/s,由图3可以知道此时理论速度约为152 MB/s,因为系统实际测试时,还要考虑操作系统时间,因而实测结果在可估测的范围内。从而验证了优化方法的有效性以及系统架构设计的可行性,也为下一步研究奠定了基础。在增加系统成本的前提下,根据设计的架构扩展到8通道,根据以上分析,8通道时,估算系统的平均读速度能达到574 MB/s,读的效率比较高。

6 结语

随着NAND Flash固态存储器技术的日益成熟,其存储密度越来越大,而相应的体积、功耗和成本却越来越小,因而NAND Flash固态存储会得到越来越广泛的应用。以并行流水机制为核心,设计了一种基于SATA3.0接口的固态硬盘存储系统,并从硬件架构以及软件调度上对系统的性能进行了分析、优化,最后验证了设计的可行性以及可扩展性。此外,本文设计也为后续对固态硬盘的研究奠定了基础。比如说在系统硬件架构基本不变的情况下,系统版本从FPGA版本扩展到ASIC版本以及在FPGA上实现NAND8个通道并行工作等。

[1]许长庚.高速海量固态硬盘的实现[D].哈尔滨:哈尔滨工程大学,2010.

[2]孙浩然.高速海量固态硬盘的设计[D].哈尔滨:哈尔滨工程大学,2009.

[3]李博.固态硬盘写效率及能耗优化研究[D].武汉:华中科技大学,2010.

[4]唐纯杰.SATA协议分析及FPGA实现[D].长沙:湖南大学,2009.

[5]Serial ATA International Organization.Serial ATA revision 2.6[S].2007.

[6]Serial ATA International Organization.Serial ATA revision 3.0[S].2009.

[7]Ken Takeuchi.Novel co-design of NAND flash memory and NAND flash controller circuits for sub-30nm low-power high-speed solid-state drives(SSD)[J].IEEE Journal of Solid-State Circuits,2009,44(4):1227-1234.

[8]Dirik C,Jacob B.The performance of PC solid-state disks(SSDs)as a function of bandwidth,concurrency,device architecture,and system organization[C]//Proceedings of the 36th Annual International Symposium on Computer Architecture(ISCA’09).New York,USA:ACM,2009,37(3):279-289.

[9]Kang J U,Jo H,Kim J S,et,A superblock-based flash translation layer for NAND flash memory[C]//Proc of the 6th ACM Conference Embedded Systems Software,Seoul,Korea,2006:161-170.

[10]Xu Zhiyong,Li Ruixuan,Xu Chengzhong.CAST:A pagelevel FTL with compact address mapping and parallel data blocks[C]//Proceedings of IEEE 31st International Conference on Performance Computing and Communication Austin,TX,2012:142-151.

[11]张磊,李清江.基于SATA接口的固态硬盘设计[J].微处理机,2011,8(4):77-82.

[12]Lee S W,Park D J,Chung T S,et al.A log buffer-based flash translation layerusing fully associative sector translation[J].ACM Transactions on Embedded Computing Systems,2007,6(3):100-127.

[13]Arm Company.AMBA specification[S].1999.

[14]涂刚.软实时系统任务调度算法研究[D].武汉:华中科技大学,2004.

[15]Synopsys Company.Synopsys design ware SATA device program guide,revision 1.33a[R].2010.

[16]Wu Wei,Su Haibing,Wu Qinzhang.Implementing a serial ATA controller base on FPGA[C]//Proceedings of International Symposium on Computation Intelligence and Design,2009:467-470.

[17]Park S H,Ha S H,Bang K.Design and analysis of flash translation layers for multi-channel NAND flash-based storage devices[J].IEEE Transactions on Consumer Electronics,2009,55(3):1392-1400.