一种高电源抑制比的带隙基准电压源的设计

2014-03-22屠莉敏

屠莉敏,何 颖,易 峰

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

一种高电源抑制比的带隙基准电压源的设计

屠莉敏,何 颖,易 峰

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

提出一种采用BiCMOS工艺的低功耗、高电源抑制比、低温度系数的带隙基准电压源(BGR)设计。该模块基本原理是利用具有正温度系数的热电压VT和具有负温度系数的双极型晶体管VBE叠加产生与温度和电源电压无关的基准电压VREF。该设计中带隙基准电压在25 ℃时,为1.242 V左右。温度从-40~120 ℃变化时,带隙基准电压变化10 mV,可以计算出温度系数为60×10-6℃-1。

带隙基准源;与绝对温度成正比;电源抑制比;低温度系数

1 引言

基准电压源是模拟电路(混合信号电路)设计中广泛采用的一个关键模块。所谓基准电压源就是能提供高精度和高稳定度基准量的电源,这种基准源与电源、工艺参数和温度的关系很小,但是它的温度稳定性以及抗噪性能影响着整个电路系统的精度和性能。本文的目的便是设计一种高精度带隙基准电压源,可以为DC/DC电源芯片提供所需的稳压输出。

本文首先介绍了基准电压源的基本原理,然后介绍了本文的电路结构,最后应用HSPICE仿真工具对本文中设计的带隙基准电压源电路及其附属的过温保护电路进行了完整模拟仿真并分析了结果。

2 带隙基准基本原理

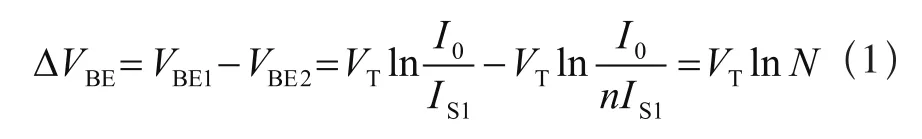

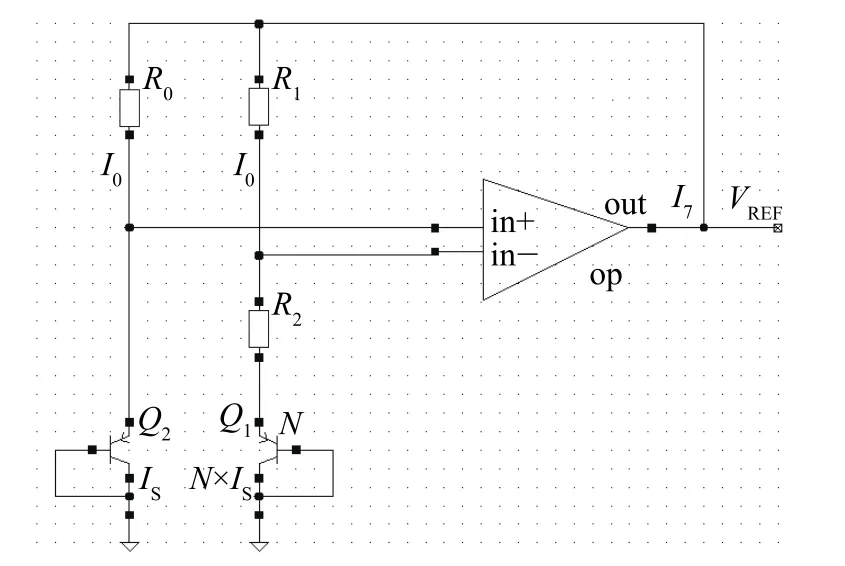

双极晶体管的基极发射极电压VBE,或者说PN结双极管的正向电压,具有负温度系数,约为-2.2 mV·K-1。另一方面,在1964年人们认识到如果两个双极晶体管工作在不相等的电流密度下,那么其基极发射极电压的差值就与绝对温度成正比[3],如图1。

VT的温度系数大约为0.087 mV·K-1,式(1)中的N是Q2、Q1的放射极面积之比。

通过选择合适的K值可使VBE与VT的温度系数相抵消,从而使VREF在理论上成为温度系数为0的基准电压。

图1 简单带隙基准源

3 电路结构

该模块用来产生带隙基准电压(1.24 V)以及其他一些偏置电压。其基本原理是利用具有正温度系数的热电压VT和具有负温度系数的双极型晶体管VBE叠加产生与温度和电源电压无关的基准电压VREF。

3.1模块输入/输出信号功能描述

带隙基准模块的symbol如图2所示。其输入/输出信号功能如表1所示。

图2 带隙基准模块的symbol

3.2模块的电路图

带隙基准的电路如图3所示,左边部分为带隙的核心电路,中间部分为带隙的子电路,右边部分为带隙基准的偏置电路。

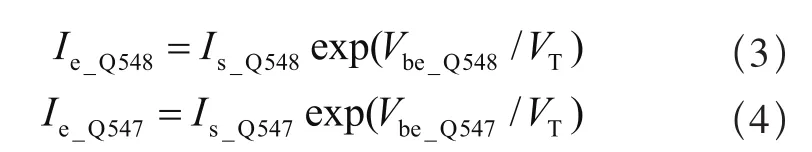

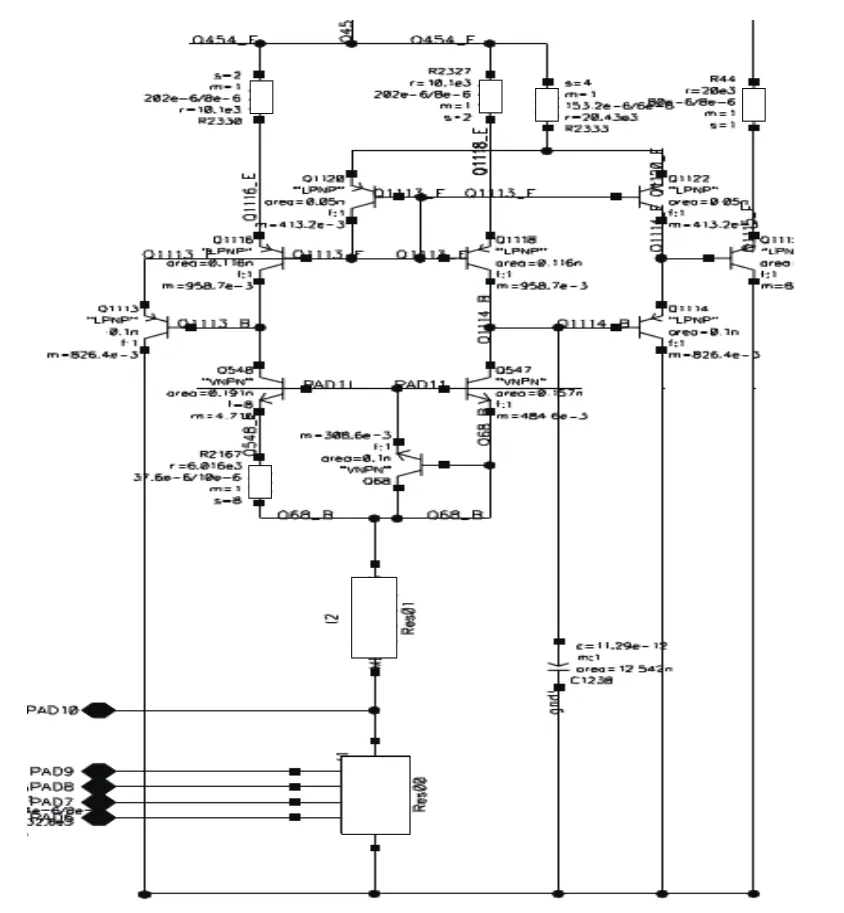

带隙基准的核心电路如图4所示。其基本利用热电压VT的正温度系数与双极型晶体管VBE的负温度系数相互抵消,以减小温度漂移。由晶体管的原理可知:

当Ie_Q548=Ie_Q547时,电路处于平衡状态,在该电路中AQ548=8AQ547。因此:

表1 带隙基准模块输入/输出信号功能描述

图3 带隙基准电路图

即平衡状态下,电阻RES2167两端的电压为VTln8。因此:

电阻RES00是一个比例电阻串,用来调节带隙基准电压的正温度系数部分,对带隙基准电压进行微调。

图4 带隙基准核心部分

4 仿真结果

带隙基准的仿真电路如图5所示。PAD6~PAD10为用来trim的引脚。

图5 带隙基准仿真电路

4.1带隙基准电压输出特性曲线

带隙基准电压输出特性曲线如图6所示。在电源电压VDD为3.5 V时,带隙基准启动。带隙电压为1.242 V。

图6 带隙基准电压输出特性曲线

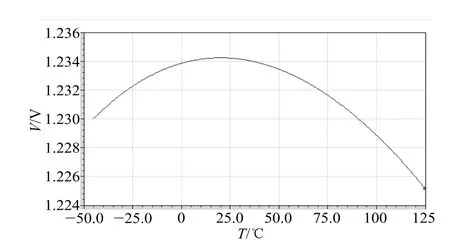

4.2带隙基准随温度变化的曲线

带隙基准随温度变化的曲线如图7所示。本设计中带隙基准电压在25 ℃时,为1.242 V左右。温度从-40~120 ℃变化时,带隙基准电压变化10 mV,可以计算出温度系数为60×10-6℃-1。

图7 带隙基准随温度变化的曲线

5 结束语

在对传统带隙基准源电路进行分析和总结的基础上,本文提出的新型带隙基准源电路由以上仿真结果验证,该设计在满足高电源抑制比的同时也能有非常好的温度特性。

[1] Gerard C MMeijer, GuiJie Wang, Fabiano Fruett. Temperature Sensors and Voltage References Implemented in CMOS Technology [J]. IEEE Sensor Journal, 2001, 1(3): 225-234.

[2] Gray P R, Meyer R G. Analysis and Design of Analog Integrated Circuits [C]. 4th New York(NY USA): John Wiley &Sons, 2001.299-327

[3] 毕查德·拉扎维. 模拟CMOS集成电路设计[M]. 西安:西安交通大学出版社,2003. 318-319.

[4] You F, Embabi S H K, Duque-Carrillo J F, Sanchez-Sinencio E. An Improved Tail Current Soure For Low Voltage Application [J]. IEEE J Solid-State Circuits, 1997, 32(8): 573-583.

[5] Vincence V C, Galup-Montoro C, Schneider M C. A High Swing MOS Cascode Bias Circuit [J]. IEEE Transactions on Circuits and Systems, 2000, 47(11).

[6] Tham K, Nagaraj K. A low supply voltage high PSRR voltage reference in CMOS process [J]. IEEE Solid-State Circuitd, 1995, 30(5): 586-590.

Design of a High PSRR Bandgap Voltage Reference

TU Limin, HE Ying, YI Feng

(China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China)

A high PSRR and low temperature coeff i cient BiCMOS bandgap reference was presented. In the design, the cascade current mirror is used in the circuit, and the output of the OPAMP is used for the bias of itself and to drive the next stage, in the same time PTAT temperature compensate is carried out. In the design of the paper, the output voltage is 1.242 V, while the temperature is 25 ℃. With the temperature range of -40~120℃, the bandgap reference voltage difference is 10 mV, which demonstrates the 60×10-6℃-1temperature ratio.

bandgap voltage reference; proportional to absolute temperature; power supply rejection rate; low temperature coeff i cient

TN402

A

1681-1070(2014)11-0031-03

屠莉敏(1966—),女,江苏常州人,工程师,目前在中国电子科技集团公司第58研究所从事项目主管工作。

2014-07-07