一种高效率MCU芯片Multi-Sites测试技术

2014-03-22张凯虹

陈 真,陆 锋,张凯虹

(1. 江南大学物联网工程学院,江苏 无锡214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

一种高效率MCU芯片Multi-Sites测试技术

陈 真1,2,陆 锋1,2,张凯虹2

(1. 江南大学物联网工程学院,江苏 无锡214122;2. 中国电子科技集团公司第58研究所,江苏 无锡 214035)

介绍了使用Multi-Sites工程测试技术提高MCU芯片测试效率的方案。针对MCU芯片Multi-Sites测试难点,阐述了在MCU芯片Multi-Sites测试中电性能测试、功能测试的影响因素和解决方案,并对MCU芯片Multi-Sites测试过程中经常遇到的干扰因素进行分析,保证MCU芯片Multi-Sites测试获得稳定可靠的性能参数,有效提高测试效率。

MCU;Multi-Sites;测试效率

1 引言

微控制单元(Micro Control Unit,MCU)芯片具有低功耗、低成本、高性能等特点,随着其应用需求的不断提升,新一代MCU芯片的电路复杂性增加,使得芯片测试时间加长,测试成本上升。

传统测试MCU芯片用的是单Site测试,该方法测试时间长、效率低,已不能满足新一代MCU芯片的测试要求。本文介绍的Multi-Sites测试技术能保证在测试结果一致性的前提下缩短芯片的测试时间,提高测试效率,以降低测试成本。但在Multi-Sites测试中,保证各项性能参数精确、可靠并且能实现高效率测试是一大挑战。

本文通过专用自动测试仪器和对应的测试编程软件结合,基于专用板卡、数字存储示波器、信号发生器,搭建出一套完整的测试平台,开发出对应的测试软件,通过对多类MCU芯片实际测试,可以保证各项性能参数精确、可靠并且能实现高效率测试。

2 测试难点

2.1信号干扰

测试频率过高会带来一系列的问题,例如信号的串扰、衍射、畸变等[1]。串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。本文所设计的PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端连接方式对串扰都有一定的影响。但是不论什么样的测试板都会产生一定的噪声。

2.2一致性和高效性

MCU在进行Multi-Sites生产测试中,通过对芯片进行多次测试并分析结果是否一致,如果测试结果的误差在l%以内是可以采纳的。通过增加Site数可提高测试效率,但对测试的结果一致性有影响。同时保证测试结果的一致性和高效性是测试的一大难点。

3 测试技术

3.1软件方式

测试软件采用TR8636开发工具开发,并基于C语言将算法程序封装成动态链接库(DLL),建立通用的函数语句库。函数语句简单明了,程序中无需在用户层次上进行深度优化,就可以做到高并行效率。它是通过对测试系统内的软硬件进行精准的分区以及通过复制调用来实现的。该软件开发环境的灵活性和通用性可有效提高开发周期。

3.2硬件方式

实现Multi-Sites测试在硬件上都采取模块化设计,每个Site必须具备独立的SEQ和控制进程,同时开始,但不一定同时结束。采用模块化设计,以FPGA组件为设计主轴,将SEQ与Timing Generator、Format分别设计在不同FPGA中,以一个SEQ控制8个PIN Waveform Format FPGA。运用分布式控制系统理念,开发可独立的Pin Electric Board(PEB),从而系统可同时并行测试Multi-Sites,有效避免测试频率过高带来的问题。

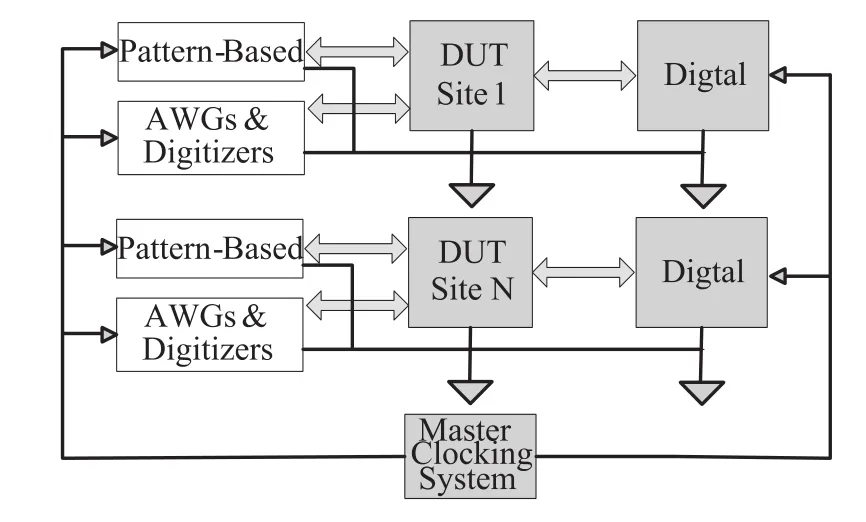

图1表示1-Site测试信道架构[2],该架构包括PEB32板及HVPMU板的测试信道,提供多种切换组合,可让使用者依照IC测试实际需要而做最适当的设定,进而提高MCU芯片的测试效率。以此类推,简单地复制该架构就能制作出Multi-Sites测试系统的架构。

图2表示一个Multi-Sites测试系统的简单架构,其中每一Site都有各自专门的资源,模拟资源和数字资源通过主时钟实现同步。

4 测试实现

4.1信号干扰

在MCU芯片Multi-Sites测试中能对信号干扰有效处理以提高测试效率。

图1 1-Site测试信道架构

图2 Multi-Sites测试信道简单架构

对MCU芯片中所涉及到的信号干扰的处理方法如下:设计PCB时要将模拟电路和数字电路分开布局,以减小数字芯片的噪声对模拟电路的影响;应尽量增大电源线和地线的宽度,或采用电源平面与地平面;在芯片电源和地之间接入滤波、去耦电容,注意电容的引线不能过长;对关键信号要采用屏蔽线,以避免其他信号的干扰;为减小信号线上的分布电阻、电容和电感,应尽量缩短导线长度和增大导线之间的距离;模拟电路的接地层和数字电路的接地层分开,最后通过电感连接起来。

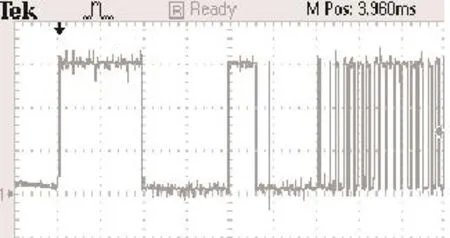

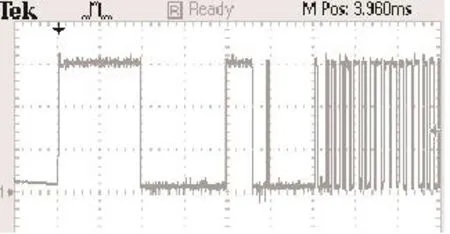

图3是被干扰的信号波形,高电平和低电平上有很多杂波,这些杂波的来源是地电位差干扰。产生地电位差干扰的原因,是由于系统中存在两个以上互相冲突的地,地与地之间存在一定的电压差。该电压通过信号电缆的外屏蔽网形成干扰电流,形成对信号的干扰。图4是处理过的信号波形,可看出高电平和低电平上杂波有明显的减少。图3和图4的对比可看出对信号干扰的有效处理在MCU芯片Multi-Sites测试中的重要性。

图3 被干扰的信号波形

图4 处理过的信号波形

4.2一致性

在Multi-Sites测试中,验证所测MCU的一致性,可用不同的Site对同一颗芯片进行测试,要求测试结果的差异控制在l%以内。另外,在调试中如果其中某一个Site测试有问题,可以考虑换一个Site来测试这颗芯片,或者通过几个Site互换外围芯片或外围DUT,对比测试结果来判断引起问题的原因。一般原因有以下几种:外围芯片发生老化、接口出现脱落或虚焊、MCU芯片功能未达到设计要求、噪声干扰等。对于同一张圆片用不同测试仪测试,如果测出的良率不一致,可以把保存的MAP图和数据进行对照。从MAP图中看到哪几项失效分布在圆片中的具体位置,然后找到失效的MCU,用上述的方法验证分析失效的原因。同时对不一致项的数据可以做柏拉图、直方图、散点图、相关分析、回归分析、ANOVA分析、FMEA、点图、柱状图、雷达图、趋势图或正态分布等方法进行分析。在对MCU测试过程中,避免软件干预已成为提高并行测试效率的标准方法。

4.3高效性

并行测试效率(Parallel Test Eff i ciency,PTE)[3]是Multi-Sites测试的计量,用百分数表示。PTE用以下公式计算:

PTE={1-{[(MSTT-SSTT)/NS-1]/SSTT}}×100

其中:

PTE—并行测试效率(%);

SSTT—单测试位器件测试时间;

MSTT—多测试位器件测试时间;

NS—测试位数。

可以从PTE的公式中推导出,测试位数越多,PTE越高。但是如果生产线上要求测试位超过16或32 个,并行测试效率越高反而影响测试的经济效益。当测试位增加时,并行测试效率可能要求超过99%。相关的调查资料显示,少测试位(2、4或8个)的并行测试效率不需要达到>99%的水平,就可以得到好的经济效益。实际上,并行效率在90%~98%时仍能很好地运作,提供较低的测试成本。

5 结束语

现在芯片测试受到利润影响,对测试效率和测试成本提出了更高的要求。需要合理采用测试设备和仪器,参考电路设计中提供的可测性设计,设计科学的测试方法。作者通过大量测试验证,解决测试中存在的问题,逐步探索形成了一套适用于生产环境的可靠而有效的Multi-Sites并行测试技术,并在多个实际的MCU测试项目中应用,可推广到MCU产品的芯片测试中。

[1] 张凯虹,陆锋,等. DDS自动测试技术研究[J]. 半导体学,2009(03):262-265.

[2] TRI. TR6836 User Guide [M]. IC Tester FAE, Test Research Inc.

[3] Weimer J. 图形测试:多工位模拟和混合信号器件并行测试效率的关键[J]. 中国集成电路,2011(001): 60-65.

A High Eff i ciency Multi-Sites Testing Technology for MCU Chip

CHEN Zhen1,2,LU Feng1,2,ZHANG Kaihong2

(1.College of Internet of Thing,Jiangnan University,Wuxi214122,China; 2.China Electronics Technology Group Corporation No.58Research Institute,Wuxi214035,China)

Describes the use of multi-sites engineering testing technology to improve test MCU chip testing efficiency programs. For MCU chip multi-sites testing difficulties, elaborated factors and solutions for electrical performance testing, functional testing of the MCU chip multi-sites testing. And analyzing the interference factor MCU chip multi-sites testing process often encountered MCU chip to ensure stable and reliable test performance parameters, improve test eff i ciency.

MCU; multi-sites; test eff i ciency

TN492

A

1681-1070(2014)11-0013-03

陈 真(1989—),男,浙江衢州人,目前就读于江南大学集成电路工程专业,硕士研究生,同时在中国电子科技集团公司第58研究所从事集成电路测试工作,主要研究方向为数字集成电路测试。

2014-09-10