DS4830的多地址I2C总线从机模块设计※

2013-09-21潘冬

潘 冬

(成都欧飞凌通讯科技有限公司,成都 610043)

引 言

经过十几年不懈努力,我国已经成为光纤、光缆、光器件和光收发模块的制造大国,特别是在光收发模块领域取得了长足的发展。目前,光收发模块正朝着小型化、高速率、低功耗、长距离方向发展。特别是高速率方向,从最初的10Mbps、100Mbps、1 000Mbps,到10Gbps、40Gbps、100Gbps。其对内部使用的微控制器提出越来越高的要求。不仅仅对微处理器的处理速率有要求,而且对微处理器外围功 能模 块如 ADC、DAC、TEC(Thermoelectric Cooler)等处理性能的要求也越来越高。针对此,Maxim公司针对光通信行业特殊应用及功能要求,定制设计了一款采用低功耗、16位MAXQ20核的微控制器,其提供了完备的光控、校准及监测方案,主要应用于XFP(10Gbps小型可插拨式模块)、SFP(小型可插拨式模块)、SFP+(增强型小型可插拨式模块)、QSFP(4通道小型可插拨式模块)、40/100Gbps光收发器、GPON(Gigabit无源光网络模块)、10GEPON(10Gbps以太网无源光网络模块)、XPON(下一代无源光网络模块)等产品上。

DS4830有如下特性:

① 16位MAXQ20核,RISC指令集,标准Harvard结构。无须借助指令流水线即可实现全部指令的单周期指令的执行。

② 36K字Flash程序存储器,4K字ROM程序存储器,1K字数据RAM。

③ 10路PWM通道(BOOST/BUCK DC/DC控制,支持4路TECC H-Bridge控制)。

④ 最多26路输入的ADC,分辨率达13位。

⑤ 8路DAC通道(12位电压型DAC)。

⑥ 31路GPIO引脚。

⑦ 内置温度传感器。

⑧ 可屏蔽的中断源。

⑨ 内部20MHz的晶振,可支持133MHz外部晶振。

⑩ 支持I2C总线及JTAG BootLoader。

⑪ 低功耗设计,在所有模拟模块使能情况下,功耗仅为16mA。

在光通信行业中,I2C总线是主要的通信接口,无论是应用于光收发还是PON类产品,均要求DS4830作为I2C总线的从机时,要满足SFF-8472协议。SFF-8472协议是一个关于光学器件的数字监控方面的多元协议,主要应用于光收发模块行业,定义其基本的A0H和A2H的MEMORY MAP(地址映射表),即DS4830要满足SFF-8472协议,其能响应两个I2C总线从机地址:0xA0、0xA2。其中,0xA0定义了一个256字节的EEPROM存储器,定义了接口形式、速率、生产厂商、生产日期等信息,0xA2同样定义了一个256字节的EEPROM,包括了光收发器的一些实时监控参量(如温度、电压、发端BIAS电流、发端光功率、收端光功率)报警门限及报警标志。

1 硬件设计

DS4830有两个I2C总线接口,主I2C总线接口和从I2C总线接口。其中,主I2C总线接口使用MSDA(PIN24)、MSCL(PIN26)这两个引脚。从I2C总线接口使用SDA(PIN3)、SCL(PIN2)这两引脚。SFF-8472协议要求光收发器有两个I2C总线从地址,即微控制器要响应两个I2C总线从地址,但由于DS4830主从I2C总线模块接口只能响应一个I2C总线地址,需要将主I2C总线接口设置为从I2C总线模式,并且在硬件上需要将这两个I2C总线接口相连即MSDA与SDA相连作为SDA线,MSCL与SCL相连作为SCL线。

同时,根据I2C总线协议可知,每条总线线路的电容负载Cb在标准模式下最大为400pF,而DS4830这两个I2C总线接口引脚的电容负载CBIN典型值仅为5pF,两条总线并在一齐,电容负载也仅为10pF。另外,针对光收发模块的I2C总线上是不会存在许多I2C总线从器件,故这样的总线相连,不会影响其I2C总线的电气特性。

2 FIRMWARE设计

2.1 开发环境

在FIRMWARE设计中,开发环境为IAR公司的Embedded Workbench For MAXQ 2.40版本。

DS4830内部的主I2C总线模块的寄存器共5个,说明如下:

① 主I2C总线控制寄存器(I2CCN_M)。寄存器地址为M1[0CH],其功能主要有I2C总线工作模式的主从设置,I2C总线的Clock Stretching和I2C总线的TIMEOUT功能相同,都是使能和关闭。

② 主I2C总线状态寄存器(I2CST_M)。寄存器地址为M1[01H],功能是显示各种I2C总线操作时序的状态位。

③ 主I2C总线中断使能寄存器。地址为M1[02H],控制各种I2C总线中断源的使能。

④ 主I2C总线数据寄存器(I2CBUF_M)。寄存器地址为M1[00H],它是I2C总线上的数据寄存器,一级缓冲、发送、接收于一体。

⑤ 主I2C总线地址寄存器(I2CSLA_M)。寄存器地址为M1[0FH],功能是设置响应的从I2C总线地址。

2.2 从I 2C总线模块寄存器

从I2C总线模块寄存器如下:

① 从I2C总线控制寄存器。寄存器地址为M2[0CH],寄存器名称为I2CCN_S。

② 从I2C总线状态寄存器。寄存地址为M2[01H],寄存器名称为I2CST_S。

③ 从I2C总线中断使能寄存器。寄存地址为M2[02H],寄存器名称为I2CIE_S。

④ 从I2C总线数据寄存器。寄存器地址为M2[00H],寄存器名称I2CBUF_S。

⑤ 从I2C总线地址寄存器。寄存器地址为M2[0FH],寄存器名称为I2CSLA_S。

2.3 cstarup.s66文件

DS4830共提供了13个寄存器的模式,其分为外围寄存器和系统寄存器两部分。其中,外围寄存器包括有6个模式(模式0~模式5),主I2C总线相应的寄存器在模式1,从I2C总线的相应寄存器在模式2,故在设计中断服务程序中,必须访问不同模式下的寄存器。这必须修改cstartup.s66文件,该文件类似于Keil C51中的STARTUP文件,但是不同于Keil,在创建项目的时候,集成编译器自动添加一个STARTUP启动文件,而且这个文件直接列在项目表上,让人一目了然。但IAR IDE中,如果没有在项目内人为加入cstartup.s66启动文件,则使用系统默认目录下的默认cstartup.s66文件。

另外,由于DS4830中断机制只使用一个中断向量,所有中断的优先级别相同。在中断全局使能的情况下,每当一个中断响应后,程序跳转到cstartup.s66区,根据中断标志判断不同的中断源,并跳转进入其相应的中断服务程序。为了加快I2C总线响应速率,需将I2C总线中断的优先级提到最高,通过将主从I2C总线中断服务程序(cstartup.s66文件中的INTERRUPT2)修改到所有中断程序的第一位,即将I2C总线中断入口判断变为保存现场后的第一个判断。

修改cstartup.s66中断部分代码如下:?isr:

2.4 中断服务程序

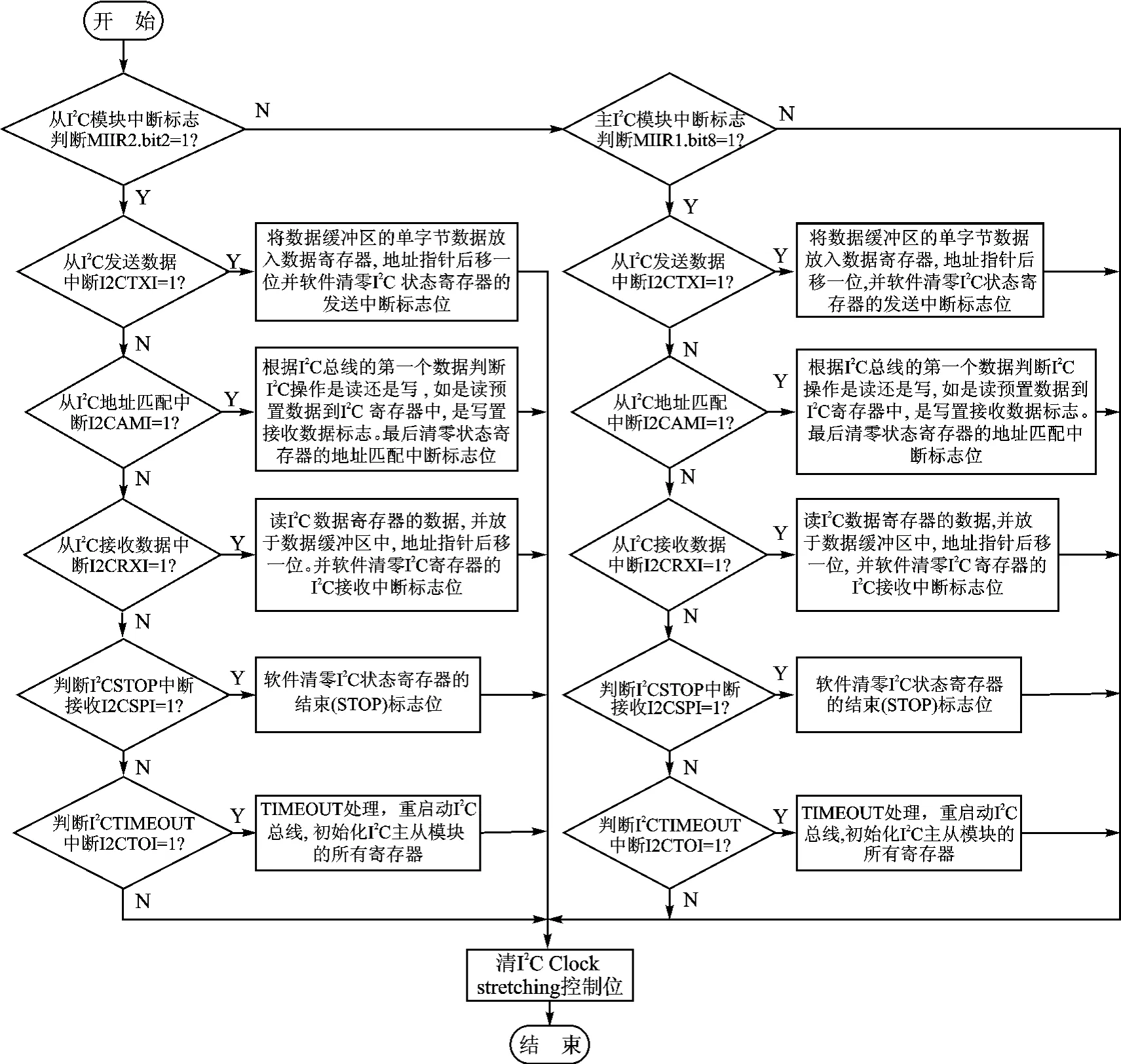

中断服务程序流程图如图1所示。

2.5 伪代码(Pseudo Code)

初始化函数略——编者注。

(1)Clock stretching机制

作为从I2C总线器件,有一个关键的特性就是Clock stretching,即当从器件不及时接收或发送完整的数据时,从器件会将SCL线拉低,强迫I2C总线主机进入等待状态,直到从器件准备好相应的数据后才释放SCL总线。由于DS4830内核是20MHz时钟,但其指令时钟仅为10 MHz,要达到标准100kHz的I2C总线时钟速率,必须在软件控制Clock stretching时,即在初始化时使能Clock stretching使能位I2CSTREN。IAR生成的中断服务程序的LIST文件部分略——编者注。

图1 中断服务程序流程图

DS4830中断响应时间分为3部分:

① CPU响应4个指令周期。

② cstartup执行最多10个指令周期。

③ 中断服务程序执行压栈部分16个指令周期。

这样算下来进行中断程序未对I2C总线寄存器进行处理前已有30个指令周期时间,即30×0.1μs=3.0μs。要达到100kHz的I2C总线速率,按占空比50%计算,低电平为5μs,故不考虑上升下降沿的时间,留给中断服务程序的时间仅有2μs去处理I2C总线寄存器和相应SFF-8472协议EEPROM要求。这是相当困难的,所以尽量提高I2C总线速率,使能Clock stretching。

实际验证中,当I2C总线模块不使能Clock stretching后,上位机(I2C总线主机)对DS4830 0xA0地址的3种I2C总线读操作为:当前读、页读、单字节读,其读出的结果均为0xA1。原因即是I2C总线主机发送到从器件的I2C总线地址值为0xA1(读模式),在SCL时钟低电平期,真正要发送的数据还未送到数据寄存器(I2C_BUF),此时数据寄存器中仍为接收到的地址值。SCL高电平来到,直接将这个值移位出了数据寄存器送到I2C总线上,如图2所示。

图2 I 2 C总线时序图(读部分)

(2)SMBus Timeout机制

SMBUS(System Management Bus),是1995年Intel公司提出的,最初设计应用于移动PC和桌面PC系统中的低速率通信。它与I2C总线电气及协议定义上类似,但在速率、超时错误、逻辑电平和总线协议上有所区别。DS4830主机I2C总线模块是使用兼容I2C总线协议,并引入SMBUS超时错误功能,使用一个30ms的定时器,当总线SCL低电平超过这个时间后,触发TIMEOUT中断,以释放I2C总线,避免I2C总线的锁死。由于各种公司的I2C总线兼容协议可能存在一些差异,各种时序,包括一些非法或错误的时序都有可能在总线上出现,所以使用TIMEOUT机制来避免I2C总线死锁是相当有效和实用的。DS4830使能TIMEOUT功能,通过I2CCN_S(M)控制寄存器的SMB_MOD置位来实现。

伪代码程序略——编者注。

结 论

本文通过介绍DS4830相应主从I2C总线模块接口的寄存器,利用IAR编译环境实现了I2C总线从器件操作,并满足SFF-8472协议对多从机地址的要求。系统的上位机发出各种常规的I2C总线读操作及写操作均正常。该方法已应用于SFP+ZR、QSFP产品中,并得到客户系统验证,I2C总线可靠、稳定。

编者注:本文为期刊缩略版,全文见本刊网站www.mesnet.com.cn。

[1] Maxim Integrated Products.DS4830datasheet[EB/OL].[2012-09].http://datasheets.maximintegrated.com/en/ds/DS4830.pdf.

[2] Maxim Integrated Products.DS4830Optical Microcontroller User's Guide[EB/OL].[2012-09].http://pdfserv.maximintegrated.com/en/an/UG5484.pdf.

[3] Maxim Integrated Products.MAXIM Integrated application Note 3960[EB/OL].[2012-09].http://china.maximintegrated.com/app-notes/index.mvp/id/3960.

[4] NXP Semiconductors.THE I2C-BUS SPECIFICATION VERSION 2.1JANUARY 2000[EB/OL].[2012-09].http://www.classic.nxp.com/acrobat_download2/literature/9398/39340011.pdf.