FPGA内嵌PowerPC的中断响应分析

2012-06-13李乾坤张恕明尹达一

李乾坤,张恕明,尹达一

(中国科学院上海技术物理研究所,上海200083)

1 引言

Xilinx公司 Virtex-ii Pro系列的 XC2VP40 FPGA内嵌有PowerPC405核。开发者可以使用开发工具XPS在芯片内部构建以PowerPC为核心的片上系统。除内核外,时钟、JTAG、定时器等模块均可由FPGA内的逻辑资源定制而成。

PowerPC内核支持外部中断,并可通过中断控制器进行扩展,XPS亦针对中断控制部分提供了完整的驱动程序。由于中断系统可以提高处理器的利用率,增强处理器的实时性,是微处理器系统的重要组成部分。因此,深入研究PowerPC的中断系统对于更合理高效地使用PowerPC有着十分重要的意义。

下面就针对PowerPC中断系统展开讨论。

2 PowerPC异常处理

2.1 PowerPC的异常与中断

首先对两个名词进行一下说明:

异常:处理器检测到的不可预测的错误事件。

中断:处理器检测到异常时自动启动的处理过程。

PowerPC支持16种异常处理,对应16种中断源。其中Critical Input与External两种中断源来自外部输入,也称之为外部中断。

2.2 外部中断优先级

Critical Input中断优先级要高于External中断,当两个中断同时发生时,Critical Input中断响应先于External中断执行。另外,PowerPC支持中断嵌套,这意味着Critical Input中断可以终止正在执行的External中断响应过程。

2.3 外部中断响应流程

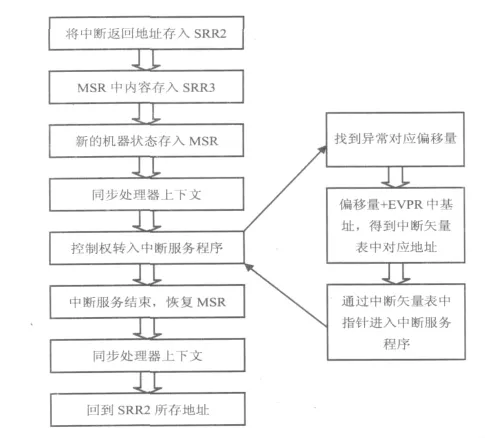

以Critical Input为例,PowerPC外部中断响应流程如下:

1)将中断返回地址存入寄存器SRR2(External为SRR0)。

2)将机器状态寄存器MSR中的内容存入寄存器 SRR3(External为 SRR1)。

3)将新的机器状态存入寄存器MSR。

4)同步处理器上下文。

5)转入中断服务程序。

6)中断服务程序结束,恢复寄存器MSR的状态。

7)处理器上下文同步。

8)跳到SRR2(External为SRR0)中存的返回地址。中断响应完毕。

那么,处理器是怎样找到中断服务程序的?

首先解释一下中断矢量表这个概念。为使异常得到相应中断服务程序的处理,需要首先建立中断矢量表。中断矢量表中每隔一段地址会存放一段代码,分别对应不同的异常。

当发生异常时,系统会通过中断矢量表的基址以及相应的偏移量找到对应的代码,进而找到中断服务程序。其中,中断矢量表的基址存储在寄存器EVPR中。由于中断矢量表中各代码段存储容量的限制(大部分为256Byte),中断矢量表往往不直接存储中断服务程序,而是存储指向中断服务程序的指针。PowerPC异常处理详细流程如图1所示。

图1 PowerPC异常处理流程图

3 PowerPC外设简介

3.1 中断控制器

Power PC提供了两个外部中断入口,这在有较多中断输入的情况下是不能满足需求的。为了解决这个问题,可以使用中断控制器。

每个中断控制器有32个中断源输入接口,1个中断信号输出接口。当一个或多个输入端有中断输入时,输出端输出中断信号。

中断控制器中包含一个32位寄存器,其每一位对应一个中断输入端。当有中断输入时,对应的标志位便被置1。中断响应过程中,从低位到高位对寄存器中的标志位进行查询,从而判断中断来源。因此,对应标志位的位置决定了中断响应优先级。

使用XPS的BSB构建系统时,即使只有一个中断源,一般也会包括中断控制器,用以连接外设与处理器内核。

3.2 Timer模块

一个Timer模块包括两个Timer,可以实现三种模式:Capture mode,Generate mode 及 PWM mode。

其中两个Timer可以分别配置成Capture mode与Generate mode同时工作,对应不同的脉冲输出。两个Timer合作可以实现PWM mode,对应单一的PWM输出。

Timer模块支持中断输出,但两个Timer共用一个中断输出端口。

4 PowerPC中断响应过程分析

4.1 构建中断系统

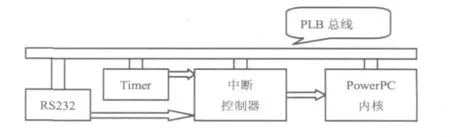

为了对中断响应过程进行分析,构建如图2所示系统。该系统主要由PowerPC内核,中断控制器,Timer,RS232模块,时钟模块(该模块未在图中显示)等组成。各模块均连接PLB总线。其中时钟模块提供80MHz时钟输入,Timer与RS232的中断输出端接到中断控制器的不同输入端,中断控制器的输出接到处理器的External Input端。

图2 中断测试系统框图(未包含时钟模块)

4.2 中断服务程序详解

XPS为中断系统提供了完整的中断服务程序。

4.2.1 外设的信息结构体

在介绍中断服务程序之前,先解释一下外设的信息结构体。XPS提供的代码为每个外设(包括中断控制器)都建立了一个结构体。结构体中包含了该外设的ID,基址,状态,中断服务程序入口,中断服务参数等信息。当需要对某个外设进行操作时,首先会找到其对应的结构体,然后读取外设信息,进而对其进行操作。

而对于中断控制器,其与一般外设又有一定的区别,其结构体中不是包括单独的中断服务程序入口与参数,而是包括一个中断服务及参数的列表。列表的长度为32,即每列对应一个输入端。

处理器通过中断矢量表进入中断服务程序后,会首先根据系统自动传入的参数ID找到对应中断控制器的信息结构体,然后查询中断控制器的输入,通过结构体内的中断服务列表找到对应的中断服务子程序。

在对Timer进行操作前,亦需先找到其对应的信息结构体。每个Timer有一个中断输出,但一个Timer包括两个计数器。因此,必须首先判断中断由哪个计数器引起,然后再调用相应的子程序。

4.2.2 中断服务流程

有了以上知识,来看一下XPS提供的中断服务程序流程是怎样的。如图3所示,在中断服务函数中,程序首先找到中断控制器的信息结构体,然后判断中断来源(这里为 Timer)以调用对应的函数(Timer中断服务函数),然后清除中断控制器输出。在Timer中断服务函数中,首先找到Timer模块的信息结构体,然后判断中断由哪个Timer引发,将结果传入子函数,在子函数中实现相关操作。子函数返回后,清除timer中断输出。

图3 XPS提供的中断服务流程

4.3 测量

下面对中断响应过程的时间参数进行测量。

4.3.1 需要测量的参数

定义T1,T2,T3三个参数,它们的意义如下:

T1:一次中断响应过程的总时间。即从外设发出中断信号到中断响应结束的时间。

T2:由Timer模块发出中断申请到执行自定义操作需要的时间。注意,这里的自定义操作为清Timer中断,位于图3所示的自定义函数中。这样会导致响应一次中断响应过程中两次清Timer中断,不过这并不影响测量结果。

T3:中断控制器的延迟时间。即Timer模块发出中断申请到中断控制器发出中断申请的时间间隔。

4.3.2 测量方法

1)上位机通过RS232向PowerPC发出指令,启动Timer模块(只使用其中一个Timer),Timer设定为generate mode,每两个时钟周期产生一次中断。这样可以保证每次中断响应结束之前产生下次中断的触发脉冲,使系统每处理完一次中断后立刻进入下一次中断的响应。这时Timer模块中断信号的周期即等效于系统一次中断响应过程的周期T1。上面已经提到,每一次中断响应过程中会有两次清中断的操作,因此一个周期中会产生两次中断信号的变化,但不会影响测量结果。

2)Timer保持generate mode不变,但调整其中断发生周期,使其远大于中断响应过程的总时间(依据上一步测得的结果),以保证产生下次中断信号时,上次中断服务已经结束。测量Timer模块中断发生到被清除的时间,即为中断发生到执行自定义操作的时间T2。同时可测到T3。

4.3.3 测量工具

使用Tektronix公司TDS3014B示波器进行测量。

4.3.4 测量结果

T1:24.40μs。约为1952个时钟周期。

T2:10.36μs。约为829个时钟周期。

T3:41.00 -41.50ns。约为 3.3 个时钟周期。

5 提高中断效率的研究

5.1 保持原硬件系统不变

通过分析PowerPC异常处理流程及中断服务函数可以发现,能够进行修改的过程只有中断服务函数部分。根据之前的分析,执行一次中断服务函数会发生两次函数调用以及数次对外设信息结构体的查找与读取。这样的优点是代码移植性强且安全性好。但在对外设信息完全掌握的前提下,可以不通过信息结构体而直接对外设进行操作,亦可以不通过函数调用而是直接编写代码。简化后的中断服务函数流程如图4所示。

此时测得的各参数如下:

T1:14.72 -14.73μs。约为1178 个时钟周期。

T2:6.588μs。约为527个时钟周期。

T3:41.00 -41.40ns。约为 3.3 个时钟周期。

通过对比数据可以发现,T1缩短为原来的60.35%,T2缩短为原来的 63.57%。

图4 简化后的中断服务函数流程图

5.2 简化硬件系统

在以上的系统中,Timer中断通过中断控制器连接到PowerPC的External Input端口,这样的结果是在中断服务程序中需要增加对中断控制器的操作代码,而且使用中断控制器会使External Input端口接收到中断信号的时间有一定的延时(即T3)。在中断数量不大于2的情况下,完全可以不使用中断控制器,而是将外设的中断信号直接接到PowerPC的两个异常输入端。

现在,对系统做如下修改,将中断控制器从系统移除,将Timer模块中断输出端接到PowerPC External Input端口,将RS232中断输出端接到PowerPC Critical端口。修改后的系统结构如图5所示。

此时只需要在中断处理程序中执行自定义操作(清Timer中断)及清除Timer中断输出命令。中断服务程序得到了进一步简化。

测得各参数如下:

1)T1:11.59μs。约为927个时钟周期。

2)T2:5.45μs。约为436个时钟周期。

可以看出,中断响应效率进一步提高。此时T1为原来的47.49%,T2为52.59%。

图5 修改后的系统结构框图

6 结束语

本研究对FPGA内嵌PowerPC中断系统的原理进行了深入的分析,对中断响应时间进行了实测,并通过简化设计提高了中断响应速度,可以作为需要设计快速响应系统的参考。

[1]张春生,常青,肖山竹.基于PowerPC405的SOPC简单应用[J].微处理机,2007(6):117-120.

[2]买培培,苏涛,张晓曦.基于PowerPC的控制器研究与设计[J].船舶电子对抗,2009,32(5):102-106.