一种二相线阵电荷耦合器件的数据采集器设计

2013-07-13林金朝宋得龙

高 翔,林金朝,庞 宇,宋得龙

(重庆邮电大学光电工程学院,重庆400065)

0 引言

二相线阵电荷耦合元件(CCD)即电荷耦合器件,是20世纪70年代初发展起来的一种新型半导体集成光电器件。它具有体积小、噪声低、灵敏度高、可靠性好等特点,被广泛应用于图像传感和非接触测量等领域[1]。在高速应用时代,传统的单路CCD已很难满足高数据率的要求,带有双路输出的二相线阵CCD便应运而生,其数据率可达单路输出的两倍。然而,由于输出信号变成了两路,导致在对输出信号进行处理上变得更为复杂。传统处理方式是将两路信号分别进行处理,然后再将得到的数据合并在一起。由于本身处理一路信号就包含了滤波、采样、放大等多个步骤,要处理两路信号更是大大增加了处理电路的复杂度[2-4]。另外,由于数据量的巨大,要想正确地将两路数据合并在一起也往往并不那么简单。本文设计的数据采集系统使用双路输出CCD,并通过专门的数据处理器对其双路信号进行处理,达到了电路简单,性能可靠,实现方便的效果。

1 设计方案

采用TOSHIBA公司的TCD1703C型二相线阵CCD做模拟数据采集,并用Analog Devices公司的AD9826型信号处理器进行数据处理,实现对待测物的数据采集。TCD1703C具有7 500有效像元,其像元尺寸为7 μm×7 μm×7 μm,像元区总长52.5 mm,响应度为15 V/(lx·s),驱动频率最大可达到20 MHz。AD9826是一款专门面向CCD的低功耗多通道信号处理器,其双通道模式尤其适合处理奇偶双路输出的CCD信号。它内含最高30 MSPS的相关双采样器(CDS)、补偿DAC、1~6倍可编程增益放大器(PGA)、16位精度ADC,可以极大地简化信号处理电路的设计。

设计关键在于对CCD和信号处理器的驱动时序的设计。设计驱动时序有很多方法,包括数字逻辑电路、单片机、专用IC以及现场可编辑门阵列(FPGA)等。但数字逻辑电路结构复杂,用到大量计数器、门电路,时序难以配合,电路不稳定,抗干扰能力差,制作修改比较麻烦,体积占用也很大[5]。由于现在CCD驱动对频率要求越来越高,大多数单片机的频率都难以达到要求。虽然专用IC功耗低,集成度高,可靠性也好,而且产生的驱动时序也非常好,但价格过于高昂,灵活性也不好。所以,功耗小、成本低、易调试且稳定性好的FPGA成为驱动时序设计的最佳选择。这里采用Altera的EP2C8Q208型FPGA,其价格适中,具有8 256个逻辑单元,138个I/O管脚,可外接超过50 MHz晶振,资源足以应对本系统的要求。针对FPGA的I/O口输出电平为3.3 V,而大多数器件对控制驱动往往要求5 V电平的问题,可在后续模块前端外接CMOS器件予以解决。

系统采用Top-down多层次结构电路的设计方法[6],利用图形和文本混合进行设计,将系统分为分频器、CCD驱动时序和信号处理控制时序3个模块,整体设计框图如图1所示。其中,预处理电路包括差分电路和跟随电路。差分电路通过一个差分放大器抑制掉输出信号中的5 V直流分量,跟随电路可以提高信号的负载能力,使信号更稳定。

图1 整体设计框图

2 CCD驱动时序

TCD1703C的驱动由5路脉冲构成:SH、Q1、Q2、RS、CP。其中,转移脉冲SH将CCD存储栅中光积分所产生的光生电荷,并行地分别转移到光敏区两侧的模拟移位寄存器的电荷势阱Q1和Q2中。当SH脉冲结束时,SH为低电平,它使存储栅和模拟移位寄存器隔离。存储栅和模拟移位寄存器分别工作。存储栅进行光积分,模拟移位寄存器在驱动脉冲的作用下串行地向输出端转移信号电荷,最后由奇数输出端OS1和偶数输出端OS2分别输出,得到OS1信号和OS2信号。RS为复位级的复位脉冲,每复位一次输出一个信号。CP是钳位脉冲,用于钳制输出信号电平[7]。

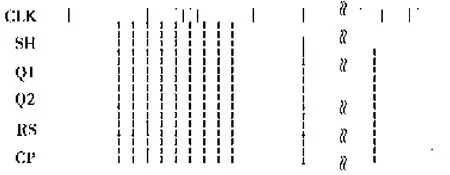

由TCD1703C的数据手册可以看到:其典型最佳工作频率为1 MHz,5路脉冲的时序如图2所示。由于该器件是两列并行输出,所以在一个SH周期中至少要有7 500/2个Q1脉冲,即TSH>3 750TQ1,而加上前后哑元数后,TSH应至少有3 822个Q1脉冲。另外,SH为高电平的时间应大于1 000 ns,1 MHz时钟下的典型值为1 500 ns,RS和CP为高电平的持续时间典型值为100 ns。

图2 TCD1703C驱动脉冲波形图

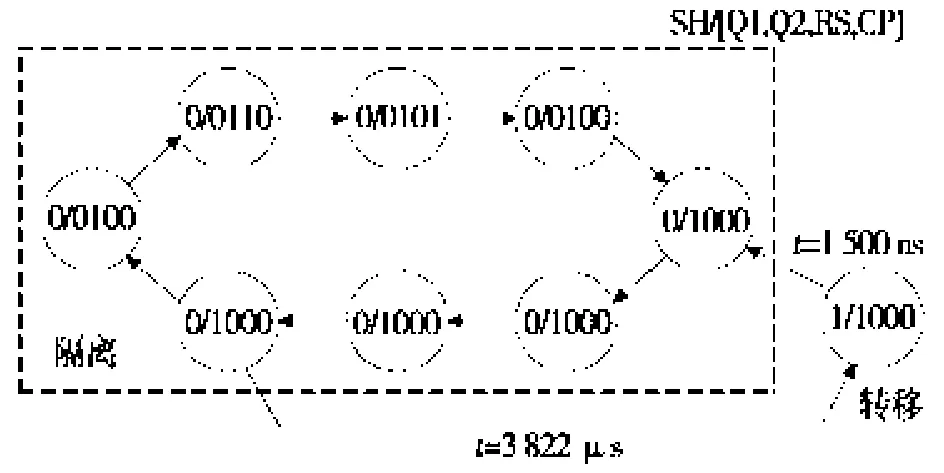

由此,FPGA可选用48 MHz的外部晶振,经六分频后得到工作时钟CLK=8 MHz,在CLK的上升沿(即每隔125 ns)每触发一次状态机,由计数器控制时间状态转换。当满足3 822 μs后,CCD扫描完一行,这时SH置高进入转移状态,[Q1,Q2,RS,CP]保持1000状态不变。当1 500 ns后SH置低进入隔离状态,[Q1,Q2,RS,CP]开始输出状态序列[8-10]。状态图如图3所示。

图3 TCD1703C驱动时序状态图

3 AD9826控制时序

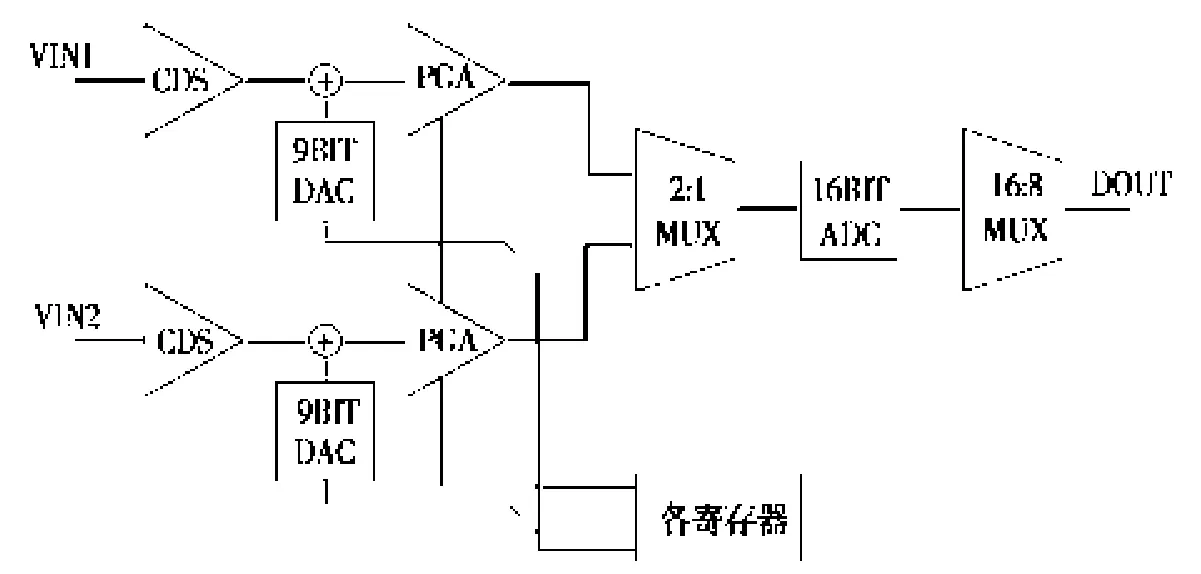

AD9826是可编程的信号处理器,内含的相关双采样器有两种采样模式:CDS和SHA。CDS模式即对待采样信号的参考电平和数据电平分别采样的差分输出,因前端已通过差分电路将TCD1703C的参考电平钳制在0 V,故可直接将参考电平采样时序输入端接地,从而只需进行数据电平采样,即SHA模式。AD9826工作原理如图4所示。

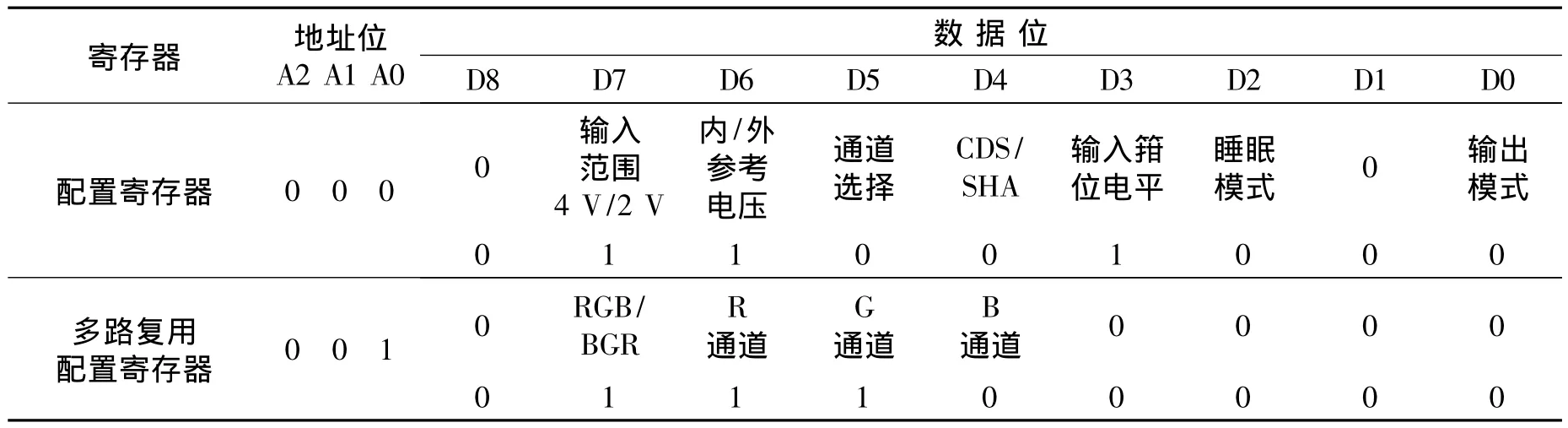

其内含的相关双采样器、增益放大器和模数转换器的具体功能设置,都是通过编程串口配置其内部对应的各相关寄存器来实现的。其中,配置寄存器用来设置AD9826的操作模式和偏置电平;多路复用配置寄存器控制抽样通道的相关命令和双通道配置;放大电路增益寄存器有3个,分别设置3个输入通道的PGA的放大倍数;补偿寄存器也有3个,分别设置3个通道的补偿电压。这里只需要配置前两种寄存器即可[11],具体配置见表1,可通过配置使AD9826工作在16 bit双通道SHA模式。其中,因CCD输出信号高低电压差最大为4 V,故将AD9826的输入范围设置为4 V。

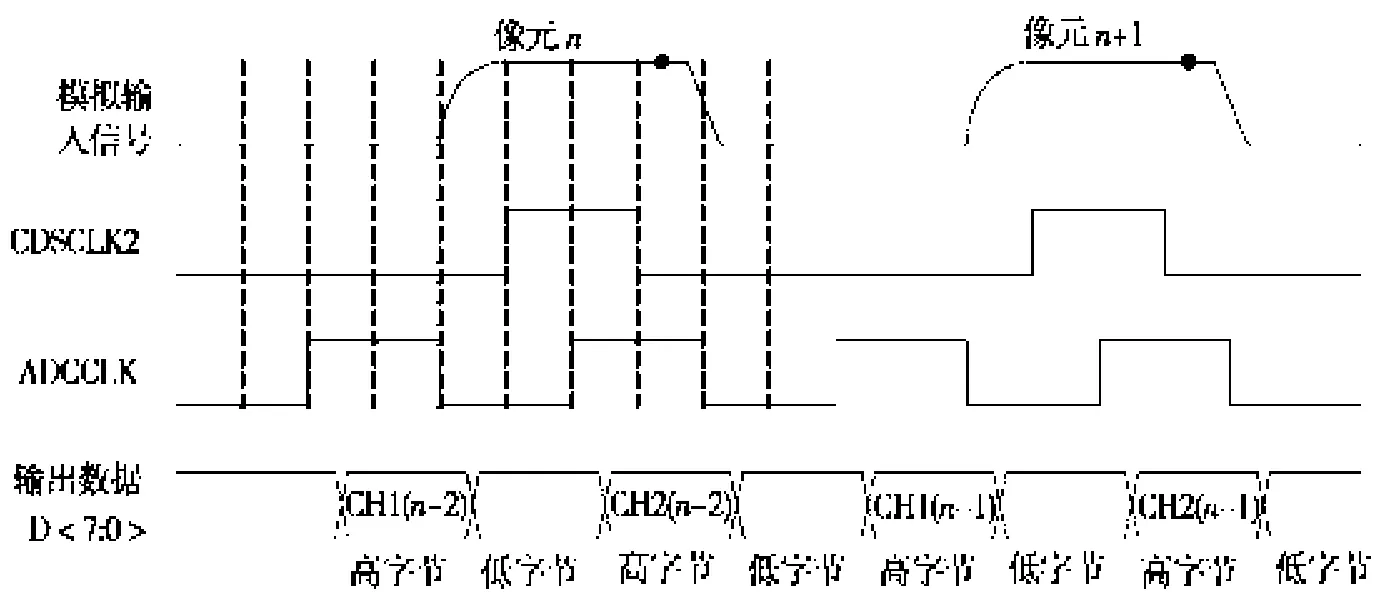

AD9826先在数据电平采样时钟CDSCLK2的下降沿分别对两个通道的输入信号进行采样,并将采得的数据依次经过DAC和PGA处理,然后送入16 bit的A/D转换器,转换器在ADC采样时钟ADCCLK的下降沿对其进行采样,由于AD9826的输出只有8位数据线,所以将16 bit信号分成高低两个8 bit信号分时输出,如图4所示。

图4 AD9826原理图

表1 相关寄存器配置参数

双通道SHA模式的采样时序如图5所示。由图5可以看出:AD9826的输出数据相对采样点有3个ADCCLK周期的时间延迟。在设计驱动时序时应当注意,CDSCLK2的频率应与输入信号相同,而ADCCLK的频率是输入信号的两倍。由于CCD输出信号频率为1 MHz,故fCDSCLK2=1 MHz,fADCCLK=2 MHz。另外,由数据手册[6]可知:CDSCLK2高电平持续时间应大于8 ns,ADCCLK2的下降沿不能位于ADCCLK前一个下降沿之前。

图5 AD9826的双通道SHA模式控制时序图

通过上述分析,该控制时序同样可由状态机来实现,如图6所示。

由TCD1703C输出特性可知:两路输出信号中的有效分量是在Q2下降沿后10 ns输出,由此便可确定AD9826控制时序与TCD1703C驱动时序间的相位关系。另外,由于TCD1703C正常工作时前后各有64和8个哑元信号,而这72个哑元信号是不需要采样的。所以,可以在AD9826开始工作时,先用计数器对前64个哑元信号计数,等64个信号全部移出后启动采样时钟,并在采满3 750个点后中断采样时钟,等待下一个采样周期的到来。

图6 AD9826控制时序状态图

需要注意的是:由于TCD1703C的输出信号含有5 V的直流分量,不能满足AD9826最大4 V的输入范围,所以应当在CCD信号输出后先通过差分电路抑制掉该直流分量,以确保信号处理器的输入信号为0~4 V。

4 试验结果与分析

4.1 仿真波形

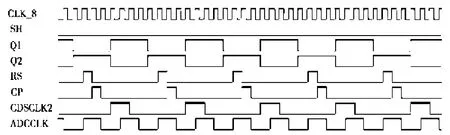

AD9826配置时序如图7所示,其中,CLK_8为48 MHz外部晶振经分频器分频得到的8 MHz工作时钟,SDATA为数据I/O口,SCLK为配置时钟,SLOAD为负载脉冲。

图7 AD9826配置时序

整体控制时序如图8所示,其中,SH、Q1、Q2、RS、CP为 TCD1703C的驱动时钟,CDSCLK2、ADCCLK为AD9826的采样控制时序。

图8 整体控制时序

4.2 试验波形

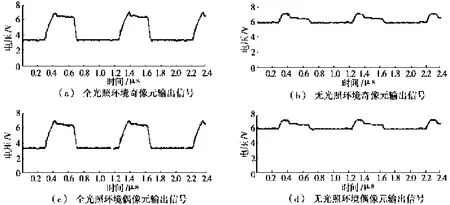

由示波器可观察到TCD1703C的双路输出波形,如图9所示。

图9 CCD输出信号波形

由于AD9826通过8位并行口高速输出数据,用示波器难以观察,可通过输出口分别对地外接发光二极管(亮为1,灭为0)进行粗略观察。因设置的信号输入范围为0~4 V,故当输入电压接近0 V时,发光二极管为00000000,此数将随电压增大而不断增加;当输入电压为4 V时,输出为11111111。因此,接入图9所示CCD波形采样后,全暗为00000000,随着光照强度的增大而增加,直到全亮11111111。正常工作后可通过后续电路传输至计算机进行详细数值分析,这里不再赘述。

5 结论

本文结合二相线阵CCD输出信号的特点及其后续处理电路复杂的现状,提出了一种通过专门集成的数据处理器对其双路信号进行高速处理的方法。该方法简化了信号处理电路的设计,解决了高速二相线阵输出信号处理复杂的问题,具有较高的应用价值。经在实际电路中验证,电路结构简单,工作稳定可靠,处理结果可以满足应用要求。

[1]王庆有.图像传感器应用技术[M].北京:电子工业出版社,2003.

[2]魏常伟,袁纵横,张文涛,等.基于FPGA的新型告诉CCD图像数据采集系统[J].测控技术与仪器仪表,2010(4):77-80.

[3]胡胜,杨雷,宋跃,等.基于ARM &FPGA的CCD图像识别装置[J].仪表技术与传感器,2012(1):54-56.

[4]陈飞明,曹万民,韩苏雷,等.用二相双列线阵CCD器件实时采集衍射图样[J].洛阳工学院学报,2001,22(3):83-86.

[5]阎石.数字电子技术基础[M].北京:高等教育出版社,2006.

[6]王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2011.

[7]王庆有.CCD应用技术[M].天津:天津大学出版社,2000.

[8]魏冬冬,王大勇,李彩霞.CCD时序驱动电路的设计[J].传感器与微系统,2011,30(9):112-114.

[9]商小川,周辉,张星祥,等.基于FPGA的大面阵CCD高帧频驱动电路设计[J].液晶与显示,2009,24(5):735-739.

[10]付天舒,赵春晖.基于Verilog的线阵CCD驱动时序设计[J].光学技术,2010,36(5):740-743.

[11]张殿富,赵源.基于FPGA的线阵CCD驱动时序及模拟信号处理的设计[J].国外电子元器件,2009,17(1):41-43.