一种基于FPGA的DDS信号发生器的设计*

2012-11-18龚光松

龚光松

(咸宁职业技术学院,湖北 咸宁 437100)

一种基于FPGA的DDS信号发生器的设计*

龚光松

(咸宁职业技术学院,湖北 咸宁 437100)

随着可编程逻辑器件的不断发展,利用DDS技术原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,具有成本低、在线更新、硬件开发软件化、操作灵活等优点.本文介绍了一种基于FPGA的DDS函数信号发生器设计,实现了输出100Hz~1MHz的正弦波、方波、三角波,频率设置等功能,具有一定的实用价值.

FPGA;DDS;Quartus II 9.0

1 DDS基本原理

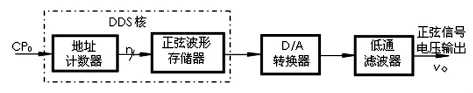

DDS技术产生波形的过程是:基于奈奎斯特(Nyquist)抽样定理对需要产生的波形进行采样,经量化后存入存储器(例如,ROM)中作为待产生信号波形的数据表;在需要输出波形时,从数据表中依次读出数据,产生数字化的信号,这个信号再通过D/A转换器和滤波器后就变成了所需的模拟信号波形.如果改变数据表中的内容,就可以得到不同的信号波形.

DDS技术产生波形的原理框图

2 DDS的FPGA实现方案

以FPGA平台为核心,将各波形的幅值/相位量化数据存储在ROM内,按照设定频率,以相应频率控制字DATA为步进,对相位进行累加,以累加相位值作为地址码读取存放在存储器内的波形数据,经D/A转换和幅度控制、滤波即可得到所需波形.系统总体设计方框图如图所示.

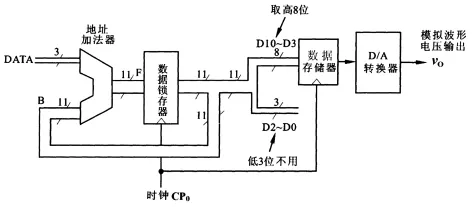

DDS实现框图

在FPGA中,地址计数器由地址加法器和并行数据锁存器组成.加法器有两个数据输入端:一个输入端B与数据锁存器的输出相连;另一个输入端为相位增量DATA,又因为DATA是决定DDS输出频率的参量,因而又被称为频率控制字,存放DATA的寄存器被称为频率控制寄存器.电路工作原理如下:在频率数据DATA的控制下,地址加法器的输出结果为DATA+B,因此,在时钟CP0的作用下,数据锁存器的输出数据D10~D0每次将增加DA TA.也就是说,DATA控制了地址加法器输出的递增速率.此例中,DA TA最小值为1,最大为值7(23-1).在时钟CP0不变的情况下,DATA的大小控制着D10~D0从最小值变到最大值所用的时间.DATA大,每次相加运算得到的结果就大,即数据存储器的地址增长快,地址循环一周(从D10~D0最小值0到最大值211-1)所需时间就短.由于数据存储器每经过一个循环就会输出一个离散的正弦波数据,所以经过D/A转换器后,输出的波形频率就高,反之则频率就越低.为保证输出数据的精度,将数据D10~D0分为两部分:高8位D10~D3与波形数据存储器相连,低3位 D2~D0不用,这样,D10~D3的数据不会大于1,从而能够顺序地从数据存储器读取数据.

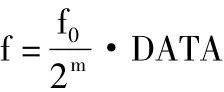

改变DATA的值就能改变输出信号的频率,数据存储器中的全部数据被读出一次的频率为:

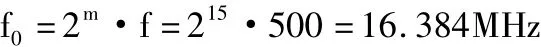

输出信号频率与频率控制字成正比.根据采样定理,所产生的信号频率不能超过系统时钟频率的1/2.为了保证信号的输出质量,输出信号的频率不能高于时钟频率的33%.例如,在地址加法器数据位宽为m=15的情况下,欲得到一个步长为500Hz的波形,则时钟频率f0为:

3 系统设计

3.1 系统参数设计

要输出比较好的正弦波形,理论上正弦波ROM里的一个周期点的数量越多越好.经过时序仿真,ROM中128或少于128个点仿真出来的波形都不太好.这里假设在ROM里取256个点.根据频率计算公式,要得到1MHz的波形,为了让ROM中每一个点都被读到,则n=8,所以f0/256=1MHz,由此系统时钟f0要大于等于256MHz.过高的频率可能会使电路板工作不稳定.因此,选择DE2能稳定工作的150MHz时钟作为系统时钟.又要达到步长小于等于100Hz,所以m大于等于21,取m=32.由于达不到256MHz以上,因此ROM中不可避免的有一些点没有读到,此时应尽量将ROM中的点数取大.经过仿真测试,1 024个点时得到的波形最好.综上,取系统时钟为150MHz,m=32,DATA为25位,ROM中点为1 024个.

3.2 各模块设计

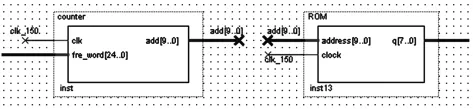

3.2.1 建立正弦波形存储器ROM

在使用QuartusII进行开发时,正弦波形存储器可以调用LPM_ROM模块来实现.为了对ROM模块内的数据进行加载首先应建立相应的*mif(Memory Initial File)文件.它可以用C语言(或者Matlab)编写源程序,描述正弦方程式,然后生成.mif文件.

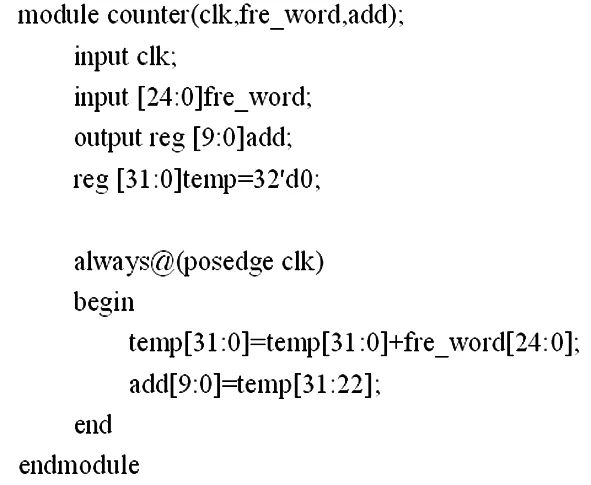

3.2.2 相位累加器和数据锁存器设计

相位累加器是DDS系统设计的核心,它决定着频率的范围和分辨率.本设计采用的是32位的二进制累加器和寄存器,其中累加器与寄存器在同一个模块中,并去锁存数据的高十位作为查表的地址值.Clk为系统时钟,fre_word为输入32位的频率控制字,address为输出后取十位的地址值.

相位累加器和正弦波模块如下:

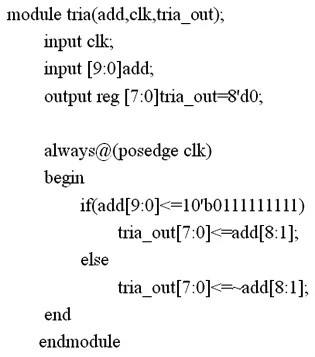

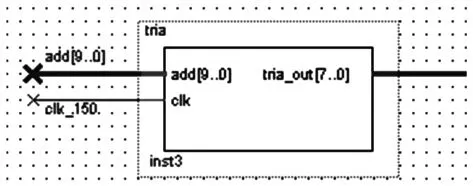

3.2.3 三角波的设计

三角波的生成原理,对输入地址address的值进行判断,当其最高位为0时,取地址的中间八位为输出值,当其最高位为1时,将中间八位取反后输入.

三角波模块如下:

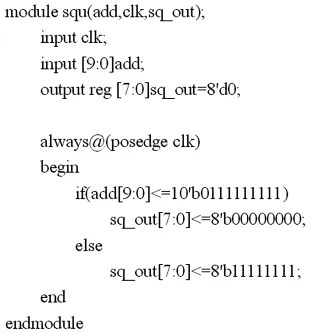

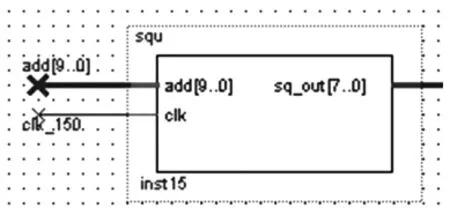

3.2.4 方波的设计

其原理如下,当地址数据的最高位为0时,输出为最大幅值为255.当地址数据的最高位为1时,输出为最低幅值0.

方波模块如下:

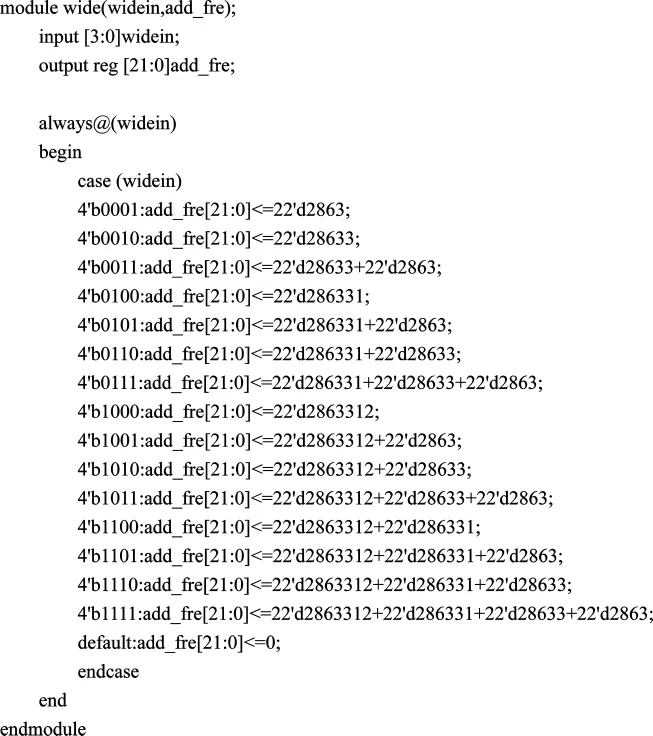

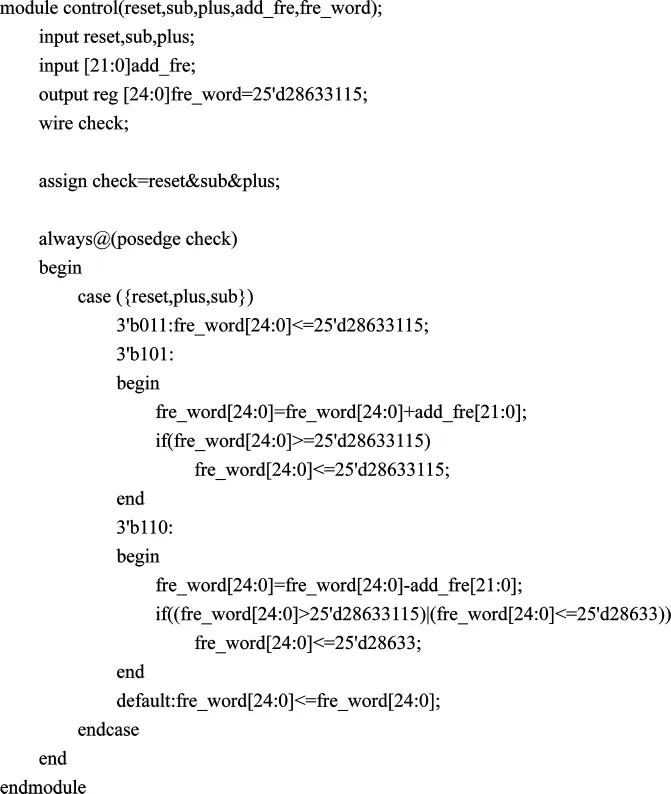

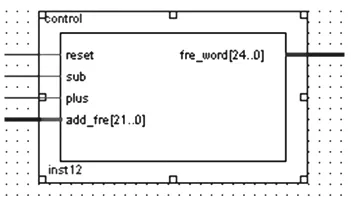

3.2.5 调整频率模块设计

更改频率实质上就是改变频率控制字的值.设计中采用四个拨码开关控制调整频率的档位,另三个按键分别控制reset(频率回到初始状态的1MHZ),plus(加频率),sub(减频率).采用两个模块设计,频率档位模块和频率调整模块.根据频率计算公式,步进值为100Hz、1KHz、10KHz、100KHz时频率控制字的改变量分别为 2 863、28 633、286 331、2 863 312,初始1MHz时频率控制字为28 633 115档位模块设计如下:

频率调整模块设计如下:

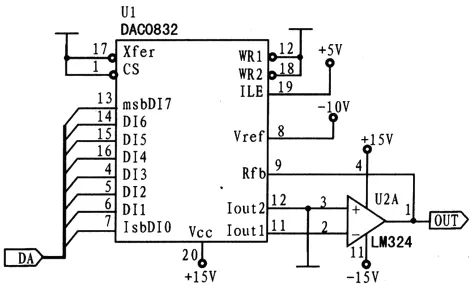

3.2.6 D/A 转换电路

数据转换器输出的数据是数字形式的电压值,为实现数字电压值与模拟电压值之间的转换,系统还专门设计D/A转换电路,其D/A转换电路原理图如图所示.

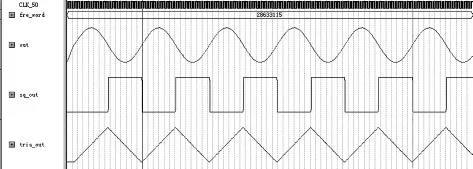

4 结果验证

仿真结果:

用示波器观察波形,在200KHz观察到的各种波形没有明显失真,能够正常通过按键切换波形和调整频率.观察结果表明,该系统输出的各种波形稳定,与设计要求一致.

5总结

本文在DDS工作原理的基础上,介绍基于FPGA实现DDS的设计方案,从测试结果可看出,该系统工作稳定,并具有一定的实用价值.

[1]Van Putten,Middeiheok S.Integrated silicon anemometer[J].Eiectronic Letters,1974,(10).

[2]阎石.数字电子技术基础(第四版)[M].北京:高等教育出版社,1998.

[3]田良.综合电子设计与实践[M].南京:东南大学出版社,2002.

[4]毛敏,郑珍,周渭.基于DDS的低通滤波器的设计与实现[J].电子技术,2006,(3):17 ~20.

TP33

A

1006-5342(2012)06-0037-03

2012-03-05