多层封装基板中同步开关噪声研究*

2012-09-05王洪辉孙海燕

王洪辉,孙海燕

(1.南通富士通微电子股份有限公司,江苏 南通,226006;2.南通大学专用集成电路设计重点实验室,江苏 南通,226019)

1 引言

在集成电路封装设计领域中,为了把不同半导体工艺制造的裸芯片和各种无源元件(电容、电感、电阻等)放置在同一个封装内,广泛采用高密度的多层封装基板[1~5]。同时随着高速集成电路的发展,电子系统正向小型化、高密度、低电压、低功耗等方向发展。电子系统的时钟频率不断提高,反射、振铃、串扰、同步开关噪声等信号完整性问题在封装设计中变得日益严峻。这其中,同步开关噪声指在数字系统中,多个有源器件同时开关引起瞬间快速变化的电流,在经过回流路径上存在的电感时,产生交流压降,从而引起噪声。同步开关噪声降低了数字电路的噪声容限,当多个有源器件同时开关时,所产生的同步开关噪声能够引起电源电压波动,导致时钟波形退化和封装内系统的干扰。

同步开关噪声是信号完整性典型问题之一。目前,同步开关噪声分析在高速电路设计中占有越来越重要的地位,已有多篇文献对同步开关噪声进行了研究[6~8]。因此,本文根据特定的封装对象对同步开关噪声进行研究,确保封装系统的可靠运行。

2 封装建模

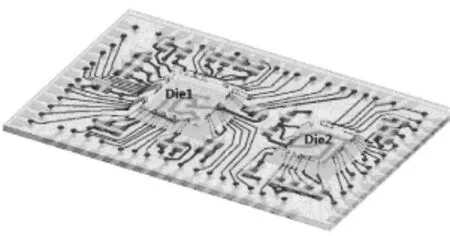

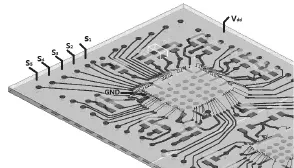

LGA(Land Grid Array)栅格阵列封装用金属触点取代了针状插脚,引线的阻抗小,适用于高速大规模集成电路封装。本文使用Sigrity公司的UPD软件进行LGA封装设计,如图1所示,整个封装由2个芯片和27个去耦电容组成,构成了一个典型的系统级封装。相应的模型参数见表1。

图1 LGA封装模型

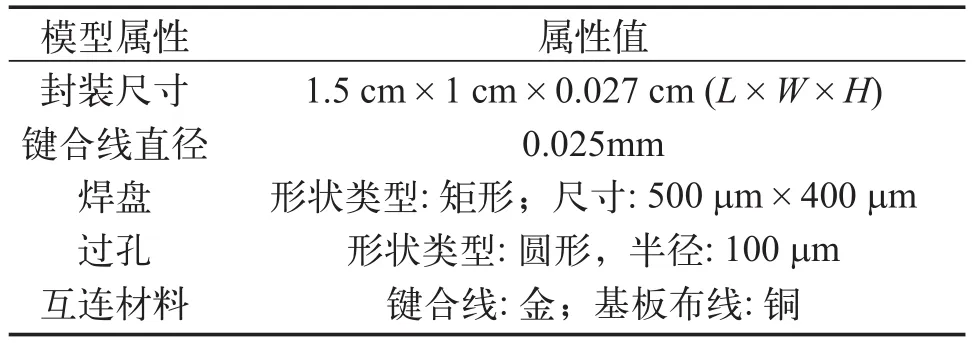

表1 LGA模型参数

3 仿真和分析

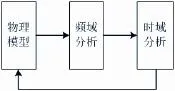

图2给出了简单的同步开关噪声的仿真流程。利用“场”和“路”相结合的方法进行仿真分析。首先对LGA封装模型进行“场”分析,即频域分析,采用Sigrity公司的频域仿真软件PowerSI分别对互连结构(键合线和信号走线)进行S参数仿真;然后进行“路”分析,即时域分析,在时域仿真软件Hspice中搭建同步开关噪声仿真电路,进行时域仿真获得同步开关噪声波形,最好将仿真结果重新应用到物理模型设计中,优化布局布线设计。

图2 同步开关噪声仿真流程

3.1 频域分析

信号传输的实质是电磁场能量的传输过程。本设计选取了S1、S2、S3、S4和S5共 5个重要的信号通道,如图3所示。每个信号通道分别由键合线、基板布线和通孔构成。电源供电网络Vdd以及参考平面GND也相应地做了定义。

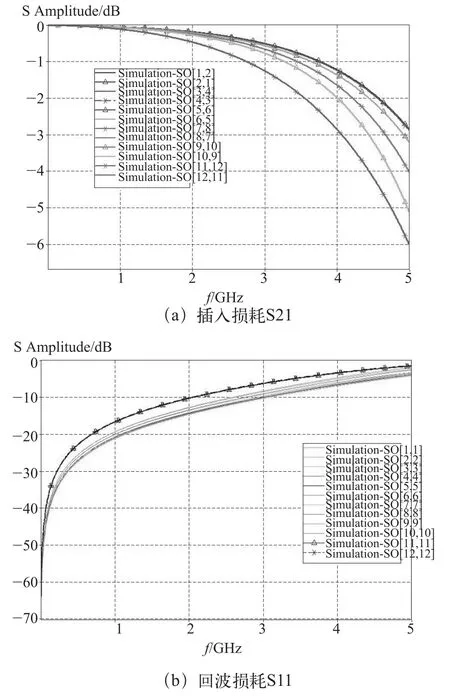

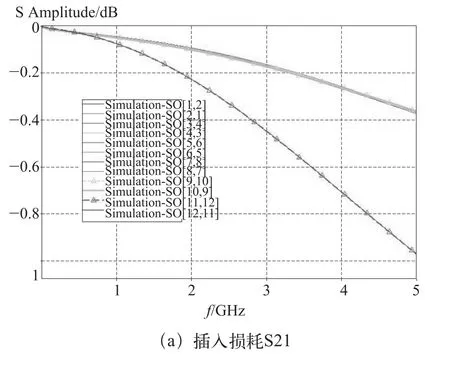

频域仿真时,为了更好地体现LGA封装中各个组件对信号的影响,将整个传输网络分成键合线和基板布线网络(含通孔)两部分。仿真起始频率均设置为1Hz,终止频率设置为5GHz,仿真步长是10MHz。图4和图5分别为键合线和基板布线网络得到的S参数,其中S21和S11分别定义为通道的插入损耗和回波损耗,定义S21=-1dB、S11=-10dB为参考标准,从图4中曲线分析可得,在整个频段内,除电源通道的键合线部分的S21损耗稍大点外,其余信号通道的键合线部分的带宽在-1dB之内均大于3GHz。同样,从图5分析可得,与键合线的S参数相比,基板上所有信号布线的|S21|在整个5GHz的带宽内均小于0.4dB,S11在整个5GHz的带宽内均小于-15dB,损耗均很小。与高电感值的键合线相比,基板布线可以灵活地进行阻抗设计,实现信号布线良好的阻抗匹配。此外,由于电源布线主要从电流密度分布的角度来考虑,采用了较宽的布线尺寸,在阻抗匹配上稍显差点,但并不影响系统的性能。

图3 选择的通道

3.2 时域分析

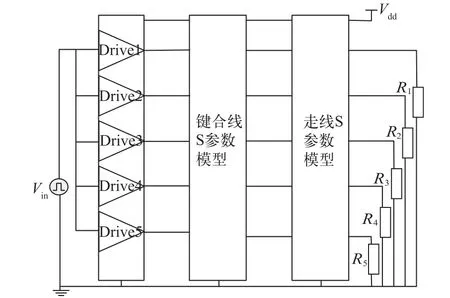

在时域分析中,主要是通过搭建同步开关噪声仿真电路来观察同步开关噪声波形。图6是同步开关噪声的仿真电路模型,主要由键合线和基板走线的S参数模型、驱动器、接收器、直流电源Vdd、理想信号源Vin组成。驱动器是由反相器组成,分别是Driver1、Driver2、Driver3、Driver4和Driver5。接收器由电阻组成,分别命名为R1、R2、R3、R4和R5。直流电源Vdd供电电压为2.85V。

图4 键合线的S参数

图5 布线的S参数

图6 同步开关噪声仿真电路

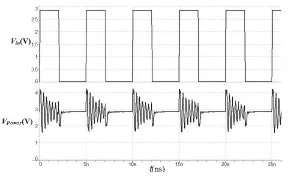

将图6所示的仿真电路模型描述为SPICE电路网表,然后将网表输入到Hspice中完成时域仿真。输入信号Vin,上升时间和下降时间设置为70ps,周期是5ns。模拟未添加去耦电容情况下5个驱动器同时切换对SSN的影响,仿真的结果如图7所示。从图7中可以看出,稳定的芯片供电直流电压由于同步开关噪声干扰而产生较大的起伏。Vin完成高低切换时产生的瞬间最大压差达1.25V。这严重影响了封装系统工作的可靠性。

图7 未添加去耦电容时产生的同步开关噪声波形

4 同步开关噪声的抑制

减小同步开关噪声已经成为封装和PCB设计中的难题之一。相关文献已提出了一些抑制同步开关噪声的方法:(1)添加去耦电容[9];(2)优化过孔位置[10];(3)采用电磁间隙结构(EBG)[11]。

本设计主要采用方法(1),即添加去耦电容来减少同步开关噪声。

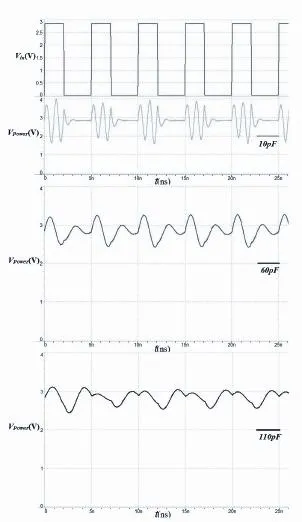

图8 不同容值的去耦电容对SSN的抑制效果

通常,去耦电容的位置一般放置在基板中谐振明显的波峰和波谷处。通过谐振分析,本例中去耦电容在基板上的位置如图1所示。利用Hspice分别模拟容值为10pF、60pF和110pF的去耦电容对SSN的影响,去耦效果如图8所示。从图中分析可得,与未添加去耦电容的波形相比,添加10pF、60pF和110pF的去耦电容能够明显减少波峰和波谷的数量,波峰电压值与标准输入电压的压差分别减少到1.2V、0.48V和0.32V。由此可知,本设计中较大容值的去耦电容对SSN有较好的抑制作用,满足设计要求,因此本设计选择容值为110pF的电容作为去耦电容。

5 总结

本文分析了一种LGA封装基板的同步开关噪声特性,采用UPD工具建立封装物理模型,然后采用PowerSI工具进行电磁分析,提取S参数,最后利用HSPICE工具进行同步开关噪声仿真,同时提出了通过添加去耦电容来抑制同步开关噪声的方法。仿真结果表明本设计中通过在基板上谐振明显的位置添加110pF容值的去耦电容可以明显减少波峰和波谷的数量,压差减少至0.32V,满足设计的要求。

[1]Solberg V, Oganesian V. High Density Substrate Solution For Complex High Pin Count Flip-Chip Application[C].IEEE International Conference on Combined Pre Medical Test, 2010:24-26.

[2]Fuhan Liu, Sundaram, V, Wiedenman B, etc. Fine Line Photolithography and Ultra High Density Package Substrate for Next Generation System-on-Package(SOP)[C].IEEE International Conference on Electronic Packaging Technology, 2007:1-5.

[3]Hiraga k, Seki T, Nishikawa k, etc. Multi-Layer Coupled Band-Pass Filter for 60 GHz LTCC System-on-Package[C]. IEEE International Conference on Microwave,2010:259-262.

[4]Bharathy K, Jae Young Choi, Swaminathan M. Use of the Finite Element Method for the Modeling of Multi-layered Power/Ground Planes with Small Features[C]. IEEE International Conference on Electronic Components and Technology, 2009:1630-1635.

[5]Chanchani R, Bethke D.T, Webb D.B, etc. Development and RF Characterization of High Density Integrated Substrate Technology[J]. IEEE Transaction on Components and Packaging Technologies, 2007, 30(3):478-485.

[6]Kyoungchoul Koo, Yujeong Shim, Changwook Yoon, etc.Modeling and Analysis of Power Supply Noise Imbalance on Ultra High Frequency Differential Low Noise Amplifiers in a System-in Package[J]. IEEE Transaction on Advanced Packaging, 2010,33(3):602-616.

[7]Jongbae Park, Hyungsoo Kim, Youchul Jeong, etc.Modeling and Measurement of Simultaneous Switching Noise Coupling Through Signal Via Transition[J]. IEEE Transactions on Advanced Packaging, 2006, 29(3):548-559.

[8]Junwoo Lee, Mihai Dragos Rotaru, Mahadevan K.Iyer, etc.Analysis and Suppression of SSN Noise Coupling Between Power/Ground Plane Cavities Through Cutouts in Multilayer Package and PCBs[J]. IEEE Transaction on Advanced Packaging, 2005, 28(2):298-309.

[9]Frank Y. Yuan. Signal Integrity Analysis of Simultaneous Switching Noises and Decoupling Capacitors in Digital Packages and PCB Systems[C]. IEEE International Conference on electrical performance of electronic packaging, 1996:132-134.

[10]Xiao Xiao Wang , Dong Lin Su, V. The Influence of Power/Ground Resonance to Via’s SSN Noise Coupling in Multilayer Package and Three Mitigating Ways[C].IEEE International Conference on electronic materials and packaging, 2006:1-5.

[11]Kong Xi, Jin Jie, Lu Lin. A novel PCB power planes design with an EBG structure used to eliminate theSSN[C]. IEEE International Conference on wireless communications, networking and mobile computing,2011:1-4.