PSOC在低频信号发生器中的应用

2012-07-07韩喜春高旭东张春艳

韩喜春,高旭东,张春艳

(黑龙江工程学院 电子工程系,黑龙江 哈尔滨150050)

信号发生器又称信号源或函数发生器,在生产实践和科技领域中有着广泛的应用。各种波形曲线均可以用函数方程式来表示,产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。函数信号发生器在电路实验和设备检测中具有十分广泛的用途。实现信号发生器的方案很多,可以用模拟电路、数字电路或数字和模拟混合电路,也能以FPGA、MCU或DSP为核心实现。Cypress公司的PSOC混合信号阵列是可编程的片上系统(SOC),其集成了微控制器以及嵌入式系统中通常围绕微控制器周围的模拟及数字组件。采用一个微控制器、一个PSOC器件最多可集成100多种外设功能,从而帮助客户节约设计时间和板上面积,降低功耗。方便易用的开发工具Creator使设计人员能够准确选择所需的外设功能,包括放大器、ADC、DAC、滤波器及比较器等模拟功能以及定时器、计数器、PWM、SPI和UART等数字功能。本文采用以PSOC芯片的DMA(直接存储器存取)为核心元件的函数信号发生器的设计方法。

1 虚拟信号发生器的系统结构

基于PSOC的虚拟信号发生器的系统结构如图1所示。本信号发生器所产生的正弦波、三角波、锯齿波、PWM波和自定义波形的软件和硬件均由PSOC内部实现。上位机通过USB串行接口将控制波形数据传输到PSOC,PSOC根据控制参数设置内部元件产生预订频率的波形,控制参数并且送到LCD输出。由PSOC产生的波形再送到低通滤波器和衰减电路变换后输出。

图1 信号发生器的系统结构

2 信号发生器的固件元件原理图设计

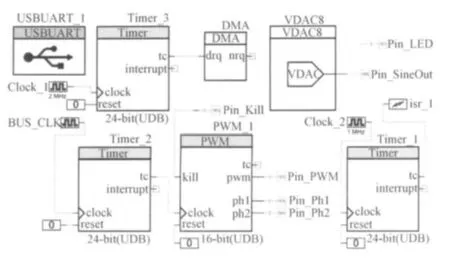

开发PSOC主要有两个阶段:原理图设计阶段和程序设计阶段。PSOC在Creator的IDE(集成开发环境)设计出的固件元件原理如图2所示。PSOC信号发生器的原理图设计大体可分为以下几步:打开PSOC Creator软件,新建一个工程项目,在弹出的“New Project”窗口中选择“Empty PSoC3Design”,要是用PSOC5,选择“Empty PSoC5 Design”,为新工程取一个名字,在默认情况下,PSoC Creator会打开一个名为“TopDesign.cysch”的文件,在这里将完成原理图的设计。原理图的设计与在Protel中画原理图类似,在IDE的右边,会有一个元件目录可以直接使用其中的元件,当然也可以自己创建元件;原理图的设计就基本上完成了,但是要在FPGA中一样对引脚进行锁定,可以把引脚锁定到任何你想要的GPIO(通用外围输入输出)上,这也是PSOC的一个优势,引脚相当灵活,任何一个GPIO都能用作数字或模拟引脚。

图2 信号发生器的固件元件原理

对于原理图中的元件,有些需要对其属性进行配置,有两种方法:一种是在程序中对其进行配置,每一个原理图中的元件都会有相应的API(应用程序接口)函数与之对应,详细的说明可以右击元件,在出现的下拉菜单中选择“Open Data Sheet...”打开其技术文档进行查找;另一种方法是直接在原理图中对其进行配置,这也是常用的方法,双击元件,即可对其进行配置,配置参数也请参考其技术文档。也可以将工程编译,在工程浏览器中会显示出元件的C语言程序和头文件,打开C语言文件找到对应的API函数。限于篇幅,下面说明几个主要元件的属性配置。

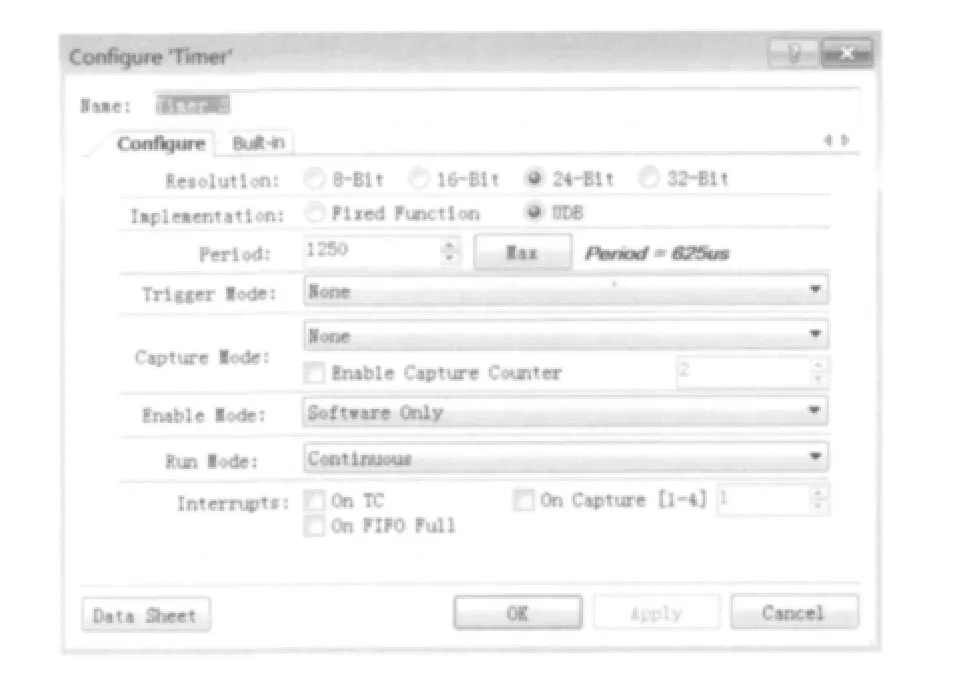

2.1 定时器的属性设置

定时器Timer_3的Clock端由Clock_1提供2MHz时钟,Clock_1是可编程时钟器件,reset端置0启动。定时器Timer_2的Clock端由BUS_CLK提供48MHz时钟。定时器的属性配置如图3所示。Timer_3的终止计数端tc产生的脉冲作为DMA元件的DMA请求时钟,每一个tc时钟周期产生1次DMA请求,通过程序中API函数修改定时器的周期达到控制DMA频率。定时器Timer_2的tc作为PWM的时钟。定时器的最高分辨率是32位。定时器在产生tc脉冲时可以产生中断,也可以在tc端接中断元件isr。定时器timer_1的tc中断用于定时查询USB端口数据,设置与输出信号相关的各个元件的属性参数。

图3 定时器Timer的属性配置

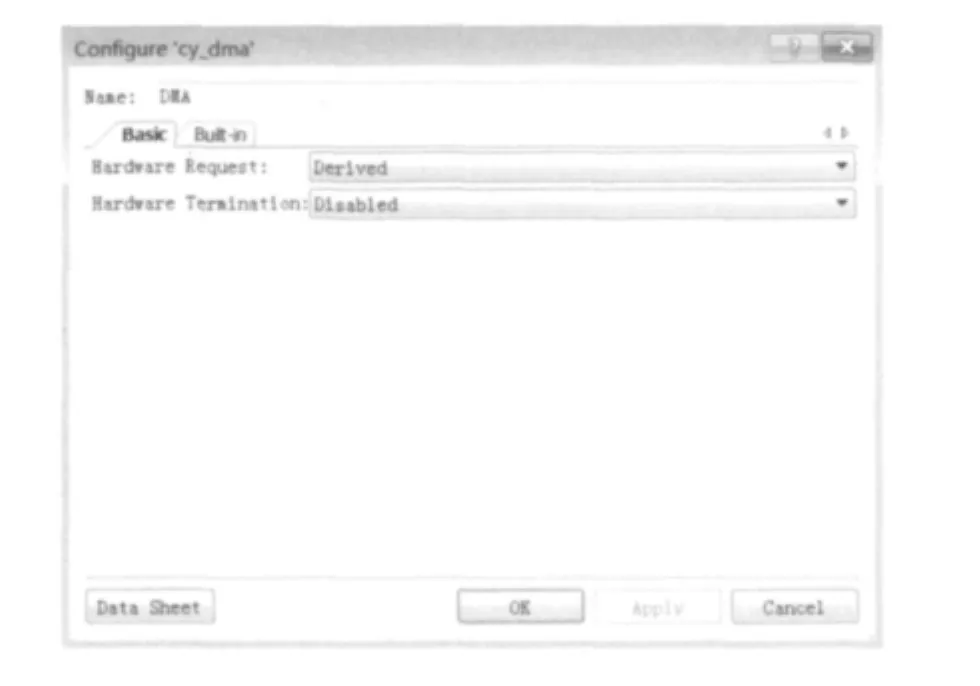

2.2 DMA的属性设置

直接内存访问(DMA)是一种完全由硬件执行I/O交换的工作方式。在这种方式中,DMA控制器从CPU完全接管对总线的控制,数据交换不经过CPU,而直接在内存和I/O设备之间进行 。DMA方式一般用于高速传送成组数据。DMA控制器将向内存发出地址和控制信号,修改地址,对传送的字的个数计数,并且以中断方式向CPU报告传送操作的结束。DMA方式的主要优点是速度快。由于CPU根本不参加传送操作,因此,省去了CPU取指令、取数、送数等操作。在数据传送过程中,没有保存现场、恢复现场之类的工作。内存地址修改、传送字个数的计数等等,也不是由软件实现,而是用硬件线路直接实现。所以DMA方式能满足高速I/O设备的要求,也有利于CPU效率的发挥。在本设计中,每个定时器周期产生1次DMA操作,每次DMA操作将1个字节的波形数据输出到数模转换器VDAC8。假如定时器Timer_2的tc端的输出频率是Fc,一个周期波形数据的长度是256,则信号发生器所产生的正弦波、三角波和锯齿波的频率是F0=Fc/256Hz。本设计中,Fc的取值不能大于1MHz。

在工程菜单的Tools中选择DMA向导对DMA的源地址、目的地址、每次DMA操作传输的字节数以及触发信号极性等参数进行设置,设置完成后自动产生在工程浏览器中可见的C语言API函数的DMA元件源代码。对DMA的属性配置如图4所示。

图4 DMA的属性配置

2.3 脉冲宽度调制PWM的属性配置

PWM的配置内容较丰富,只选择与本设计密切的几项介绍,对PWM的配置如图5所示。定时器给PWM提供可编程时钟频率为Fa,PWM的输出频率(通过设置PWM的周期参数为P)为Fb,则Fb=Fa/P。在信号发生器工作时通过程序改变Timer_2和PWM的周期都可以改变输出脉冲波的频率。改变参数比较值的大小可以改变输出波形的占空比。如果要控制电机,通过设置死区的时钟数产生两相PWM波形。分辨率设置为16位,实现方法采用通用数字块UDB。

3 信号发生器的软件设计

图5 PWM的属性配置

PSOC Creator的图形设计编辑器将嵌入式系统设计的软硬件融合在一个设计环境中。其内容丰富的外设库能提供上百个预先配置好的模拟和数字外设,可以轻松拖放元件到电路图中,为所有片上信号设置传输通路,将元件的输入和输出端点在原理图内互连或分配给PSOC芯片的引脚。每个外设元件都经过仔细的参数配置,因而在使用中可以自动优化,以适应开发者的需求,而不必浪费资源。“创建”(Build)过程会为每个元件生成具有一致性、容易记忆的一系列API,使软件开发者得以控制硬件,而无需担心基本的操作。Cypress还为PSOC3和PSOC5系列器件提供全功能的免费编译器,并且没有代码量的限制。

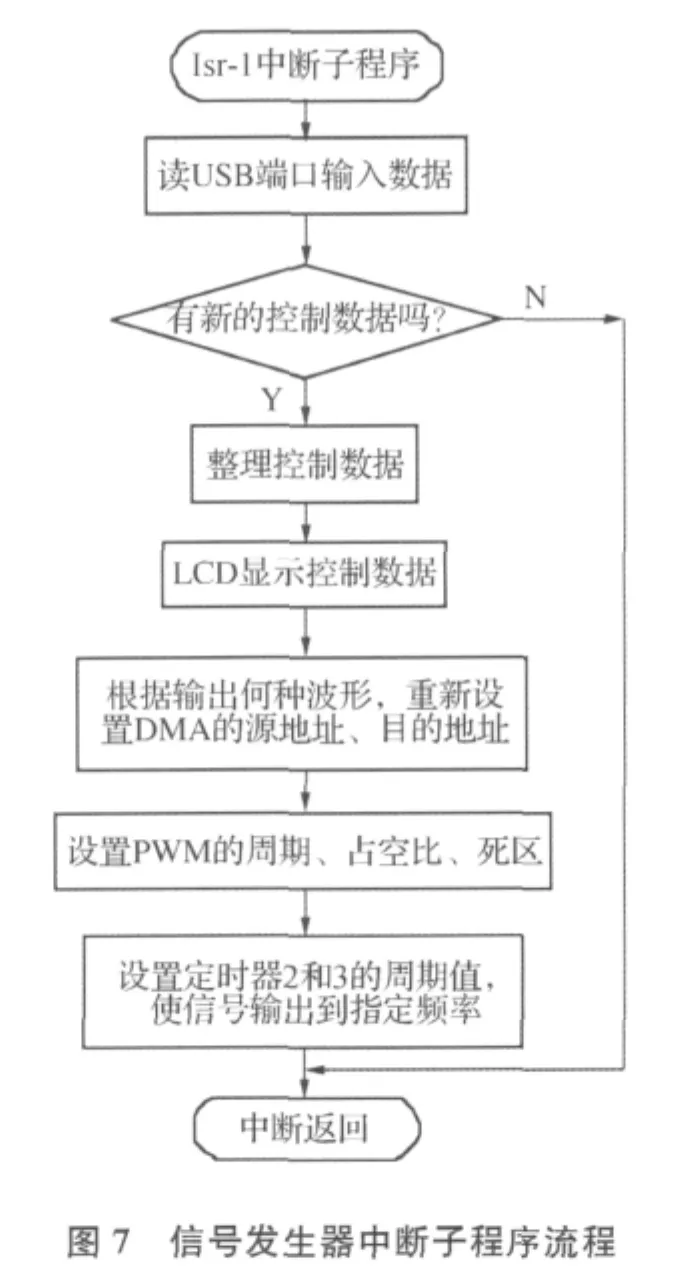

设计完原理图之后,需要点击一下Build创建,这样系统就会自动生成需要的各种文件,编译完成后你会发现,工程目录中多了很多文件。系统默认在“main.c”中写主函数,在程序中,你需要调用各种元件的API来完成对元件的操作,这些API函数可以在元件的技术手册中找到。本项目的软件程序设计包括main主程序和isr_1的定时器中断子程序设计。程序的流程如图6和图7所示。在main程序中,首先调用各元件的初始化和启动函数对各个元件进行初始化和启动,然后打开全局中断,接着初始化DMA,在初始化函数中,设置每次DMA操作需要1次请求,每次请求传输1个字节,传输的源地址(波形数据表的首地址)和目的地址(VDAC8的地址),一个DMA周期传输的字节数(波形数据表的长度),启动DMA数据传输。接着开始程序无限循环,在循环中查询设置的中断标志位是否有中断发生。在定时器中断子程序中读取USB接口,看是否有新的数据输入,没有新数据就结束中断子程序;如果有新数据,按通信协议定义的数据格式,将频率控制字(定时器的周期值)送入Timer_2和Timer_3,脉冲波的周期和占空比以及死区送入PWM。

4 结束语

本虚拟低频信号发生器在PSOC开发工具CY8CKIT001进行了设计验证。该信号发生器的模拟信号频率范围为0.01~10kHz,受VDAC8的上限频率1MHz限制。在整个测量频率范围内与安捷伦53131A的测量结果对比,最大频率误差正负2Hz。产生误差的原因是PSOC的可编程时钟精度只有1%,PWM 信号的频率范围是1Hz~1MHz。

PSOC器件采用一种针对嵌入式控制设计的高度可配置片上系统架构,除了集成一个片上微控制器外,还集成了可配置模拟和数字电路,提供了更强大的设计修改功能。单一PSOC器件集成100多个外设功能元件,从而节省客户的设计时间、板级空间和功耗,同时改善系统质量并降低系统成本。PSOC 3器件具有一个高性能8位8051处理器,而PSOC 5则采用一个强大的32位ARM Cortex-M3处理器。这些产品为设计者提供了一个无缝的可编程平台,能轻松实现8~32bit的转换。这些解决方案的强大功能大大拓展了PSOC的应用和市场范围,包括汽车、便携式医疗、工业等等。本文介绍的低频信号发生器设计只用了PSOC器件很少资源,在图形化编程环境Creator的支持下,减少了开发难度,缩短了开发周期,提高了产品的易用性和可靠性。PSOC是嵌入式系统设计中很有发展前途的一种器件和设计思想。

[1]唐颖,梅海波.单片数控信号发生系统的SOPC技术设计与实现[J].自动化仪表,2008,29(4):96-98.

[2]王广昊,肖明清,高成金.基于FPGA的可重构智能仪器设计[J].微计算机信息,2009,10(2):159-161.

[3]周遐,金瑞,曹云川.基于DDS技术的高精度数控信号源设计[J].昆明理工大学学报:理工版,2009,34(5):50-53.

[4]罗杰汉,程光伟.基于FPGA的DDS设计[J].电子设计工程,2010,18(1):66-70.

[5]钱永青.基于DDS技术正弦信号发生器的设计[J].现代电子技术,2008,31.

[6]刘明成,孙景瑞.基于DDS芯片的信号源应用计[J].天津师范大学学报,2008,10:35-36.

[7]冯煦,钟卫,胡亮,等.基于DDS的多调制功能正弦号发生器[J].国外电子测量技术,2010,1:39-41.

[8]黄志伟.全国大学生电子设计竞赛训练教程[M].北京:电子工业出版社,2005.

[9]黄雪梅,胡建生,魏功辉,等.DDS技术实现可调信号发生器[J].现代电子技术,2008,31(9):80-81.

[10]韩喜春,高旭东,张春艳.基于PSOC的通用计数器设计[J].黑龙江工程学院学报:自然科学版,2011,25(3):48-52.