关于EDA教学中Quartus II原理图输入法的探讨

2014-03-23于明军

于明军

(赤峰学院 物理与电子信息工程学院,内蒙古 赤峰 024000)

关于EDA教学中Quartus II原理图输入法的探讨

于明军

(赤峰学院 物理与电子信息工程学院,内蒙古 赤峰 024000)

本文介绍FPGA/CPLD开发软件QuartusII的原理图输入法,举例说明原理图输入设计法的基本知识,并对原理图输入设计法作进一步的深入讨论.

EDA;QuartusII;原理图输入法

1 引言

现代电子设计技术的核心就是EDA(电子设计自动化,ElectronicDesignAutomation)技术.在QuartusII中,VHDL输入和原理图输入都能完成FPGA的设计,他们的地位是均等的.两种输入之间可以互相转换和互相调用,两者仅为表述形式的不同,其结果都能形成RTL级描述.在VHDL输入中的元件例化,就是文字表述的原理图输入.在原理图中的元件符号,就是封装好的VHDL输入元件,此元件还需要对应的VHDL输入文件给出其功能,才能在原理图输入中形成RTL级描述.两种输入可自由选择,按使用习惯进行FPGA设计,无需特意区分.原理图输入法表示的优点是直观、方便.

2 Quartus II原理图输入法设计时钟

原理图输入方式是利用EDA工具提供的图形编辑器以原理图的方式进行输入.应用数字逻辑电路的基本知识,使用QuartusII原理图输入法可非常方便地进行数字系统的设计.原理图输入方式比较容易掌握,直观且方便,所画的电路原理图(请注意,这种原理图与利用Protel画的原理图有本质的区别)与传统的器件连接方式完全一样,很容易被人接受,而且编辑器中有许多现成的单元器件可以利用,自己也可以根据需要设计元件.

本文以时钟设计为例,说明QuartusII原理图输入法的基本步骤,先设计十二进制和六十进制计数器,再通过层次化设计调用完成对时钟的设计.

2.1 建立工程文件夹

2.1.1 新建一个文件夹作为工程项目目录

首先在计算机中建立一个文件夹作为工程项目目录,此工程目录不能是根目录,比如D:,只能是根目录下的目录,比如D:QuartusIIcntm12.

2.1.2 建立工程项目

工程是不同的数字系统设计作品的装载物.在Quartus II中以工程作为设计的独立单位.工程中有顶层设计文件和底层设计文件,其关系是调用和被调用的关系.工程(工程文件夹名)、顶层设计文件和VHDL输入(原理图输入)的文件名需要一一对应.

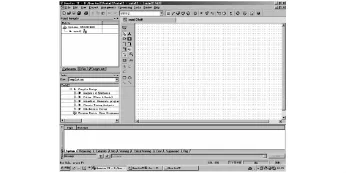

运行QuartusⅡ软件,执行File→NewProjectWizard…命令,建立工程.在所弹出的图1所示的NewProject Wizard对话框中,分别填写各个项目.其中第一、第二、第三文本框分别是工程项目目录、项目名称和项目顶层设计实体的名称.单击Finish按钮就建立了一个空的工程项目.

图1 工程项目基本设置

2.2 编辑设计图形文件

2.2.1 建立原理图文件

执行File→New…命令,选择BlockDiagram/Schematic File流程图和原理文件.再执行File→Saveas…命令,把它另存为文件名是cntm12的原理图文件,文件后缀为.bdf.将Addfiletocurrentproject选项选中,使该文件添加到刚建立的工程文件中去.

QuartusⅡ支持五中设计输入法文件:AHDLFile是AHDL文本文件;BlockDiagram/SchematicFile是流程图和原理文件,简称原理图文件;EDIFFile是网表文件Verilog HDLFile是VerilogHDL文本文件;VHDLFile是VHDL文本文件.选择BlockDiagram/SchematicFile,单击OK按钮即建立一个空的原理图文件.

2.2.2 编辑输入原理图文件

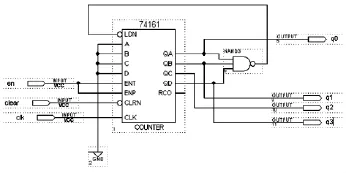

图形编辑界面如图2所示,其右侧的空白处就是原理图的编辑区,在这个编辑区输入图3所示的十二进制计数器原理图.

2.3 编译设计图形文件

完成原理图编辑输入后,保存设计图形文件,就可编译设计图形文件.执行Processing→StartCompilation,进行编译.编译结束后,会出现对话框显示编译的错误和警告情况.若有错误,则可双击编译器界面下方出现的第一个错误提示,使第一个错误处改变颜色.检查纠正第一个错误后保存再编译,如果还有错误,重复以上操作,直至最后通过.最后通过时应没有错误提示但可有警告提示.可以通过查看编译报告了解有关情况,比如定时分析情况.以上是使用QuartusⅡ编译器默认设置进行的编译方法,还可以先根据需要进一步的编译设置,然后再编译,具体方法可参考QuartusⅡ帮助文档.

2.4 时序仿真设计文件

图2 图形编辑界面

图3 十二进制原理图

图4 仿真结果

2.5 生成元件符号

执行File→Greate/Update→Greate Symbol Files for Current File命令,将本设计电路封装生成一个元件符号,供以后在原理图编辑器下进行层次设计时调用,所生成的符号存放在本工程目录下,文件名cntm12,文件后缀名为.bsf.调用方法与QuartusⅡ提供的元件符号相似.用以上同样的方法完成六十进制计数器的设计,并生成符号.

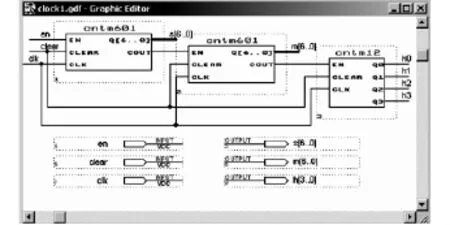

2.6 图形的层次化设计

首先新建一个工程文件夹clock把十二进制计数器的cntm12.bdf、cntm12.bsf文件和六十进制计数器的cntm60.bdf、cntm60.bsf文件放入其中,再新建一个原理图文件,使用符号插入命令,选择cntm12.bsf、cntm60.bsf将它放置于原理图编辑区中即可实现调用.完成的原理图如图7所示.

图5 六十进制计数器原理图

图6 六十进制计数器仿真波形

图7 clock的原理图

图8 clock的仿真波形

3 结语

EDA课程是高校电类专业一门重要的工程实践类课程,在工程设计中,QuartusII软件的原理图输入法简单易用,是初学硬件设计的首选方法,本文以实例方式对其进行了详细的阐述,对软件的学习有一定的指导作用.

〔1〕廖超平.EDA技术与VHDL实用教程[M].高等教育出版社,2007.

〔2〕闫石.数字电子技术基础[M].高等教育出版社,2006.

〔3〕侯伯亨.VHDL硬件描述语言与数字逻辑电路设计[M].西安电子科技大学出版社,2009.

G642

A

1673-260X(2014)01-0224-02