X波段线性调频信号源的设计

2011-04-17邓潘陈卫

邓潘 陈卫

(解放军电子工程学院,安徽 合肥 230037)

X波段线性调频信号源的设计

邓潘 陈卫

(解放军电子工程学院,安徽 合肥 230037)

X波段线性调频信号源已在多个领域得到广泛应用。采用直接数字频率合成(DDS)激励锁相频率合成(PLL)的技术,可以弥补各自的缺点,设计了X波段(10GHz~10.5GHz)线性调频信号源的实现方案,并对信号源的频率建立时间和相位噪声进行了仿真,重点研究了基于AD9854的锁相环激励信号源的设计。

DDS PLL X波段 线性调频 信号源

0 引言

X波段线性调频信号源广泛应用于雷达、通信等领域,通常用频率合成的方法来实现。频率合成技术主要分为三类:直接模拟式频率合成技术(DAS)、间接锁相式频率合成技术(PLL)和直接数字式频率合成技术(DDS)[1]。直接模拟式频率合成需要大量的晶体、滤波器、混频器等硬件,所以难于集成而逐渐被淘汰;PLL具有极宽的频率范围、良好的寄生抑制性能、输出频谱纯度很高,但频率转换速度慢,频率分辨率不高;DDS技术有频率转换速度快、频率分辨率高、输出相位连续、相位噪声低等突出优点,得到了广泛应用,但是由于其全数字的结构,存在输出带宽窄和杂散抑制差的缺点。由此可见,PLL技术和DDS技术相结合,可获得高性能的信号源[2]。

DDS技术与 PLL技术的组合方式通常有两种[2]:一种是DDS激励PLL式的频率合成方案,另一种是用DDS与PLL混频的频率合成方案,分为环外混频和PLL内插DDS两种。前者可以达到低相噪、宽带宽、小步进的要求,所以在设计实现X波段(10GHz~10.5GHz)的线性调频信号源时,采用DDS激励PLL式的频率合成方案。

1 DDS激励PLL式的频率合成方案

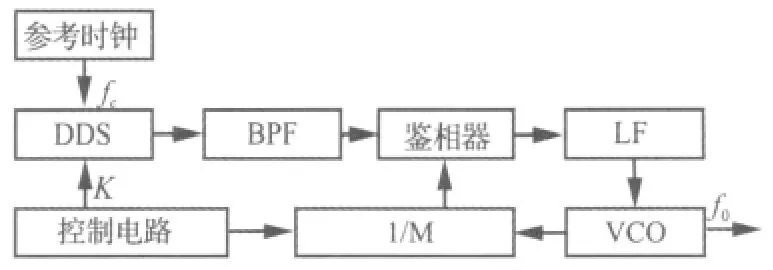

DDS激励PLL式的频率合成方案如图1所示。DDS的输出信号作为PLL的激励源,PLL作为跟踪倍频锁相环,当锁相环稳定时,频率合成器的输出频率为

其中,fc为DDS的时钟频率,N为DDS相位累加器的字长,K为DDS的频率控制字,M为锁相环路的可编程分频比。

该方案实现了DDS技术和PLL技术的优势互补,兼顾了各方面的性能,可做到很高的输出频率、较快的频率切换速度、高的频率分辨率,同时也能很好的保证系统杂散和相位噪声性能。

2 X波段线性调频信号源的设计方案

本文采用DDS激励PLL式的频率合成方案,来设计实现X波段(10 GHz~10.5 GHz)的线性调频信号源。DDS输出线性调频信号,作为锁相环的参考信号。

图1 DDS激励PLL式的频率合成原理框图

锁相环芯片采用ADF4108。ADF4108工作带宽为8 GHz,内含一低噪数字鉴相器、精密电荷泵、可编程的14位参考R分频器、6位可编程A计数器、13位可编程B计数器和可编程双模预分频器(P/P+1),可实现N倍分频(N=B·P+A)。使用时外加环路滤波器和VCO即可构成一个完整的PLL[3]。

本设计中的VCO采用Hittite公司的HMC588LC4B,其输出频率范围为8 GHz~12.5 GHz,输出功率为5 dBm。图2为用ADISimPLL3.0软件仿真得出的ADF4108驱动HMC588LC4B的仿真原理图。其中,鉴相器鉴相频率为500 kHz,外部参考时钟为10 MHz,计数器R=20,环路滤波电路采用了二阶有源滤波电路。

图3为10.49931时PLL的频率建立时间仿真图,图中可以看出,约经过 30.62 μs,PLL 可将输出频率锁定在 10.49931GHz。

信号源的相位噪声主要由以下因素组成:鉴相器、环路滤波器、分频器的相位噪声和参考时钟的相位噪声以及VCO的相位噪声。其中环路分频比N对环路带宽内的相位噪声影响最大,将恶化20 lgNdB。在环路带宽外的相位噪声主要由VCO决定,而HMC588LC4B的相位噪声指标能满足本设计需要。

图2 10 GHz~10.5 GHz锁相频率源的仿真原理图

图4为10.2 GHz时锁相环输出信号的相位噪声分析图,表1为各主要部分的相噪分析报表,在偏离载频10 KHz时,相位噪声为 -79.01 dBc/Hz,在偏离载频100 KHz时,相位噪声为 -85.00 dBc/Hz。分析表明此设计方案的相位噪声指标符合设计要求。

表1 PLL各部分的相位噪声分析报表

3 基于AD9854的锁相环激励信号源的设计

按照上述设计方案,以AD9854输出的线性调频信号作为ADF4108的激励信号。

AD9854具有4~20倍可编程时钟倍频器,系统时钟最高可达300 MHz,输出信号频率可达120 MHz。AD9854内部有双48位可编程频率寄存器、双14位可编程相位偏移寄存器和12位可编程幅度控制寄存器等模块,可以很方便地实现AM、FM、FSK、BPSK、PSK和线性调频信号,因此广泛应用于通信、雷达中的频率合成[4]。

图5所示为采用AD9854实现PLL激励信号源的电路框图,主要包括电源调整电路、差分时钟电路、控制电路和低通滤波电路。

图5 基于AD9854的PLL激励信号源电路框图

为防止数字电路的电源噪声耦合到模拟电路电源上,确保电路各部分供电稳定、互不干扰,因此对AD9854采用模数分离供电方式。整个激励信号产生电路选用了3片集成电压转换芯片AMS1117 -3.3,该芯片输出电压浮动不超过2%[5]。

AD9854的参考时钟即可采用单端输入又可采用差分输入,为抑制共模噪声,改善参考信号质量,通过差分时钟芯片MC100LVEL16将30MHz单端有源晶振信号转换成差分信号,作为AD9854的参考时钟。同时,MC100LVEL16还起到了共模电压搬移,差分时钟幅度调整的作用。

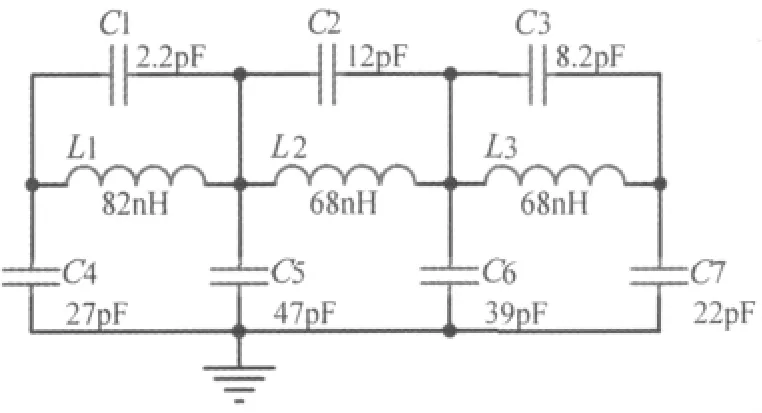

AD9854的内部没有为正弦DAC设置平滑滤波器,输出信号为阶梯波,含有幅值包络为辛格函数的高频谐波,必须外接LPF来抑制无用的高频分量。LPF采用120MHz的7阶椭圆滤波器,电路图如图6所示。运用ADS软件对其进行仿真,结果如图7所示。AD9854可比较方便地合成线性调频信号,但是输出信号杂散较大,且输出杂散种类复杂,有参考时钟引入的杂散、相位截短杂散、相位幅度转换杂散、DAC谐波杂散、DDS内部数字信号产生的杂散和PCB布线不当导致的杂散。为提高AD9854输出信号质量,减小杂散,必须针对不同来源的杂散采取相应抑制手段:一是采用低相噪、高精度和频率稳定度的参考时钟;二是进行合理的频率规划,找到参考时钟频率和输出信号频率之间的最佳关系;三是进行认真、细致的PCB布局、布线,例如尽量采用差分信号,合理的电源、地层设计等。

图6 120 MHz的7阶椭圆LPF的电路图

图7 120 MHz的7阶椭圆LPF的仿真图

4 结束语

以DDS激励PLL的技术方案设计了10 GHz~10.5 GHz频段线性调频信号源,并对信号源的主要时频域指标进行了仿真分析。结果表明,该方案设计的X波段信号源在10.49931 GHz输出频率的锁定时间为30.62μs,在10.2 GHz输出频率的相位噪声为-79.01 dBc/Hz@10kHz,其时频域指标符合设计要求。最后研究了基于DDS芯片AD9854的锁相环激励信号源的设计,详细给出了关键部分的电路设计原理。

[1]冯源,邹继伟,陈卫.现代频率合成技术的发展与趋势[J].电子对抗,2010(3):45-49.

[2]郭德淳,费元春.DDS的杂散分析及频率扩展研究[J].现代雷达,2002,24(1):63 -66.

[3] ADF4106 Datasheet[M].Analog Devices Inc.,2002.

[4] AD9854 Datasheet[M].Analog Devices Inc.,2002.

[5] ATmega8515/ATmega8515L Data-sheet[M].Atmel Corp.,2003.

Design of X-band LFM Signal Source

Deng Pan Chen Wei

(ElectronicEngineeringInstituteofPLA,HefeiAnhui230037,China)

X-band LFM signal source is widely applied in many areas.On the basis of DDS-driven PLL,this paper makes up for their short comings,the scheme of the LFM signal source in X-band(10GHz~10.5GHz)was designed.The frequency locked time and phase noise of signal source were simulated.Based on AD9854,the source-driven PLL was further designed.

DDSPLL X-band LFM Signal Source

TN74

A

1000-3886(2011)04-0075-02

2010-10-14

邓潘(1981-),女,讲师,研究方向:主要从事高功率微波武器研究。 陈卫(1979-),男,讲师,研究方向:主要从事精导防御研究。