基于FPGA中断管理的研究及硬件化设计

2011-03-15贾小梨迟欢欢

李 岩 ,贾小梨 ,迟欢欢

(1.哈尔滨理工大学 计算机科学与技术学院,黑龙江 哈尔滨150080;2.黑龙江省卫生学校,黑龙江 哈尔滨150086)

航空航天、工业控制和核电站建设等领域的发展,对嵌入式操作系统的实时性要求越来越高。随着FPGA的集成度和速度的不断提高,嵌入式操作系统由硬件实现成为可能。传统的中断过程包括中断请求、中断响应、现场保护、中断服务程序执行、现场恢复及中断返回。对于用户中断,仅中断服务程序执行部分由CPU执行,其他部分均由FPGA硬件实现;而对于系统中断,中断过程全部由硬件实现。例如软操作系统内核的时钟节拍中断,其频率越高,加载CPU也就越频繁。若将其全部由硬件实现,与CPU并行处理,就可以提高CPU的使用效率,满足系统的实时性需要。

本文提出了一种基于PowerPC体系结构的中断管理方法,并将中断管理模块在FPGA系统上实现。

1 中断管理结构模型研究

1.1 中断管理结构模型

中断管理总体结构模型如图1所示。中断系统除负责通知系统中断以外的所有外部中断,还将发送中断使能信号到硬核并识别中断源[1]。在硬核中,中断服务程序被称为“中断任务”,与普通任务一样被硬核调度。当外部中断到来时,触发硬核的调度机制,使中断任务实时执行。而此时,硬件实时操作系统已经从处理器中的任务中使高优先级的中断任务抢占低优先级的中断任务[2]。

1.2 中断处理流程

针对中断请求和响应方式的不同特点,基于Power-PC体系结构的中断管理包括系统中断管理和用户中断管理[3]。

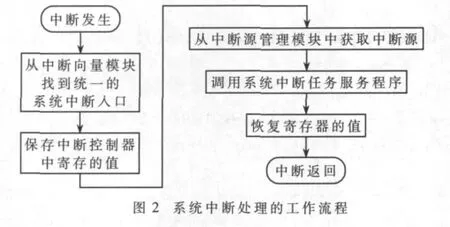

(1)系统中断:在 PowerPC体系结构中,除了把外部引脚中断和可屏蔽片内模块中断称为系统中断外,其中外部引脚中断由FPGA引脚触发:每个引脚对应一个外部引脚中断,多个外部引脚中断对应一个中断处理任务。可屏蔽片内模块中断由片内模块触发[4]。系统中断发生时,将进入统一的系统中断服务程序入口,在执行前只保存少量的必要寄存器数据即可。系统中断处理过程如图2所示。

系统中断处理过程如下:

①中断发生,硬件从中断向量模块找到统一的系统中断入口地址,中断任务从入口地址开始执行。

②保存中断控制器的值。

③同时从中断源管理模块中获取中断号以及从中断向量管理模块中获取中断向量地址。

④根据中断向量入口地址执行相应的中断任务。

⑤中断处理结束,恢复保存寄存器的数值。

⑥中断返回,从断点处继续运行。

(2)用户中断:外部引脚中断和可屏蔽片内模块中断称为用户中断[5]。如图3所示。用户中断处理过程如下:

①中断发生,硬件从中断向量寄存器找到统一的系统中断入口地址,中断任务从入口地址开始执行[6]。

②保存中断控制器中寄存器和CPU寄存器的值,把寄存器的值写入到相应的栈空间管理器。如果是从任务进入中断,则需要从任务堆栈切换到中断嵌套栈;如果是嵌套中断,则不需要进行堆栈切换。同时屏蔽比该中断优先级低的中断。

③开中断,获得中断源,然后根据该数据值,从中断向量模块中输出该类中断源的入口地址,找到中断服务程序并执行。

④中断处理结束,切换堆栈指针。首先判断中断是从何处退出,如果是从中断中退出任务,则需要从中断嵌套栈切换到任务堆栈;如果是从嵌套栈中退出任务,则不需要进行堆栈切换。

⑤恢复在第②步骤中保存的寄存器数值。

⑥退出中断,继续执行被中断的程序。

2 中断管理模块的内部结构

中断管理模块的内部结构如图4所示,由中断源管理逻辑、中断向量管理逻辑、中断嵌套逻辑和时钟节拍中断管理逻辑组成。其中,中断源管理逻辑生成中断源Id;中断向量管理逻辑提供统一的入口地址;中断嵌套逻辑判断用户中断是否存在中断嵌套,如果存在嵌套则不需要切换中断嵌套栈,否则需要切换到任务栈中执行;时钟节拍中断管理逻辑属于系统中断,该模块包含一个时钟计数器寄存器,当时钟节拍到达时,执行中断任务。

硬件中断管理同中断控制器有很大的区别,当中断控制器的中断使能有效时,只有INTA_en为1,并且外部中断到达时,才执行中断处理,此时由操作系统的硬件中断任务调度器统一调度,完成中断任务的管理。大部分的操作不需要CPU参与管理,节约了CPU的资源。

3 中断管理模块的硬件设计

3.1 中断源管理逻辑

在该中断管理逻辑中定义了五类中断源:外部设备请求中断、故障强迫中断、时钟节拍请求中断、数据通道中断以及程序自陷中断。其中,把外部设备请求中断定义为用户中断,故障强迫中断、时钟节拍请求中断、数据通道中断以及程序自陷中断定义为系统中断。系统中断直接进行任务调度,用户中断则需要中断响应、任务调度及中断现场恢复过程。一个FPGA引脚对应一类中断,一类中断就有可能有不同的中断类型,这样设计可以很好地节约硬件资源。中断控制器接收一类中断,发出中断使能,中断源管理逻辑接收中断使能信号,识别该中断源。中断源管理逻辑主要任务是识别中断源,采用图5所示的逻辑电路确定该中断属于哪类中断源。如果是同一类中断源请求中断,则生成触发信号,启动该逻辑,分配一个合适的中断源Id;否则直接分配中断源Id。

在设计前定义了五类中断源,分别为ISR0、ISR1、ISR2、ISR3、ISR4。 其中,ISR0~ISR3 为系统中断,即定义为B信号;ISR4为用户中断,即定义为A信号。中断源的类型号定义在 Idreg0~Idreg4寄存器中,定义的中断类型号如表1所示。

中断类型号的大小与中断任务的优先级有关,中断号越小,中断任务优先级越高。该逻辑的工作过程为:首先判断中断源为系统中断还是用户中断,如果输出A信号有效,则中断源为用户中断;如果输出B信号有效,则中断源为系统中断。如果是用户中断,则在中断控制器给出中断使能有效的情况下,经过一个触发器,生成一个触发信号,此时累加器接收该信号,累加器加1,Idreg4与累加器相“或”,生成一个新的 Id,输出该 Id,该用户中断在此最多支持15个外部中断;如果为系统中断,则选择器从中断类型号寄存器中选择,直接输出中断类型号Id。

表1 中断类型号寄存器表

3.2 中断向量管理逻辑

在中断向量管理逻辑中,主要任务是接收中断控制器的中断向量寄存器(IVR[x])的值,构造一个中断向量寄存器组,保存中断向量值,通过选择器,选择中断向量地址,指向特定中断服务子程序IP核的入口地址。

在逻辑内部建立一个中断向量寄存器组IVRreg,在IVRreg0~3分别存放ISR0~3的中断向量值,对应的是系统中断的中断向量。用户中断的中断向量地址,从IVRreg4开始,当有用户中断发生时,依次存入到该中断向量寄存器中。

3.3 中断嵌套逻辑

在中断嵌套逻辑中,判断中断是否存在中断嵌套,即IntNesting字段的值是否为0。如果为0,则中断管理中不存在嵌套的情况,中断直接返回,指针SP从中断嵌套栈跳转到任务栈;如果不为0,则表明在中断管理中,存在中断嵌套,中断执行完毕后,指针SP读取中断嵌套栈中的保存在中断任务中的信息,响应嵌套中断。直到IntNesting为0,指针从中断嵌套栈跳转到任务栈。

3.4 时钟节拍管理逻辑

时钟节拍管理硬件化的方案如下:

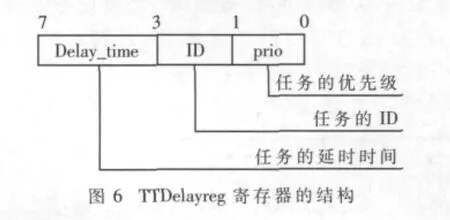

(1)接收时钟节拍中断源,保存中断任务的延时时间、任务ID及任务的优先级。把这些信息保存在输入寄存器TTDelayreg寄存器组中。TTDelayreg寄存器结构如图6所示。

(2)定时器产生时钟节拍。对每一个时钟节拍,扫描TTDelayreg寄存器,判断是否有延时时间已满。如果有,则将时钟请求节拍中断响应信号置“1”,按高优先级任务置任务就绪,执行;如果没有,则在任务的延时时间字段中,统一减去一个时钟节拍。如此重复步骤(1)、(2),直到所有任务都结束,如果寄存器中的值为空,该时钟节拍管理逻辑进行休眠态,直到有时钟节拍中断任务。

(3)时钟节拍管理逻辑接收任务的恢复延时任务信号,当接收到该信号时,时钟请求节拍中断响应信号置“1”,任务的延时取消,置任务为就绪。

4 中断管理仿真结果及分析

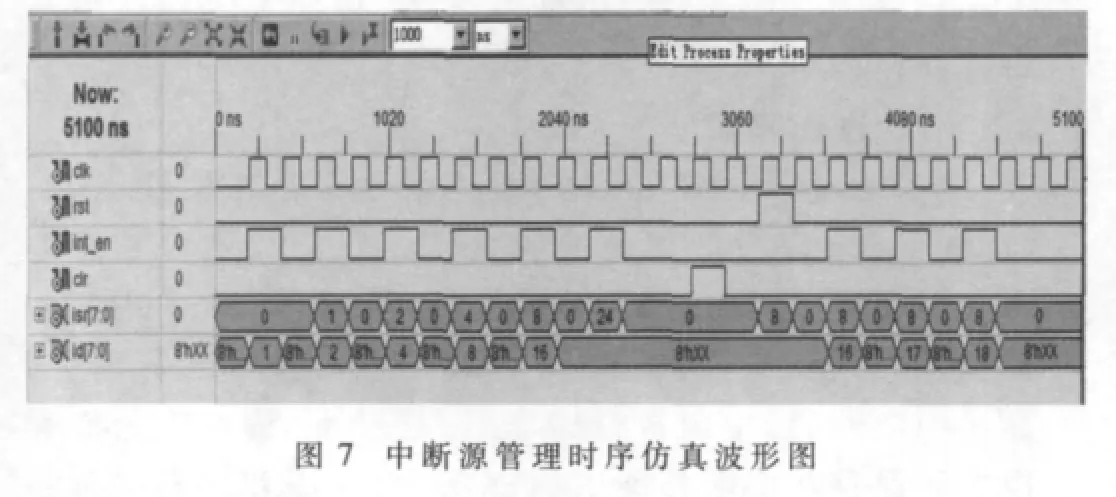

中断源管理时序仿真波形图如图7所示。由图7(仿真图采用十进制的方式)可知,在中断源管理模块中,定义了五类中断源,每类中断源对应的是ISR寄存器中的相应位,即当中断源ISR0有效时,Idreg寄存器的值置00000001;当中断源ISR1有效时,Idreg寄存器的值置00000010;当中断源ISR2有效时,Idreg寄存器的值置00000100,详细的Idreg寄存器的值如表 1所示。在中断使能有效的情况下,ISR0有效,输出 Id号为 1;ISR1有效,输出 Id号为 2;ISR2有效,输出 Id为 4,ISR3有效,输出Id为 8;ISR4比较特殊,是用户中断,是通过一个触发机制分配ID,响应了三个用户中断,输出Id分别为16~18。实验数据表明,同一的用户中断,获得的 Id不同,说明了设计的可行性和正确性。

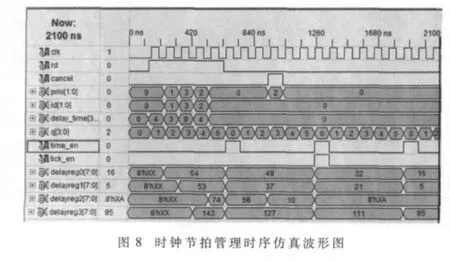

仿真模拟管理为4个任务的延时任务,初始化输出寄存器为delayreg寄存器组,接收需要延时任务的prio,任务为ID,延时时间为delay_time,接收到的数据存储在输入寄存器TTDelayreg寄存器组中,启动定时器;接着扫描cancel、time_en控制信号。时钟周期设为5个时钟,每5个时钟产生一次时钟节拍,进行一次所有延时任务的扫描。一旦扫描到规定的时间期满或某个任务调用了cancel控制信号,则取消任务延时,此时任务需要调度,置tick_en为1,进行中断任务调度,否则延时任务的时间减 1。

时钟节拍管理逻辑的仿真波形如图8所示,优先级为1的任务,开始delayreg1的值为53(即二进制为00110101),在经过一个时钟节拍后,delayreg2的值为37(即二进制为 00100101),延时任务时间减 1。

该仿真实验结果表明,CPU只有在接收到tick_en信号后,才进行延时任务处理,分配CPU资源,进行任务调度,CPU不再需要不断地扫描时钟节拍中断服务程序。从而提高了CPU的利用效率,提高了系统的执行效率。

本文提出了基于PowerPC体系结构的中断管理设计思想,通过实验数据表明了该中断管理的可行性和稳定性。中断管理的硬件化实现,不仅有效减少了CPU扫描时钟节拍中断服务程序的频率,有效提高了CPU的使用率,而且提高了系统的实时性。在硬件角上简化了设计、降低了成本,具有一定的使用价值。目前只在实验平台上对各个模块进行了仿真,下一步将中断管理进行综合,将中断管理综合的IP核应用于硬实时操作系统,以提高操作系统的运行效率。

[1]KESSAL L,ABEL N,KARABERNOI S M,et al.Reconfigurable computingdesign methodology and hardware tasks scheduling for real-time image processing[J].Real-Time Image Processing,2008(3):131-147.

[2]浦汉来,刘昊,凌明.小型嵌入式操作系统中断管理的实现[J].电子器件,2003,26(2):218-221.

[3]雷红卫,桑楠,熊光泽.嵌入式实时系统中断管理技术研究[J].单片机与嵌入式系统应用,2004(5):16-19.

[4]赵民德,姜旭峰.基于PowerPC体系结构的嵌入式操作系统的中断管理方法:中国,200510060734.X[P].2006-06-07[2010-01-02].

[5]Lin Chengmin.Nested interrupt analysis of low cost and high performance embedded systems using GSPN framework[M].Maruzen Co.,Ltd.,Nihonbashi,Tokyo,103-8691,Japan.2010:2509-2519.

[6]胡威,陈天洲,谢斌,等.一种构件化嵌入式操作系统中断的实现方法:中国,200610154795.7[P].2007-05-16[2010-01-02].