数字信号传输性能分析仪设计

2011-01-19刘三军冉文明王信杰谭大祝

刘三军,冉文明,王信杰,谭大祝

(湖北民族学院 信息工程学院,湖北 恩施 445000)

数字信号在传输的过程中会受到传输线路阻抗和噪声等因素的影响,使信号发生传播衰落、码间干扰、邻近波道干扰等现象[1].现有的数字信号传输性能分析仪中大多都应用于特定的场合,通用性方面受到很大的局限.本文提出了基于SOPC技术的数字信号传输性能分析仪,采用m序列模拟实际信道中的噪声,并能任意设定信噪比以及基带信号码率,具有通用性强,性能稳定,使用灵活的特点.设计中传输信道采用三个截止频率不同的低通滤波器进行模拟;数字信号发生器能够发出码元速率可调的m随机序列;数字信号分析电路能在尽量低的信噪比情况下自动提取出同步信号,并用提取的同步信号显示出眼图.

1 系统总体方案

1.1 m序列信号发生器及信号分析电路方案

m序列信号发生器以FPGA为开发平台,通过将50 MHz的时钟信号分频得到m序列时钟,可以方便的改变时钟频率.利用非阻塞语句实现m序列,同时通过内嵌的Nios II处理器实现按键、显示等设备的控制.整个信号产生部分以及控制部分集成在一块FPGA上.

信号分析电路采用FPGA可编程逻辑器件加高速A/D方案.FPGA可以非常方便的获取高速A/D的采样数据,并且可以通过输出任意频率的CLK方式改变采样频率,同时通过状态机迅速的寻找同步信号,这比采用软件判断更灵活.另外,FPGA可以灵活的配置数字滤波器的特征参数,并且可以使用多个数字滤波器.

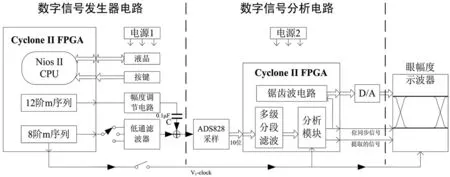

图1 系统总体原理图Fig.1 Hardware structure of the whole system

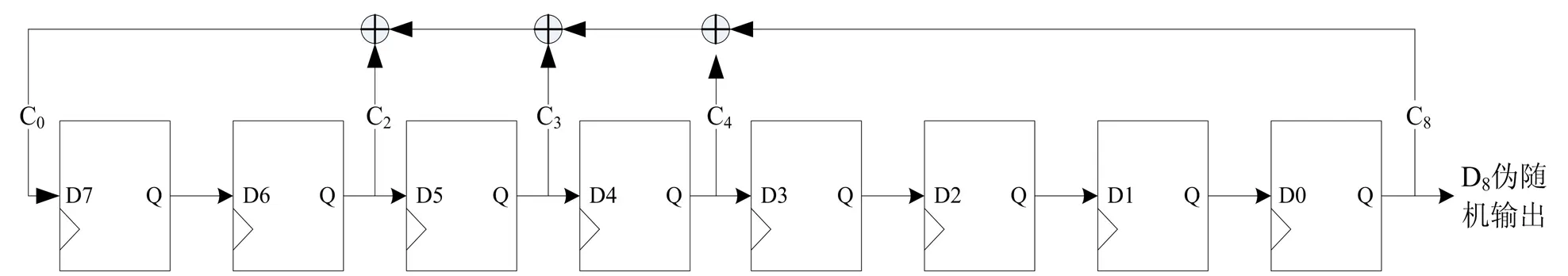

图2 多项式1+x2+x3+x4+x8的m序列原理图Fig.2 The m-sequence principle diagram of polynomial 1+x2+x3+x4+x8

编号中心频率/K宽度/K阶数110108022011853301292440131025501411468016127710018143

1.2 系统总体设计

系统整体采用两块Altera Cyclone II FPGA为开发平台,分别实现数字信号发生器和数字信号分析电路.第一个FPGA包含有8级、12级m序列发生器模块,并且内嵌Nios II软核CPU,用来实现按键控制和LCD显示;第二块FPGA通过调用FIR的兆功能核实现带通滤波,便于分析电路模块提取有用信息以及位同步信号.系统整体框图如图1所示.

2 伪随机信号发生器设计方案

2.1 m序列和曼彻斯特编码生成原理

m序列是最长线性反馈移存器序列的简称,它是由带线性反馈的移存器产生的周期最长的一种序列[2].多项式1+x2+x3+x4+x8是一个既约多项式,由它产生的m序列的周期为255.该多项式对应的线性反馈移位寄存器原理图如图2所示.

曼彻斯特编码,是将不归零的普通二进制数据与其位率时钟信号相异或而得,解决了传输数据没有时钟的问题[2].根据定义,首先将信号时钟二分频,得到位率时钟,再将该位率时钟与基带信号相异或便可得到曼彻斯特编码.

2.2 Nios II CPU模块配置

采用Altera的SOPC Builder工具构建出Nios II软核CPU系统,每一个外设都对应着一个特定的IP核,系统添加的IP核有[3-4]:Nios II CPU核,JTAG核用于在线调试,三态桥总线用于总线共享,SRAM、SDRAM及Flash用来存储,PIO用于按键控制,LCD控制器核用于控制液晶(该IP核为自主开发).

2.3 电平转换及加法电路电路设计

由于FPGA输出的高电平只有3.3 V,需要转换成标准的TTL电平以便于模拟一般信号在信道中的传输.设计中采用CD40106施密特触发器实现,具有电路简单、输出波形失真度小的优点.采用同相加法电路实现噪声信号和基带信号的求和,运放选用THS3061,具有通带频率宽、供电电压范围宽的特点.

3 数字信号分析电路设计方案

分析电路的设计思路是将待测信号根据码率分为低频和高频部分(设定10 KHz以上为高频,1 KHz以下为低频),低频采用比较的方法提取出位同步信号,高频部分采用窄带滤波器+锁相的方法提取位同步信号.设计中根据位同步信号产生了同频的锯齿波,用来在示波器上显示眼图.

3.1 A/D采样电路设计

系统选用ADS828E作为A/D转换芯片,理想情况下最高转化速率可以达到75M,实测结果表明最高稳定的转换速率只能达到10 MHz,故系统设定的采样速率为10 MHz,采样电路设计参照ADS828E PDF文档.

3.2 多级、分段数字滤波器设计

基频信号经曼彻斯特编码之后含有与码率同频的正弦谐波,通过窄带滤波器可以提取出来[5].但是信号发送端的码率是变化的,为了较为精准的提取较高码率信号的正弦基频,系统设计了7个不同中心频率的窄带滤波器,他们的设计参数如表1所示.

3.3 锯齿波电路设计

系统中设计了与V4-syn同步的锯齿波电路以便于能在模拟示波器上以x-y的方式显示眼图,设计中DA选用DAC902E,具体电路设计参照DAC902E PDF文档.

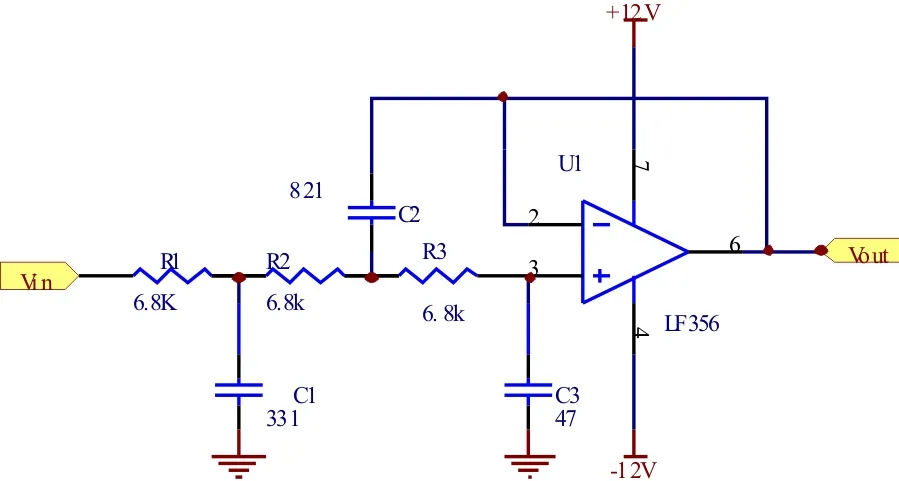

图3 滤波器电路图Fig.3 Schematic of low pass filter circuit

图4 系统软件流程图Fig.4 Software flow chart or system

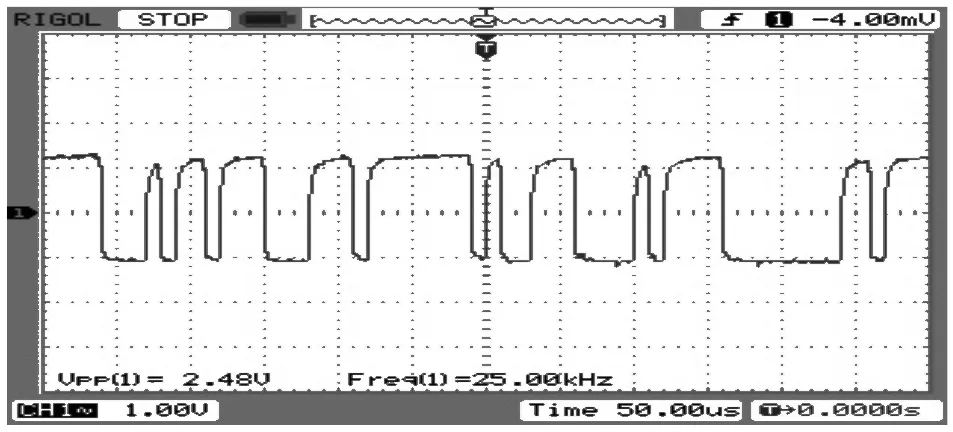

图5 m序列实际输出波形Fig.5 The real output wave of m-sequence

4 低通滤波器及噪声调幅电路设计

4.1 低通滤波器设计方案

题目要求设计三路不同截止频率的低通滤波器用来模拟不同的传输信道,要求每个滤波器带外衰减不少于40dB/十倍频程.设计中选用带内平坦度优良的两个巴特沃斯三阶低通滤波器级联得六阶低通滤波器,带外衰减理论上达120dB/十倍频程,电路设计如图3所示.计算出滤波器的传递函数[6]为式(1).

(1)

4.2 噪声调幅电路设计方案

从FPGA输出的噪声电压VPP是3.3 V,题目要求噪声电压能从100 mV~TTL电平幅度调.为解决这个问题,首先将噪声信号放大到5 V,再通过TLC7528程控衰 减调节,由于LC7528的转换频率可达到25 MHz,可以使10 M的噪声电压不失真的程控衰减.

5 软件设计

系统采用嵌入式软核CPU Nios II来承担按键、显示及系统控制的任务,开发环境为Altera公司提供的集成开发环境IDE(Integrated Development Environment)[8].软件流程图如图4所示.

6 系统测试方案及结果分析

6.1 m序列验证及曼彻斯特编码测试

可以通过具有存储功能的示波器进行存储回放的方式来验证m序列的正确性.由m序列递推公式可知,新生成的码元,应该是前8个已生成码元的函数.如果每个新生成的码元与前面8个码元之间都有这样的关系,表明该m序列是正确的,实际序列输出如图5.在图5中从左至右取序列001011001,根据推论可得0^1^1^0=1,等于最后一位,证明m序列正确.

数据率测试参数如表2所示,频率输出误差达到0.004%,远远超出题目要求指标.

表2 数据率参数测试表

6.2 低通滤波器参数测试及结果分析

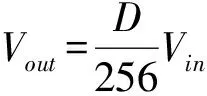

设计中采用三个低通滤波器,用来模拟不同信道的通频带传输特性.三个滤波器的主要区别是截止频率的不同,分别是:100、200、500 kHz.共同特性是每个滤波器带外衰减不小于40 dB/十倍频程,通带增益要求在0.2~4.0范围内可调.通过扫频仪测得三路滤波器参数断滤波器性能,测量结果表明-3dB截止频率误差小于5%.三路滤波器参数如表3所示.

表3 模拟低通滤波器性能测试表

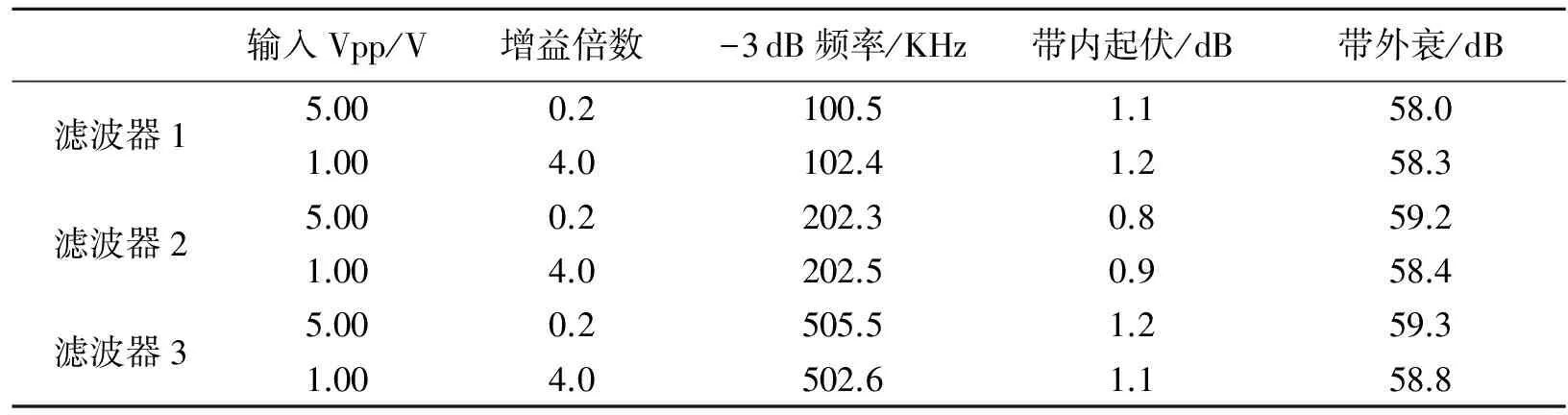

6.3 眼图测试结果

在测试,将数字信号分析电路输出信号加载到数字示波器X端、将提取的同步信号加载到数字示波器的外触发端形成“眼图”,如表4所示.

表4 眼图测试表

通过对比可以看出,在高信噪比的情况下眼图质量明显好于低信噪比的眼图质量,这就表明本文所设计的系统能够准确的测出数字线路的传输性能.

[1] 肖闽进.基于FPGA的数字通信误码测试系统设计[J].常州工学院学报,2006,19(5):32-34.

[2] 樊昌信,张浦翊,徐炳祥.通信原理[M].北京:国防工业出版社,2001.

[3] Altera.Corporation.www.altera.com[EB/OL].NiosⅡ Software Deuelopment Manaal,2011-09-01.

[4] Altera.Corporation.www.altera.com[EB/OL].Sopc Build PTF File Reference Manual,2011-09-03.

[5] 张仁杰.广义多载波滤波器组的算法研究和FPGA实现[D].南京:东南大学,2006.

[6] 刘树棠.基于运算放大器和模拟集成电路的电路设计[M].西安:西安交通大学出社,2010.

[7] 高吉祥.电子仪器仪表设计[M].北京:电子工业出版社,2007

[8] Altera Corporation.www.altera.com[EB/OL].Nios II Hardware Development Tutorial,Version 9.1 June,2010-06-10.