一种带自刷新功能的三模冗余触发器设计

2017-07-20曹靓王文封晴

曹靓,王文,封晴

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

一种带自刷新功能的三模冗余触发器设计

曹靓,王文,封晴

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

随着体硅CMOS电路工艺尺寸的不断缩小,数字电路在宇宙空间中受到的单粒子效应愈发严重。特别是触发器结构电路,单粒子效应中的单粒子翻转效应会造成触发器内部存储的数据发生错乱,影响电路正常工作。提出了一种带自刷新功能的三模冗余触发器设计,改进了传统三模冗余触发器设计只表决修正输出不刷新错误数据的不足。

单粒子翻转;抗辐射加固;触发器;三模冗余

1 引言

随着工艺技术的发展,器件尺寸缩小,集成电路集成的晶体管密度提高,随着工作频率的不断增加以及工作电压的降低,数字电路中的单粒子效应影响越来越严重[1~3]。当宇宙射线或其他带电粒子射入器件的耗尽区,会引起耗尽区电离,从而产生电离通道。若粒子能量足够高,电离通道可进入衬底,形成形状像漏斗的电离等离子区。电离等离子区里等离子体密度可较衬底掺杂高出几个数量级,这样的等离子体周围的耗尽区被中和,耗尽层消失。电离通道的电荷在电场的作用下,空穴被驱赶到衬底,电子被吸引到正电极。如果该电荷量可与存储的信息电荷量比拟,就可能改变单元的状态,也就产生了软错误,这种错误称之为单粒子翻转(Single-Event Upset)。

目前对单粒子翻转效应的加固方法主要是设计加固,针对带有存储结构的单元如触发器等,较为常见的加固设计方法为三模冗余[5],采用三个相同模块同时执行相同的操作,三路信号通过表决,以少数服从多数的原则作为输出,只要不出现两个模块同时发生SEU,就可以屏蔽掉错误,保证最终输出的正确性。

传统的三模冗余设计虽然通过表决屏蔽了错误输出,但是发生错误的模块中的错误数据在下个时钟周期到来前依然存在。在特殊的应用环境下,如时钟周期较长或者非连续时钟时,可能发生第二个模块错误从而影响输出。本文介绍了一种带自刷新功能的三模冗余触发器设计,可以在表决的同时纠正错误的数据,从而保证在各种应用环境下系统功能的准确性。

2 电路设计

2.1 传统结构三模冗余设计

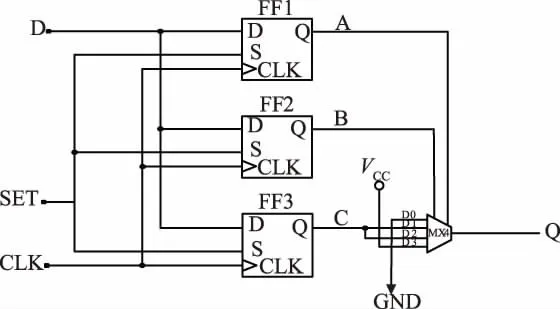

图1所示为一种典型的传统型三模冗余触发器,三个触发器并行排布,拥有相同的输入和时钟端口,三个触发器的输出信号通过一个MUX形式的表决器结构进行输出,两个触发器的输出A和B连接到表决器MUX的选择端。

图1 三模冗余结构逻辑框图

如果A和B都为逻辑“0”,那么MUX的D0端将被选择作为输出,D0端接地,因此最终输出为逻辑“0”;同理,如果A和B都为逻辑“1”,那么D3端被选择作为输出,D3端接电源,因此最终输出为逻辑“1”。如果A和B的信号因为发生了SEU而导致不同(01或者10),那么将选择第三路触发器输出C作为最终输出,由于C要么与A相同,要么与B相同,因此最终输出为A、B、C三路中两路相同的信号,即通过“表决”以少数服从多数的方式决定了输出。

2.2 带自刷新功能的三模冗余设计

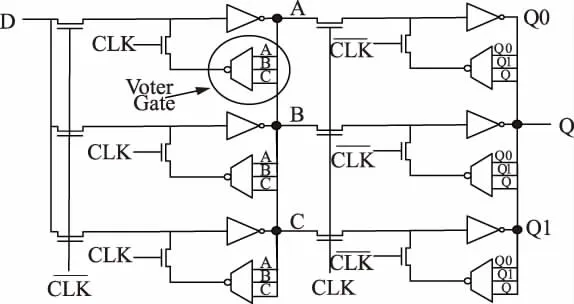

图1设计的三模冗余触发器可以通过表决有效屏蔽SEU的错误输出,但是在下个时钟周期到来之前,错误信息依然储存在触发器中,不会被纠正。在一些特殊的应用环境中,如果时钟周期很长或者在非连续时钟应用环境下,在长时间的等待过程中,可能出现除已发生SEU的触发器外,另一个触发器也发生SEU的情况,这时候两路错误信号会通过表决从而造成错误输出。要避免以上情况的发生,最好的方法就是改进增加自刷新功能,在表决的同时将错误信息纠正,图2所示为一种自刷新三模冗余触发器设计。

设计原理是在三路并行触发器每一个带反馈的存储结构里,将反馈路径上的反向器改为表决逻辑门。图2中三路触发器包含六个带反馈存储结构,对其中每个反馈路径的反向器均进行改造。前级(A、B、 C点)和后级(Q、Q0、Q1点)分别进行表决。举例说明,假如A点信号因为SEU发生错误,那么在圆圈处的表决逻辑门会通过B、C的正确信号将A信号纠正,并且这个纠正过程是即时的,不需要等待时钟或其他信号驱动。由于后级也采用了表决逻辑门设计,即使A点错误信号在纠正前被传输至Q0,那么在后级表决逻辑门也会被纠正,保证最终输出的稳定。

图2 带自刷新功能的三模冗余设计

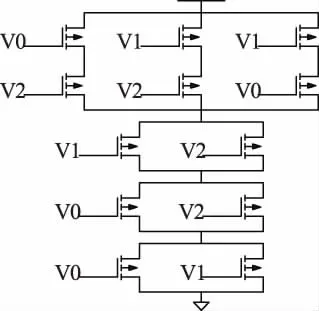

表决逻辑门的逻辑图如图3所示,逻辑表达式为Y=V0&V1+V0&V2+V1&V2。

图3 表决逻辑门逻辑图

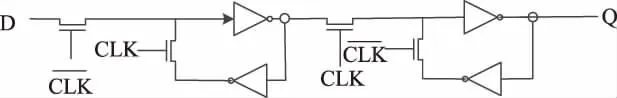

该三模冗余结构与传统三模冗余结构相比会增大版图面积,增大部分主要是由于传统反馈路径上的反向器变为表决逻辑门造成的。传统三模冗余结构的每一级触发器包含最少12个MOS管,如图4所示。反馈路径上的反向器改为表决逻辑门后,原本2个MOS管组成的反向器变成了12个MOS管的表决逻辑门,额外增加了10个MOS管。由于1级触发器包含2个反馈回路,因此,新结构的每一级触发器都将增加20个MOS管,即每一级触发器都由12个MOS管增加到32个MOS管。整个新结构将增加约60个MOS管,通过版图合理布局,新结构最终面积约为传统三模冗余结构的两倍。

图4 传统三模冗余触发器结构图

3 仿真分析

选用0.18 μm仿真模型,采用Hspice工具进行仿真分析,仿真偏置条件为:电源电压2.25~2.75 V,温度范围-55~125℃。仿真结果如图5所示。

图5自刷新三模冗余触发器仿真图

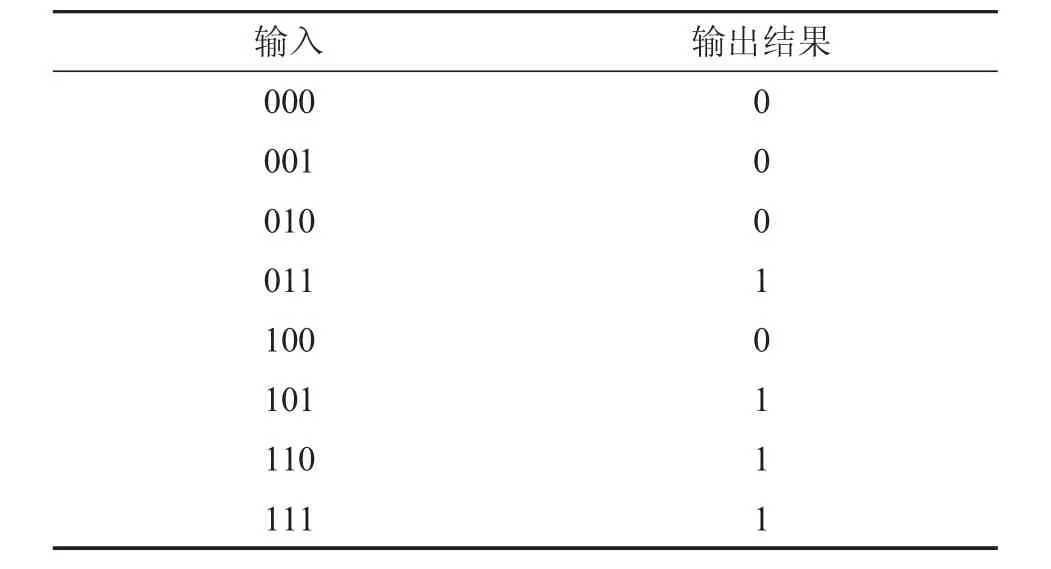

图5 中din0~din2为三个触发器的激励信号,q为最终输出,clk1为驱动时钟。整理仿真结果见表1。

表1 自刷新三模冗余触发器功能仿真结果

4 试验验证

在中国电科第58所研制的抗辐射FPGA电路中应用本文提出的带自刷新功能的三模冗余设计对触发器进行了加固,通过中国原子能科学研究院核物理研究所的HI-13串列加速器将FPGA配置为EDAC(Error Detection And Correction)功能,进行试验验证。试验采用Ge粒子,试验过程中功能未发生翻转错误。经验证加固后的电路抗单粒子翻转LET阈值达到37 MeV·cm2/mg以上,达到加固要求。

5 总结

本文提出了一种带自刷新功能的三模冗余触发器设计,主要思想是通过在每级触发器每一个带反馈的存储结构里,将反馈路径上的反向器改为表决逻辑门,当错误发生时通过表决将错误信息即时纠正。该方法为抗辐射集成电路设计提供了新的加固设计思路。

[1]S P Buchner,M P Baze.Single-event Transients in Fast Electronic Circuits[C].IEEE NSREC Short Course,2001:1-105.

[2]H T Nguyen,Y Yagil.A Systematic Approach to SER Estimation and Solutions[C].Proc.Int.Reliability Physics Symp,2003:60-70.

[3]D G Mavis,P H Eaton.Soft Error Rate Mitigation Techniques for Modern Microcircuits[C].Proc.Int.Reliability Physics Symp,2002,4:216-225.

[4]Quming Zhou,Kartik Mohanram.Gate Sizing to Radiation Harden Combinational Logic[C].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2006,25(1):155-166.

[5]Ronald C Lacoe.Improving Integrated Circuit Performance Through the Application of Hardness-by-Design Methodology[J].IEEE Trans.Nucl.Sci,2008,55(4):1903-1925.

Design of Triple Modular Redundancy Flip-Flop with Self-Refresh Function

CAO Liang,WANG Wen,FENG Qing

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

Digital logic technology scaling results in greater sensitivity to the radiation effect when used in space.Especially in date flip-flop,Single-Event Upset may make the data in flip-flop change and cause complete failure of circuit function.The paper introduces a design of TMR(Triple Modular Redundancy) flip-flop with self-refresh function,which improves the traditional design of TMR flip-flop that only corrects the outputthrough vote gate withoutrefreshing the error bits.

Single-EventUpset;radiation hardness;flip-flop;Triple Modular Redundancy

TN303

A

1681-1070(2017)07-0025-03

曹靓(1984—),男,江苏无锡人,毕业于东南大学,工程师,现就职于中国电子科技集团第五十八研究所,主要从事抗辐照FPGA等电路设计工作。

2017-4-14