基于FPGA的时钟信号实现方法

2017-07-20季振凯郭俊杰

季振凯,郭俊杰

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

基于FPGA的时钟信号实现方法

季振凯,郭俊杰

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

时钟信号是时序电路的基础和整个电路得以正常运行的保证,由于仪器的小型化和低成本化对印刷电路板(Printed Circuit Board,PCB)具有严格的物理尺寸、层数等要求,使得通过震荡器和时钟分配IC获得多种频率时钟信号的PCB电路设计方法越来越难以持续。为此,设计三种基于FPGA的时钟信号实现方法,可以在FPGA引脚充足的情况下取代震荡器和时钟分配IC,为PCB电路提供多种频率的时钟信号。

时钟信号;时序电路;FPGA;震荡器

1 引言

时钟信号是指有固定周期并与运行无关的信号量,它用于决定逻辑单元中的状态何时更新。时钟信号是时序逻辑的基础,是时序控制系统得以正常运行的保障。而时序控制系统的首要制约条件便是同步,同步是指在有效信号沿发生时刻,能够写入单元的数据也有效。

同步数字系统中的时钟信号(如远程通信中使用的)为系统中的数据传送定义了时间基准。一个时钟分配网络由多个时钟信号组成,由一个点将所有信号分配给需要时钟信号的所有组件。因为时钟信号执行关键的系统功能,很显然应给予更多的关注,不仅在时钟的特性(即偏移、抖动和占空比)方面,还有那些产生时钟信号的组件。

2 时钟信号的特性

对于时序电路尤其是具有全局时钟的高速电路,除考虑时钟与数据是否满足建立时间和保持时间外,还需考虑时钟偏移、时钟抖动和时钟占空比,以下将介绍这三种时钟信号的特性。

2.1 时钟偏移

时钟偏移是指同一个时钟信号到达两个不同寄存器之间的时间差,根据差值的正负可以分为正偏移和负偏移。产生时钟信号偏移的主要原因是:时钟信号要提供整个电路的时序单元,从而导致时钟线非常长,并构成分布式RC网络。它的延时与时钟线的长度及被时钟线驱动的时序单元的负载电容大小和个数有关,由于时钟线长度及负载不同,从而导致时钟信号到达相邻两个时序单元的时间不同,便产生了所谓的时钟偏移。

时钟偏移无法避免且永远存在,但当其大到一定程度时,就会严重影响电路的时序。因此在STA(static time analysis)中,时钟信号偏斜是必须考虑的因素。同时通过布局布线前和布局布线后两个阶段的STA,估计时钟树上的偏移,继而通过修改设计等方法,保证时钟偏移满足时序电路的要求。

2.2 时钟抖动

时钟抖动是指时钟信号沿不稳定,会提前或者延时。时钟抖动最常见的两个参数是周期抖动和周期间抖动。周期抖动较大也比较固定,常由第三方原因造成,如干扰、电源、噪声等。周期间抖动由环境因素造成,具有不确定性,满足高斯分布,一般难以跟踪。

同时钟偏移一样,时钟抖动是永远存在的,但当其大到可以和时钟周期相比拟时,就会影响到设计时序,这样的时钟抖动是不可接受的。

2.3 时钟占空比

理想情况下,时钟占空比是50%,也即时钟信号的高电平保持时间等于低电平保持时间,时钟信号在传输过程中由于变形、时延等原因的存在使得脉冲宽度发生变化,该变化使得时钟信号高低电平的时间比例发生改变,也即时钟占空比失真(Duty Cycle Distortion,DCD)。

对于单边沿触发的时序电路,时钟占空比对于时序电路并不会有太大的影响,但是对于现有的其他高速电路,如片外高速存储器,它采用双数据甚至多数据接口,在时钟的上升沿和下降沿都需要对数据进行采样,每次读或写至少有两拍时钟,在此类应用时,DCD会吞噬大量的时序裕量,进而造成数字信号的失真,使过零区间偏离理想位置,向上或者向下移动。

因此,保证时钟信号占空比对于充分利用系统资源、保证时序电路的时序裕量具有重要意义。

3 基于FPGA的时钟信号实现方法

印刷电路板设计必须考虑到许多限制因素,包括物理尺寸、散热要求、走线长度、层数和互连的类型。随着每一代的设计都要求更多的功能,因而电路板的限制因素也越来越多。

采用添加时钟信号IC的传统设计方法不仅因为时钟网络的各种走线长度,占用了大量的电路板面积,并且还用到大量的振荡器和时钟分配IC来产生设计中所需的多种频率[1],不但制约了PCB电路板的小型化还提高了设计成本[2]。本文提出的解决方案是使用可编程逻辑器件(如FPGA和CPLD)产生时钟信号,减少元件数量,降低成本并降低电路板的复杂度。采取这种方法的同时还可以进一步重新审视时钟分配网络。

3.1 调用内部时钟信号发生器

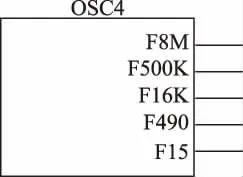

该方法最为简单,但需要FPGA内部集成时钟信号发生器模块,其原理图如图1所示。

图1 时钟信号发生器模块原理图

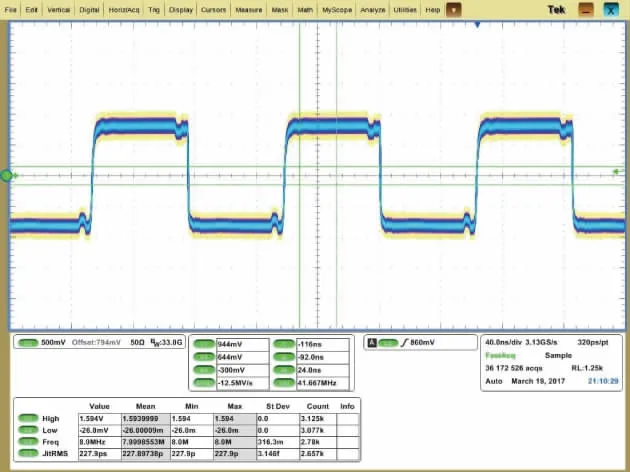

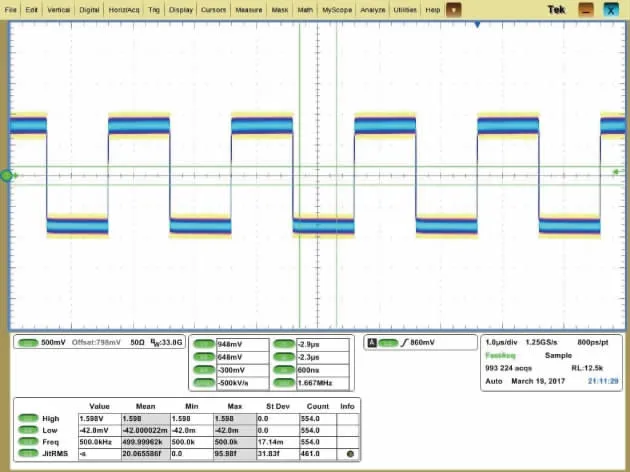

F8M、F500k、F16k、F490、F15分别对应8 MHz、500 kHz、16 kHz、490 Hz和15 Hz的时钟信号输出。将各模块端口与FPGA的IO口连接,便可以在该IO口获得该频率的时钟信号。图2、图3分别是通过示波器获得的F8M和F500K端口的时钟信号。

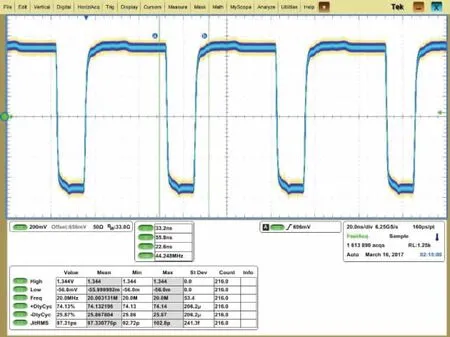

图2 通过示波器获得的F8M端口的时钟信号

图3 通过示波器获得的F500k端口的时钟信号

采用这种方式获得的时钟信号频率、占空比受限,但具有较低的抖动和良好的稳定性。

3.2 锁相环配置时钟

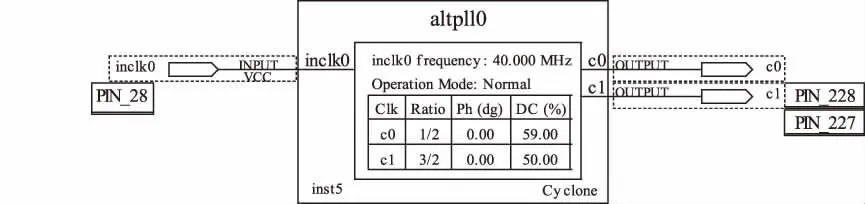

通过FPGA的外接晶振作为锁相环的时钟信号输入,并利用锁相环的分频和倍频功能,产生需要的特定频率的时钟信号[2]。其设计原理图如图4所示。

图4 锁相环配置时钟信号设计原理图

由图4可知,锁相环输入时钟也即晶振的频率为40 MHz,通过调节Ratio的值来调节输出时钟信号的频率。设输入时钟信号频率为fin,输出信号频率为fc,Ratio的值为R,则输出频率的计算公式为fc=R·fin,其中R值的分子和分母皆为在一定范围内可调的正整数,且对于不同的FPGA芯片,该值的范围存在一定差异。默认情况下被配置的时钟信号占空比和相位延时分别为50%和0。通过调节锁相环中的DC和ph调节输出时钟信号的占空比和相位延时[2~3]。

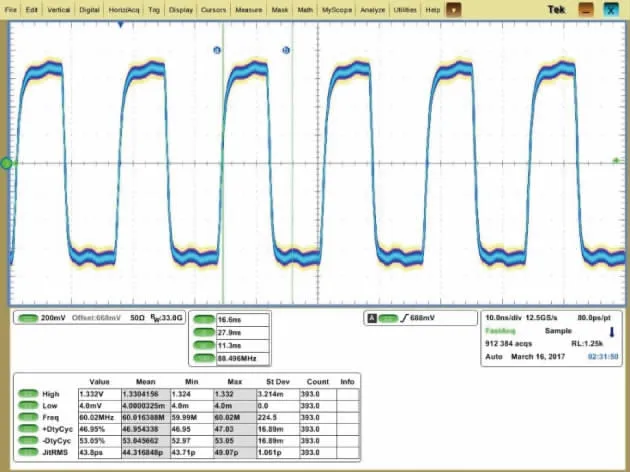

按照上述方法,配置两路时钟信号c0和c1。c0的频率为20 MHz,相位延时为0,占空比为75%;c1的频率为60 MHz,相位延时为0,占空比为50%。将以上设计载入FPGA,通过示波器获得的两路频率信号波形如图5、图6所示。

图5 c0信号波形

图6 c1信号波形

采用锁相环获得的时钟信号具有输出稳定、抖动低、频率相位精确可调的优点,但是必须外接晶体振荡器来获得初始时钟信号,并且初始时钟必须满足一定频率、抖动要求。

3.3 级联反相器

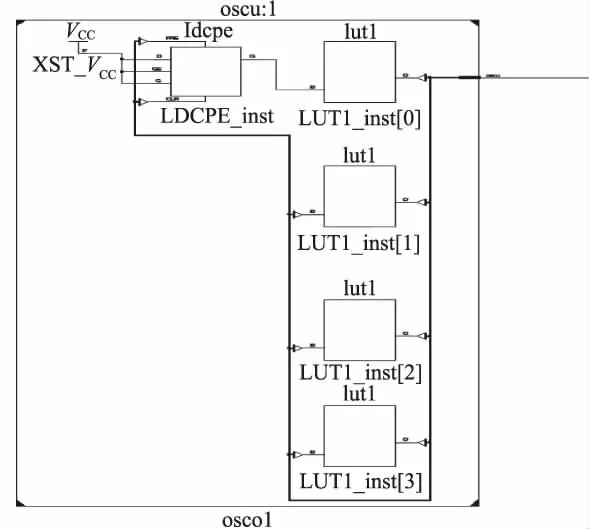

由于需要级联若干反相器以实现不同频率的时钟信号输出,所以该方法适用于FPGA资源富余的情况,其具体设计方法如图7所示。

图7 级联4个反相器设计原理图

本方法需使用的主要元件是反相器和锁存器,通过反相器级联并控制锁存器的复位端和置位端以实现1和0状态的翻转。该方法相对较为复杂,旨在无法获得锁相环和时钟信号发生器时临时搭建时钟系统,是上述两种方法的补充。

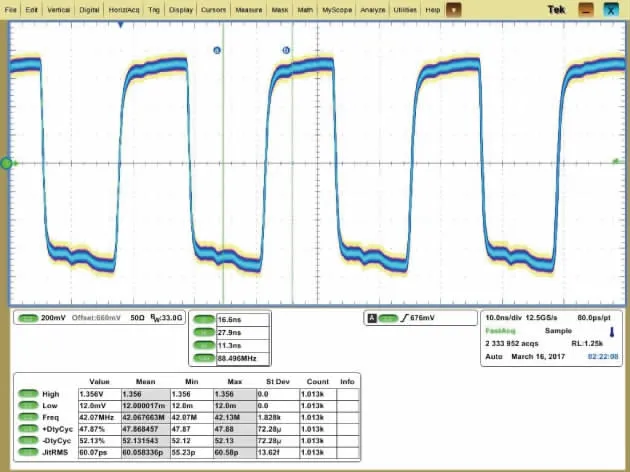

图8 级联20个反相器获得的时钟信号

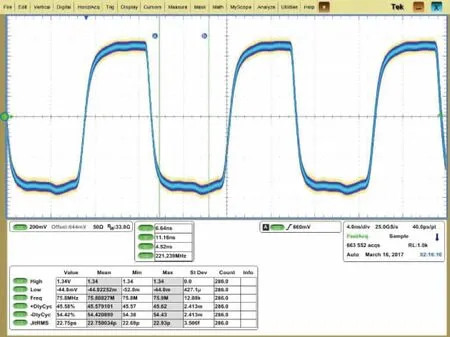

图9 级联40个反相器获得的时钟信号

通过添加不同数量的反相器获得不同的信号延时,便可获得不同频率的时钟信号。图8为串联20个反相器时获得的时钟信号波形,时钟频率为42.07 MHz,占空比为50%。图9为串联40个反相器时获得的时钟信号波形,时钟频率为75.8 MHz。

采用这种方法可在无外接晶振的情况下产生稳定时钟,有效降低PCB板上面积和复杂度。但是由于各反相器之间延时的关系,很难精确产生特定频率的时钟信号。同样的原因,在程序经过重新综合、布线后时钟信号的频率还会发生一定改变。为避免这一现象,必须在约束文件中对每个反相器位置进行约束。3.4三种时钟信号获取方法比较

(1)通过FPGA内置时钟模块的方法简单稳定,不增加PCB板上面积,但是生成的频率、相位、占空比受限;

(2)通过锁相环生成时钟信号的方法可以灵活地产生不同频率、相位、占空比的时钟信号,且信号抖动小、误差低,但是需要板上外接时钟输入;

(3)通过反相器串联的方法可在无时钟振荡器的情况下生成稳定可用的时钟,但很难精确生成指定频率的时钟。

4 结束语

本文介绍了三种基于FPGA电路的时钟信号实现方法,实现了取代震荡器和时钟分配IC,为PCB电路提供多种频率的时钟信号,可满足不同情况下电路对时钟信号的需求,减小了PCB面积、减少元件数量、降低成本并降低电路板的复杂度。

[1]刘一平,叶媲舟,凌朝东.FPGA的可靠时钟设计方案[J].华侨大学学报(自然版),2009,30(6):720-722.

[2]James Wilson.为基于FPGA的设计选择绝佳的内部或者外部时钟解决方案[J].今日电子,2014(9):32-33.

[3]沈增帧.一种基于FPGA的高精度时钟信号源[J].电子技术与软件工程,2016(10):105-107.

[4]陈欣波.Altera FPGA工程师成长手册[M].北京:清华大学出版社,2012.

[5]张建斌.锁相与频率合成[M].北京:科学出版社,2011.

[6]张厥盛.锁相环频率合成器[M].北京:电子工业出版社, 1997.

Implementation Method of FPGA-Based Clock Signal

JI Zhenkai,GUO Junjie

(China Key System&Integrated Circuit Co.,LTD,Wuxi 214072,China)

Clock signal is the basis of timing circuit and the safeguard of circuit operation.The miniaturization and cost-effectiveness of the printed circuit board(PCB)entails strict requirements on physical size and layers, thereby crippling the method of obtaining various-frequency clock signal using oscillator and clock distribution ICs.The paper presents three FPGA-based clock signal implementation methods capable of replacing the traditionalmethod when FPGApinsare adequate.

clock signal;sequentialcircuit;FPGA;oscillator

TN402

A

1681-1070(2017)07-0017-04

季振凯(1986—),男,2009年毕业于南京大学电子科学与工程系,学士学位,2009年6月起就职于中国电子科技集团公司第五十八研究所,从事超大规模集成电路测试应用及可靠性验证的研究工作。

2017-3-21