基于双DSP和FPGA控制器的大功率电压暂降仪设计

2015-06-25张华赢朱正国姚森敬史帅彬黄力鹏欧阳森

张华赢,李 翔,朱正国,姚森敬,史帅彬,黄力鹏,欧阳森,曾 江

(1.深圳供电局有限公司,广东 深圳518020;2.华南理工大学 电力学院,广东 广州510640)

1 引言

随着科技和经济发展,以计算机、可编程控制器、嵌入式系统为核心的精密设备等敏感负荷大量接入电网,这些设备对电压质量的要求非常高,主要由系统故障引起的电压暂降,往往会导致敏感设备异常工作甚至死机,因而造成巨大的损失[1-2]。因此,电压暂降造成对用电设备特别是敏感设备造成的影响已成为电能质量领域研究的热点课题[3-5]。在研究电压暂降对用电设备产生的影响时,有时需要测试用电设备在电压暂降条件下的工作情况。然而,在实际过程中,要电网产生特定持续时间与波形的电压代价很大且很难达到。因此,研制可产生特定电压波形的装置就显得尤为重要。

目前,电压暂降发生仪(电压暂降仪)、电能质量信号发生器、电能质量干扰发生器等装置均可产生所需的电压波形,为测试用电设备的实验提供条件[6-12]。文献[6-7]研制的电压暂降发生仪虽然采用数字信号处理器(DSP)控制电子器件的开断,但由于其原理的限制,控制存在不够精确、不够灵活等不足。文献采用单片机作为控制器,同样由于原理限制,缺乏精确性和灵活性。文献[9-12]基于逆变器结构,采用DSP控制,具有快速、精确、灵活等优点,但受限于DSP性能,单DSP控制器如要同时兼顾运算、输出、故障检测、人机交互等功能要求,必然导致控制周期延长和控制精度降低。

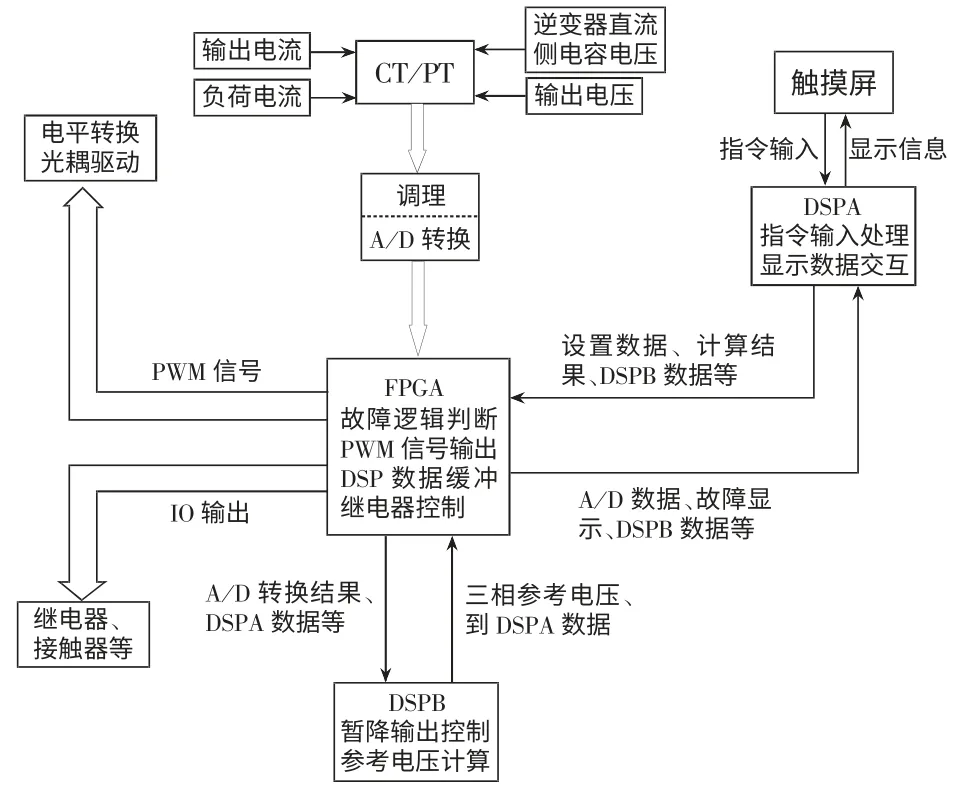

因此,为了进一步提升电压暂降仪的性能,实现多功能、智能化控制等设计要求,本文设计了基于双数字信号处理器(DSP)和现场可编程逻辑门阵列(FPGA)架构控制器的电压暂降仪,其控制器采用“双DSP(F2812)+FPGA”架构,一个DSP(称为DSPA)负责处理数据显示与数据输入,一个DSP(称为DSPB)负责产生参考波形并对输出波形进行控制,现场可编程逻辑门阵列(FPGA)负责控制模数(A/D)转换芯片工作、逆变器IGBT驱动信号的生成与全系统的故障检测,一旦有故障可瞬时执行保护程序,不受DSP工作状态影响。三者分工明确,使全系统的运行效率明显提高。

2 主电路拓扑设计

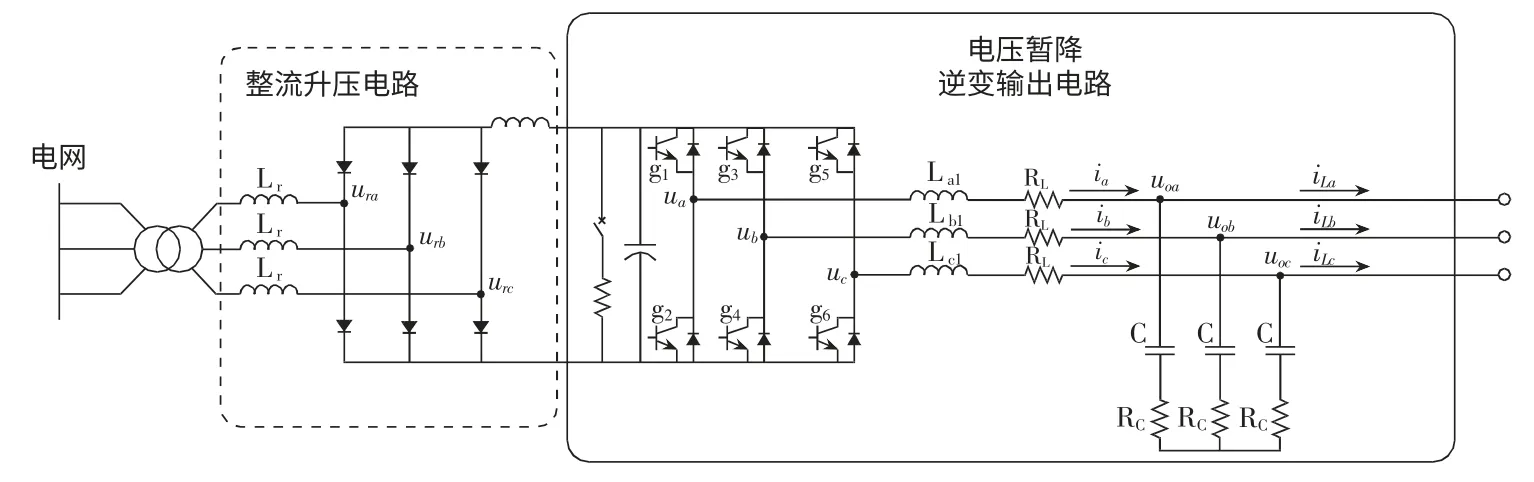

电压暂降发生仪的主电路由整流升压电路和电压暂降逆变输出电路两部分采用“背靠背”的方式连接组成。前端为整流升压电路,采用三相不可控整流电路进行整流升压。电网通过一个升压变压器接于三相不控整流桥的交流侧,直流侧经一平波电抗接于电容器两端。后端为电压暂降逆变输出电路,控制系统输出的脉冲经驱动电路控制功率开关IGBT的通断,经LC滤波器向负载提供指定电压和电流。

实验电路拓扑如图1所示,本文采用LC滤波器作为输出滤波器,其中La1、Lb1、Lc1均取190μH,RL为输出滤波器电感的等效电阻,C 取60μF,Rc取0.11Ω,Rc用于停机时消耗直流侧电容能量市电经调压器升压后,通过三相整流桥给逆变器直流侧电容充电,充电完成后由控制器控制逆变器输出电压,输出端接电阻负载。

图1 电压暂降仪拓扑结构图

3 双DSP和FPGA控制器设计

3.1 控制器硬件系统设计

本文设计的电压暂降发生仪的控制器采用“双DSP+FPGA”架构。其中,DSP是TI公司的TMS320F2812芯片,这是一款针对数字控制所设计的32位定点型DSP,具有强大的数据运算能力,主频最高达150MHz,广泛应用于嵌入式控制领域。FPGA是XILINX公司的XC2S200芯片,是一种可编程使用的信号处理器件,用户可通过改变配置信息对其功能进行定义,以满足设计需求,其内部有丰富的BRAM、GCLK、各种直接可利用的IP核等资源,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,有效提高了设计的灵活性和效率。

为了提高电压暂降仪控制器的运作效率及实时反应速度,应充分发挥FPGA逻辑判断的优势,应用其进行多种故障逻辑判断和IO输出。同时,应充分发挥DSP强大的数据运算能力,应用其进行精确的输出控制。因此,对FPGA和两块DSP应作功能分配,图2为电压暂降仪控制器架构框图。

FPGA主要有四方面功能:一是控制A/D转换芯片,对外部CT/PT及调理电路后的电压电流信号进行模数转换并读取结果,同时把结果传送给DSPA和DSPB;二是作为DSPA和DSPB之间的数据交换通道;三是逆变器IGBT驱动信号输出;四是进行全系统故障检测及IO控制输出。

DSPA主要负责与人机界面通讯及数据管理。DSPA读取FPGA中的电压电流数据和故障状态等信息在人机界面中显示,并传送人机界面中的命令。

DSPB主要负责控制电压波形的稳定精确输出。DSPB通过FPGA与DSPA进行数据交互,读取触摸屏输入的指令生成指定的电压参考波形,并读取FPGA中的模数转换结果,作为电压外环电流内环双闭环控制器的输入,实时控制输出电压,并把比较值传输到FPGA,和FPGA产生的三角载波进行比较得到PWM信号,PWM波经驱动模块输出驱动信号,控制IGBT的开通与关闭,经LC低通滤波器产生符合要求的三相交流电压,实现所需电压的稳定精确输出。

图2 电压暂降仪控制器架构框图

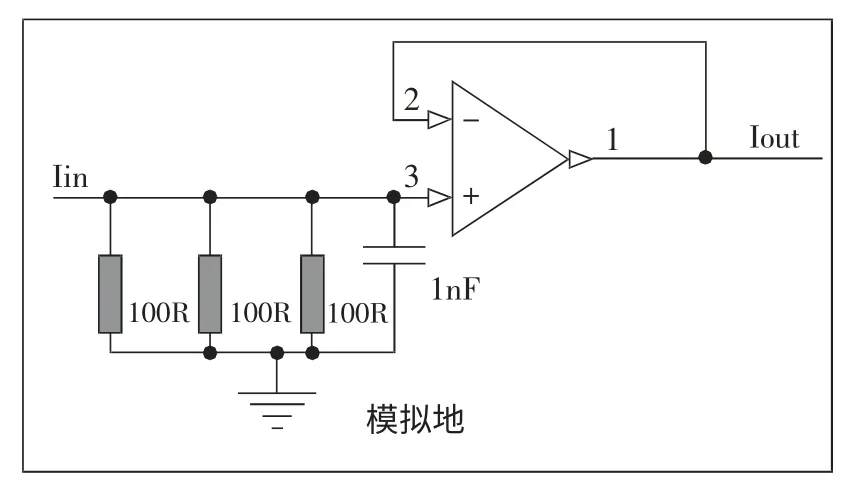

3.1.1 电压电流转换及调理电路

为了把电流信号转换成可作为A/D转换芯片输入的电压信号,需要设计电流调理电路对经过电流传感器后的信号进行处理。图3为逆变器输出电流的调理电路。图中运放采用LM258,1、2、3号管脚分别为运放的输出端、反向输入端、同相输入端。以A相电流为例,逆变器输出电流经过霍尔传感器后得到小电流信号Iin,Iin通过并联于运放同相输入端的3个100Ω电阻转换为电压信号,经过运放构成的电压跟随器后,最终得到适用于A/D转换芯片的电压信号Iout,其范围为-5V~5V。

图3 逆变器输出电流的调理电路

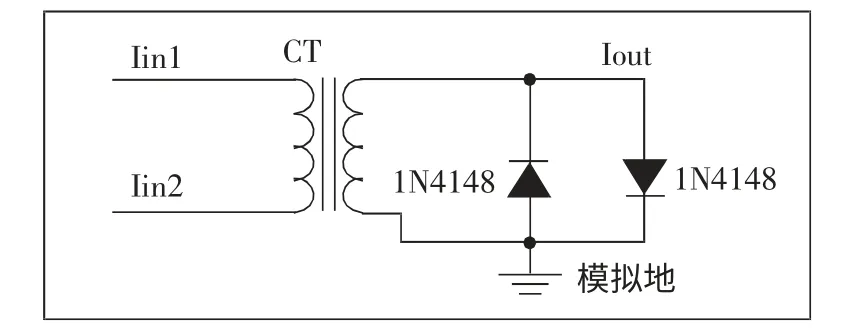

为了提高实际应用过程中使用的灵活性,对于负荷电流,可采用不同的外接电流互感器进行测量,本文设计要求外接电流互感器二次侧额定输出为5A,互感器二次侧输出电流需经板上CT进行再次转换,本文采用的板上CT变比为5A/2.5mA,负荷电流转换电路如图4所示,Iin1、Iin2分别接外接电流互感器二次侧两端,Iout为变换后的电流信号。

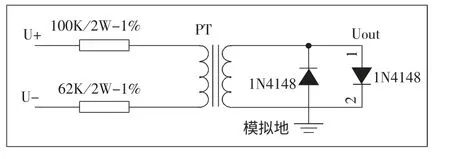

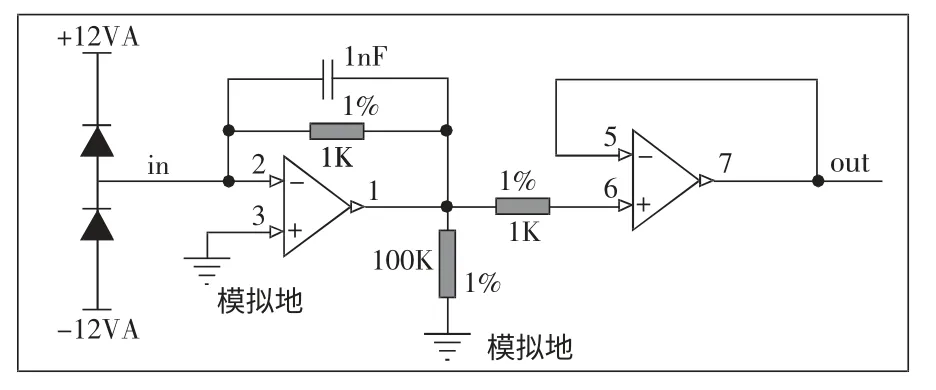

对于输出电压,本文采用图5所示的电压电流转换电路把电压信号转换为电流信号,图中PT变比为2mA/2mA,U+、U-为输出电压信号,Uout为与输出电压等比例的电流信号。图6为负荷电流、输出电压的调理电路。该电路输入为图4的Iout或图5的Uout,输出为-5V~5V的电压信号,作为A/D转换芯片的输入信号,图中运放采用LM258双运放模块,1、2、3、5、6、7均为引脚编号,其中输出引脚为1、7,同相输入端为3、5,反向输入端为2、6。

图4 负荷电流转换电路

图5 电压电流转换电路

图6 负荷电流/电压的调理电路

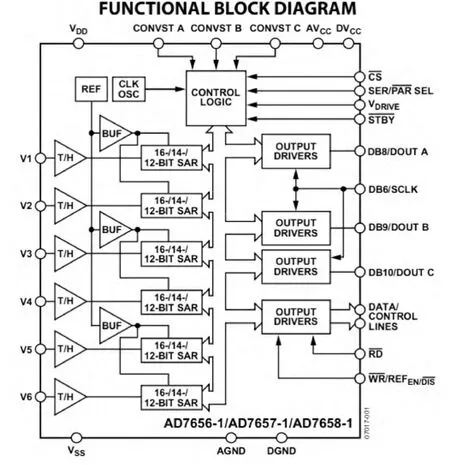

3.1.2 模数转换电路

基于本文架构设计的控制器为数字控制系统,因此必须把电流、电压信号模拟量转换成数字量。电流、电压的转换用于输出电压的双闭环控制,实现电压波形的精确稳定输出。另外,相关数据用于触摸屏上的显示。本文设计的采样频率为25.6kHz,对工频电压、电流信号每个周波(20ms)采样512个点。A/D转换芯片选用AD公司推出的AD7658模数转换芯片。该芯片模拟信号输入范围为-5V~5V,可支持6通道12位的高速采样转换,转换速率达250ksps,可完全满足要求。图7为AD7658的功能框图。

图7 AD7658的功能框图

3.1.3 驱动电路

FPGA的引脚电压为0或3.3V,不足以驱动IGBT工作,故要把其引脚电压转换后输出到IGBT的驱动电路,从而控制IGBT的开断。

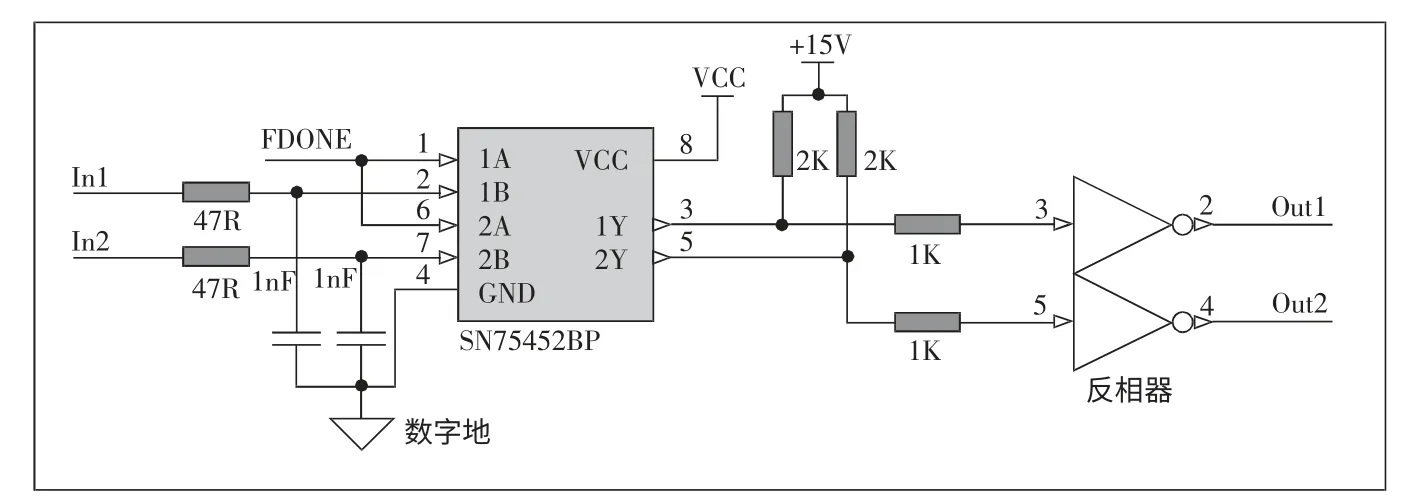

图9 电平转换电路

电平转换电路如图8所示,图中In1、Iin2为FPGA输出的同一相的上、下IGBT PWM信号,FDONE为封锁信号,Out1、Out2为经电平转换后的上、下IGBT控制信号FPGA输出的PWM信号,经光耦电路转换成0或15V。Out1、Out2经M57962L 集成电路模块产生IGBT的驱动信号,直接控制IGBT的开断。IGBT的驱动电路如图8所示,图中C1、G1、E1分别接IGBT的集电极、门极、发射极。

图8 IGBT的驱动电路

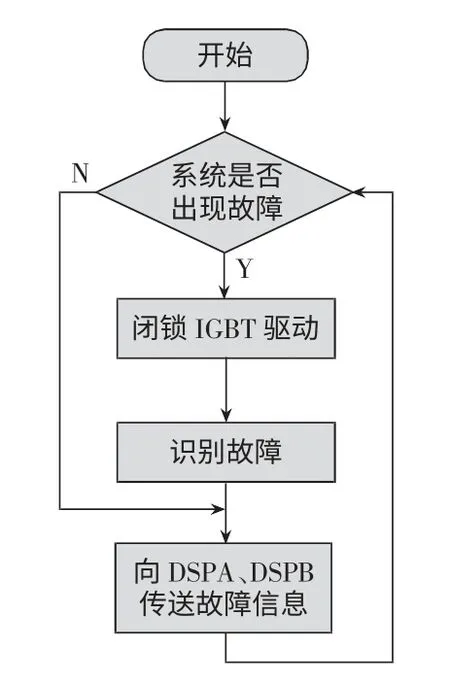

3.1.4 故障检测电路

FPGA负责检测全系统的故障并作出迅速反应。当出现直流侧过压或欠压、输出电流过流、AD转换芯片工作异常、DSP工作异常等故障时,FPGA经内部逻辑判断将作出故障处理,通过图9所示的FDONE信号封锁IGBT输出的同时并将故障情况显示于触摸屏。其中DSP工作检测和AD转换芯片检测由软件程序完成,过压欠压检测和过流检测需设计一定功能的前置电路,使故障电平信号能转换成可直接输入FPGA的信号,以便FPGA进行实时监测。

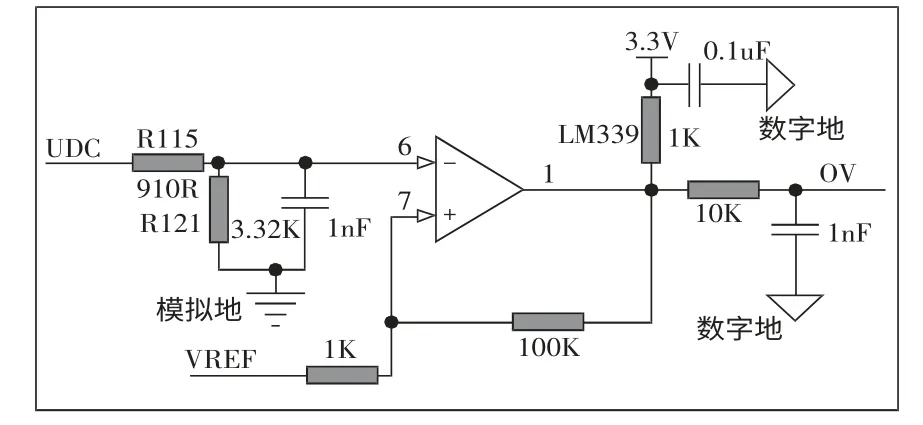

(1)过压欠压检测

本文的电压暂降仪为电压源型逆变器,输出指定电压前,要确保直流侧电容上的电压已经稳定在所需范围,若存在欠压现象,则不能保证有效输出,若存在过压,则可能导致功率器件的烧坏、电容爆炸等危险。因此,必须对直流侧电容的电压进行实时检测,迅速处理故障。

图10为过压检测电路。其中,UDC为直流侧电压经霍尔传感器后的值,根据设计,UDC为实际电压的0.00503倍。UDC经电阻R115和R121分压后,与基准电压VREF=3.3V比较,过压时OV为低电平,正常时为高电平。经计算可得,过压临界值为835V。

在图11所示的欠压检测电路中,基准电压VREF经电阻R116和R122分压后与UDC进行比较,由电路原理可知,欠压时UV为低电平,正常时为高电平。经计算可得,欠压临界值为298V。

必须清醒地把握打赢打好脱贫攻坚战面临的困难和挑战,切实增强责任感和紧迫感,一鼓作气、精锐出战、精准施策,以更有力的行动、更扎实的工作,集中力量攻坚,确保坚决打赢打好脱贫这场对我省如期高水平全面建成小康社会具有决定性意义的攻坚战。

图10 过压检测电路

图11 欠压检测电路

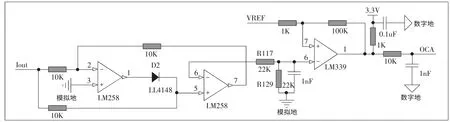

(2)过流检测

输出电流过大时,可能导致功率开关的烧坏等一系列损坏。因此,为了保证电路的安全可靠,必须实时对输出电流进行检测,以便迅速处理故障并报警。

图12 过流检测电路

图12为过流检测电路。图3所示输出电流调理电路的输出信号Iout作为图12电路的输入。检测过流时要检测电流的峰值,要保证电流最大时不出现过流。因此,Iout首先要经过整流环节,然后再与参考电平比较。Iout整流后经电阻R117和R129分压,然后与基准电压VREF进行比较。过流时OCA为低电平,正常时为高电平。结合CT变比(2000:1)和调理电路,经计算可得输出电流过流临界值为396A(峰值)。

3.2 控制器软件系统设计

3.2.1 FPGA程序设计

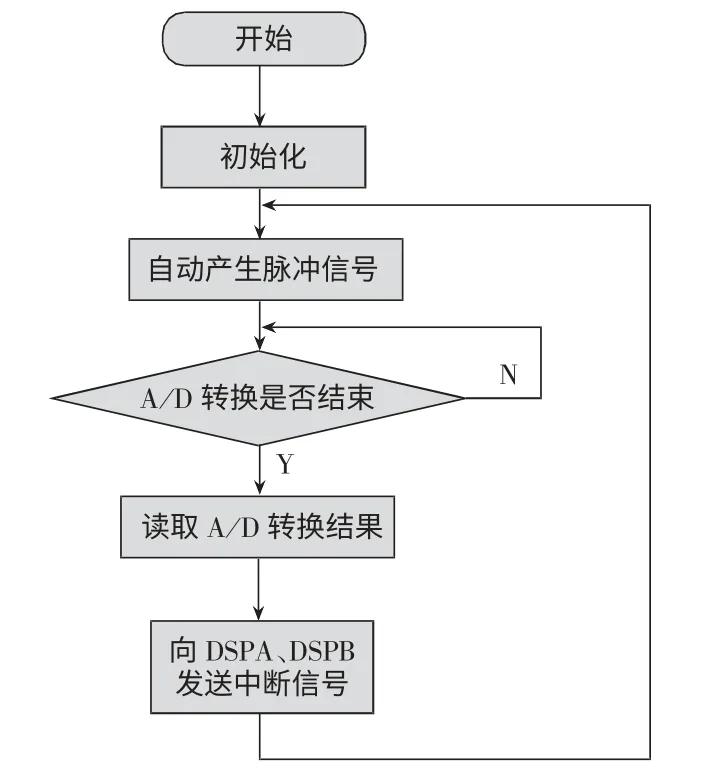

FPGA将由内部的计数器产生一系列的原始中断脉冲信号,此脉冲频率与采样频率一致,为25.6kHz,为了保证在每个中断周期内A/D转换芯片的模数转换结束后DSPB和DSPA才工作,此脉冲信号宽度为10μs。

此脉冲信号将控制A/D转换芯片、DSPB和DSPA协调可靠工作。

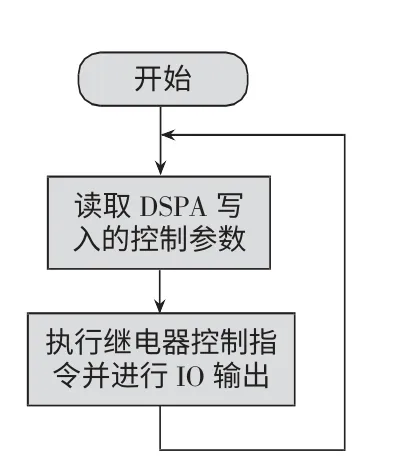

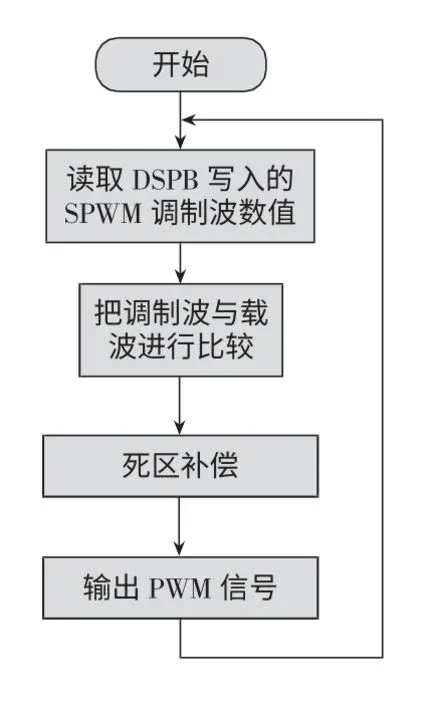

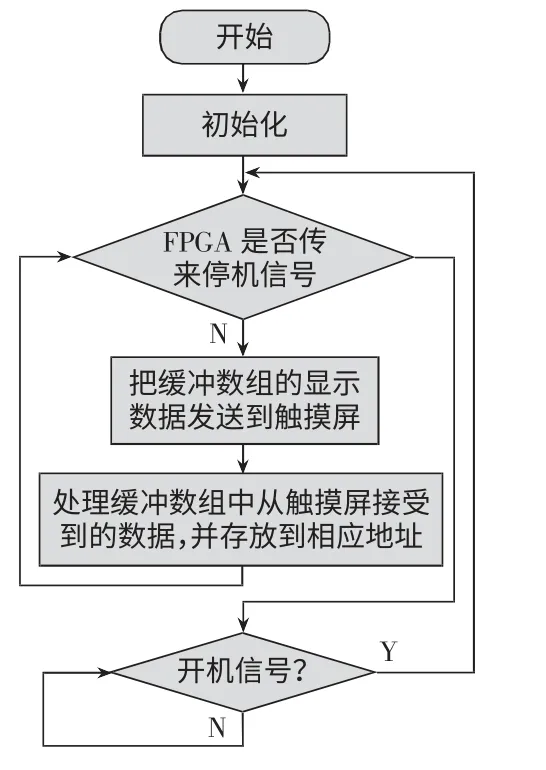

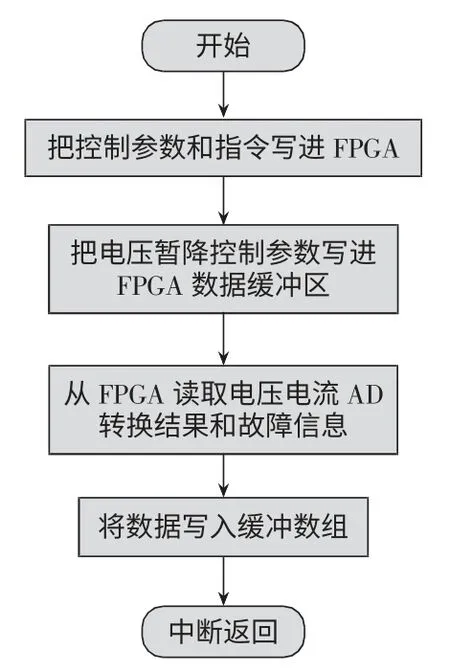

另外,FPGA还为两个DSP进行数据交互提供数据缓冲区,进行故障检测逻辑判断、PWM信号输出和普通IO输出控制。图13~图16为FPGA的程序设计流程图。

图13 FPGA的系统时钟脉冲序列产生模块

图14 FPGA的故障检测模块

图15 继电器控制IO输出模块

图16 PWM信号生成模块

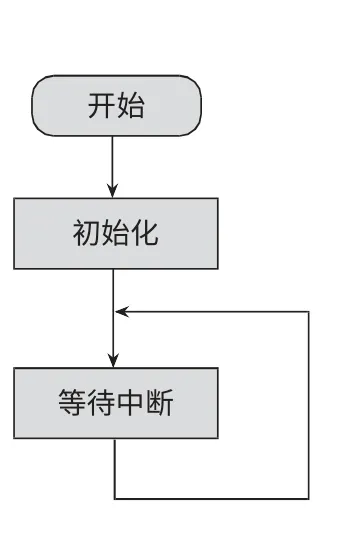

图17 DSPA的主程序设计流程图

图18 DSPA的外部中断程序

图19 DSPB主程序流程图

DSPA是进行人机交互的重要环节,来自触摸屏控制指令和控制参数将经过DSPA写进FPGA,从而控制系统的运行,同时,DSPA从FPGA读取数据,在触摸屏上显示出来。DSPA的程序设计如图17和图18所示,DSPA与触摸屏之间通过一个缓冲数组进行数据传输。

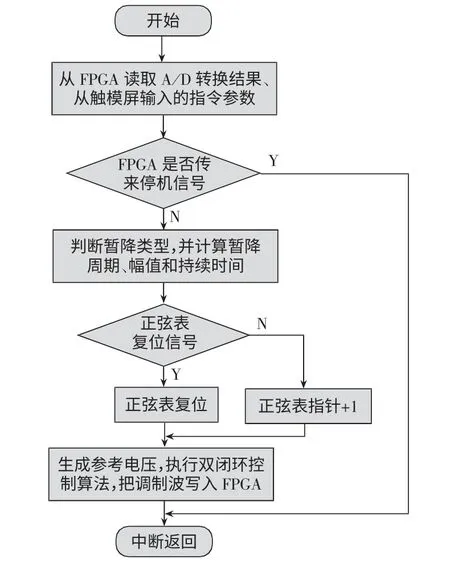

3.2.3 DSPB程序设计

DSPB是电压控制算法的核心执行器件,主要负责输出电压波形的精确控制,控制算法采用电压外环电流内环的双闭环控制算法。图19和图20为DSPB的程序设计流程图。

图20 DSPB的外部中断程序设计流程图

4 实验结果

按照上文的设计,本文搭建了电压暂降仪整体实物图进行测试,如图21所示。实验样机为三相三线制,只能输出线电压,具体参数见表1。其控制器采用正弦脉宽调制(SPWM)控制方法,其中载波频率为12.8kHz。实现了暂降(暂升)起始相位、持续时间、幅度均可调的电压波形输出。

图21 电压暂降仪整体实物图

表1 电压暂降仪具体参数

经日置HONKI3196测试,本文设计的电压暂降仪能够产生精度较高的有不同幅值、持续时间及相位的电压暂降信号,可满足各种相关的实验需求。

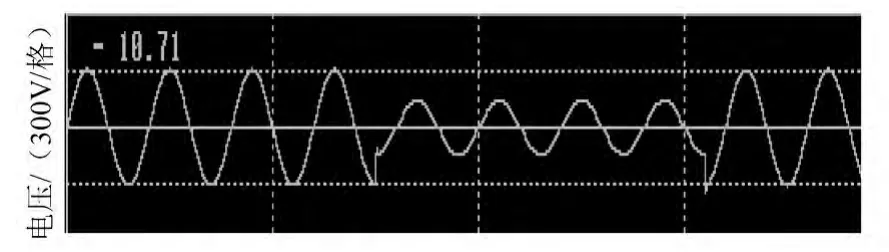

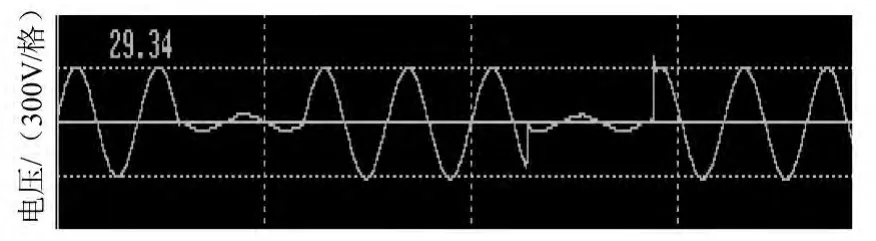

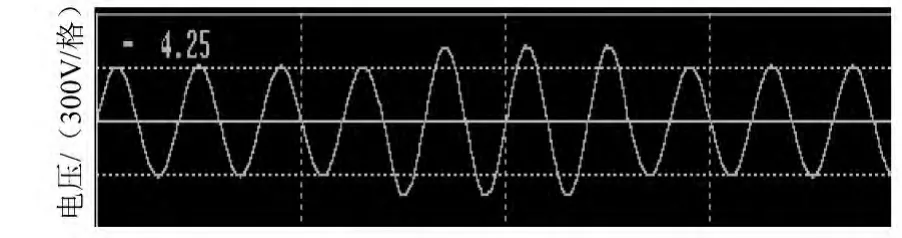

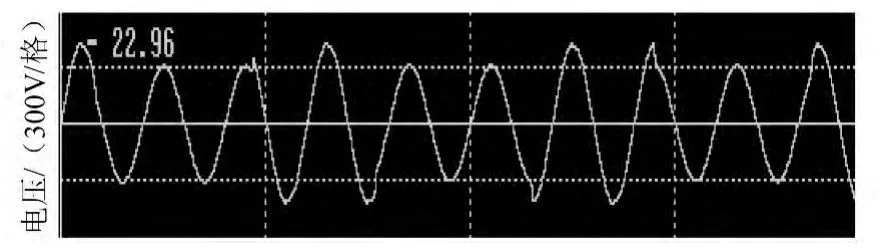

图22~图25为日置HONKI3196测得的电压暂降波形示例图,其中图22为4周波的电压暂降与恢复波形,暂降幅度为48%,暂降起始相位为270°。图23为连续2次1.5周波的电压暂降与恢复波形,暂降幅度为88%。图24为3周波的电压暂升与恢复波形,暂升幅度为38%。图25为连续3次1.5周波的电压暂升与恢复波形,暂升幅度为38%。

图22 暂降波形1

图23 暂降波形2

图24 暂降波形3

图25 暂降波形4

5 结束语

本文设计了基于双DSP和FPGA控制器的电压暂降仪。FPGA负责全系统脉冲信号的输出、故障检测和处理、PWM信号的输出、IO控制的输出并作为两个DSP数据交互的平台,其中一个DSP负责触摸屏的数据显示及指令读入,另一个DSP负责对输出电压进行电压外环电流内环双闭环精确控制。该设计结合各处理器的功能特点,充分发挥其功能优势,使整个控制系统效率得到了进一步提高。测试结果表明,该电压暂降仪能够产生理想的电压暂降信号,控制器运行效率高、实时性强、控制精度高。

[1]肖湘宁,徐永海.电能质量问题剖析[J].电网技术,2001,25(3):66-69.

[2]林海雪.现代电能质量的基本问题[J].电网技术,2001,25(10):5-12.

[3]汪 颖,肖先勇,杨 达.敏感设备电压暂降失效事件不确定性的最大混合熵评估[J].电网技术,2012,36(11):159-164.

[4]肖先勇,马 超,杨洪耕,李华强.用电压暂降严重程度和最大熵评估负荷电压暂降敏感度[J].中国电机工程学报,2009,29(31):115-121.

[5]袁 媛,吴丹岳,林 焱,等.电压暂降评估体系研究[J].电网技术,2010,34(6):128-133.

[6]张 威,郑常宝,王 萍,等.基于自耦调压器的电压暂降发生器研究[J].电力电子技术,2011,45(3):88-90.

[7]陈增禄,姚伟鹏,毛惠丰,宋 健.一种电压暂变发生器研究[J].电力电子技术,2007,41(3):97-99.

[8]陈文波.电压暂降发生仪[P].中国专利:201120295494.2[P],2012-04-25.

[9]颜湘武,张 波,王树岐,等.三相电压暂降发生器[P].中国专利:201010188565.9[P],2010-11-17.

[10]赵剑锋,王 浔,潘诗锋.基于双脉宽调制变换器和电压滞环控制的电能质量信号发生装置[J].电网技术,2005,29(4):41-43.

[11]赵剑锋,王 浮,潘诗锋.大功率电能质量信号发生装置设计及实验研究[J].电力系统自动化,2005,29(20):71-75.

[12]张香真,张建成.一种电能质量干扰发生器的研究及仿真[J].供用电,2004,21(1):27-29.