一种基于双模冗余的扫描结构TSPC 型D 触发器设计

2023-11-07曹雪兵

曹雪兵

(中国电子科技集团公司第四十七研究所,沈阳 110000)

1 引 言

随着工艺技术的不断发展,集成电路晶体管的寄生电容进一步降低,这也使得集成电路中敏感节点的临界电荷不断减小,导致集成电路对软错误愈发敏感[1-2]。由单粒子翻转所引起的时序逻辑电路中存储数据的失效一直是业界最为关注的重点。特别是在先进工艺节点的微处理器、微控制器及SoC 中,大量的触发器逻辑分布于芯片各处,设计出抗单粒子翻转的触发器成为系统可靠工作的重要保障[3-5]。进入纳米工艺节点后,组合逻辑电路中所产生的单粒子瞬态脉冲成为了继单粒子翻转后又一关键问题,在纳米集成电路中,组合逻辑所产生的单粒子瞬态脉冲宽度已与时钟脉宽相当,当瞬态脉冲在触发器锁存窗口内到达触发器的数据输入端时,该瞬态脉冲同样会引发逻辑错误[6-7]。据报道,在65nm 工艺节点,由单粒子瞬态所引发的软错误问题达到了与单粒子翻转相同的规模,在45 nm 甚至更先进的工艺节点,由单粒子瞬态所引起的软错误将成为危害集成电路可靠性的主要因素[8]。传统的抗单粒子效应的加固方法包括三模冗余技术以及DICE 单元加固技术,基于空间冗余设计思想的三模冗余技术通过将电路复制三份,然后采用表决器进行表决,从而得到正确的逻辑值[9]。DICE 单元通过将敏感节点进行备份,进而克服单粒子效应的影响。三模冗余结构会消耗较大的面积和功耗,而DICE 结构无法处理SET 问题[10-11]。本研究即基于双模冗余加固思想,对现有设计进行改进,实现一种具有扫描输入功能的TSPC(True Single Phase Clock, 真单相时钟)型D触发器,TSPC 型触发器相对于传统需要互补时钟信号的D 触发器,其主要优势在于面积与性能的提升。本设计基于普通TSPC 型D 触发器改进完成。

2 普通TSPC 型D 触发器

触发器是微处理器、微控制器及SoC 等数字系统的基本存储单元,其面积和功耗占整个数字系统的相当大部分比重。目前广泛采用的触发器结构为采用传输门所实现的主从结构触发器,如图1 所示。传统触发器无法应用于高可靠环境当中。首先,触发器内的锁存结构在粒子轰击下可能会直接发生单粒子翻转。其次,触发器输入数据信号的脉冲信号波动如果落在触发器的锁存窗口内,继而被捕获也会诱发触发器发生单粒子翻转现象,两种情况都会破坏触发器输出端的逻辑值。

图1 传统D 触发器逻辑结构及单粒子效应示意图

图2所示为普通TSPC 型D 触发器的逻辑图。该逻辑电路由四级反向逻辑所构成,当时钟信号CLK 为低电平时,假设D 此时输入数据为1,则P1管关断、N1管导通,net1 被拉到低电平,如果此时粒子入射P1管的漏极,会在net1 中引入瞬态脉冲,继而将输出端Q 的高电平下拉至地,从而引起输出信号的翻转。

图2 普通TSPC 型D 触发器逻辑结构

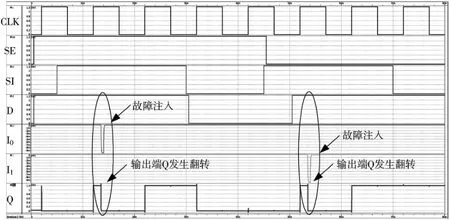

图3给出了基于UMC 55 nm 工艺的带有扫描输入功能的普通TSPC 型D 触发器的SEU 仿真结果。扫描输入使能端SE 为高电平,此时扫描输入数据端SI 信号有效,在13.5ns 时注入双指数电流脉冲,幅值为10mA,持续时间500ps,上升时间、下降时间皆为50ps。触发器的数据输出端在脉冲注入后翻转为低电平,输出发生翻转。当扫描输入使能端SE 为低电平时,输入数据端D 有效,在53.5ns 时注入双指数电流脉冲,脉冲参数与上述注入过程设置相同。从仿真结果可见,触发器的输出端同样发生了翻转。

图3 普通TSPC 型D 触发器单粒子翻转仿真结果

如图4 所示为数据输入端引入瞬态脉冲后,对普通TSPC 型D 触发器进行仿真的结果。瞬态脉冲的注入时刻为61.9ns,脉冲宽度300ps。从仿真结果可见,在时钟信号的上升沿,触发器采到了故障脉冲的低电平,从而引起输出端Q 值的翻转。

图4 普通TSPC 型D 触发器单粒子瞬态仿真结果

3 改进的D 触发器结构

在普通设计基础上进行改进,在此提出基于双模冗余的扫描结构的TSPC 型D 触发器(简称SDM-TSPC)的逻辑结构如图5 所示。

为提高系统的可测性能力,此处设计了由P1~P5及N1~N5等晶体管所构成的扫描输入电路,由扫描输入控制端SE、扫描输入数据端SI 及扫描输出端Q为扫描输入功能的输入输出测试端口。在运行扫描移位模式时,设置SE 为高电平,此时SI 有效,在时钟上升沿采样该输入信号输出至触发器的输出端。在对系统进行故障检测时,通过将普通触发器替换成扫描触发器,完成扫描链的插入,进一步利用测试矢量对故障点进行测试。扫描输入电路的设计增加了该触发器应用时可测性设计方面的灵活性。

相关研究显示,在纳米工艺节点,由单粒子轰击所产生的单粒子瞬态脉冲宽度最大可达700ps[12-13]。单粒子瞬态脉冲宽度的增加会大大提高其被捕获的概率,导致系统软错误率的升高。在SDM-TSPC 型D 触发器中,设计了由晶体管P11~P14及N11~N14所构成的延迟单元,采用工作在饱和状态的晶体管来获得延迟,相比于普通延迟单元具有更低的功耗[14]。在延迟单元以及由CLK 信号控制的C 单元共同作用下,SDM-TSPC 型D 触发器可以抑制数据输入端信号上瞬态脉冲的影响[15]。

4 仿真结果与分析

通过仿真,得到基于UMC 55nm 工艺的SDMTSPC 型D 触发器的SEU 仿真结果,如图6 所示。扫描输入使能端SE 为高电平,此时扫描输入数据端SI 信号有效,在13.5 ns 时注入双指数电流脉冲,参数设置与常态TSPC 型触发器仿真时的参数保持一致。触发器的数据输出端在脉冲注入后保持高电平,输出端未受到故障注入的影响。当扫描输入使能端SE 为低电平时,输入数据端D 有效,在53.5ns 时注入双指数电流脉冲,脉冲参数与上述注入过程设置相同。从仿真结果可见,触发器的输出端同样保持原始输出值,输出结果未受到故障注入的影响,从而也证明所提出的SDM-TSPC 型D 触发器具有抗SEU的能力。

图6 SDM-TSPC 型D 触发器单粒子翻转仿真结果

为了评估SDM-TSPC 型D 触发器在真实辐照环境下的抗SEU 能力,采用故障注入的软错误敏感性评估方法,对普通TSPC 型D 触发器和改进后的SDM-TSPC 型D 触发器分别进行故障注入仿真[16]。故障注入脉冲采用双指数电流源的形式,脉冲幅度设置为4×10-4A,脉冲持续时间设置为100~500 ps之间的随机值。该脉冲宽度区间为粒子辐照产生瞬态脉冲的主要分布区间。脉冲的上升时间和下降时间设置为50ps[17-20]。在故障注入过程中,双指数电流源产生于100 个时钟周期内,并被随机注入到D 触发器逻辑结构中的不同电路节点。故障注入的仿真共执行10000 次,得到故障注入仿真结果,具体普通TSPC 型D 触发器在10000 次故障注入实验中,发生单粒子翻转并最终导致输出信号发生错误共374次;SDM-TSPC 型D 触发器在10000 次故障注入过程中发生单粒子翻转共39 次。通过对故障注入过程中故障注入点的分析可知,此39 次脉冲注入均发生在SDM-TSPC 型D 触发器的最终输出级(N23~N26,P23~P25),而内部敏感节点未出现由于故障脉冲注入引起的输出端数据错误的现象,由此也可证明双模冗余结构在抗单粒子翻转方面的有效性。

如图7 所示为数据输入端引入单粒子瞬态脉冲的仿真结果。瞬态脉冲的注入时刻为61.9ns, 脉冲宽度300ps,与普通TSPC 型注入脉冲的参数设置相同。从仿真结果可见,在CLK 时钟上升沿时刻,输入信号D 上产生瞬态脉冲,但此时触发器输出端Q的逻辑电平未受影响,仍然保持瞬态脉冲注入前的高电平。仿真结果证明了所提出的SDM-TSPC 型D触发器具有抗SET 的能力。

图7 SDM-TSPC 型D 触发器的单粒子瞬态仿真结果

5 结 束 语

改进后的基于双模冗余的带有扫描输入功能的TSPC 型D 触发器,其扫描输入功能的设计提高了触发器应用过程中的可测性能力。基于UMC 55nm工艺,在电路级对普通TSPC 型D 触发器和所提出的SDM-TSPC 型D 触发器进行了SEU 与SET 的模拟仿真分析,通过故障注入实验进行验证,结果表明SDM-TSPC 型D 触发器具有较好的抗单粒子翻转和单粒子瞬态的能力。采用双模冗余结构能够实现抗单粒子翻转加固,通过引入延迟单元结构有助于消除输入数据信号所产生的SET 瞬态脉冲,扫描输入功能的加入也使得该触发器具有较高灵活性,大大提高了系统的可测性设计。