主从JK触发器逻辑功能分析

2017-12-02大连计算机职业中专

大连计算机职业中专 梁 伟

主从JK触发器逻辑功能分析

大连计算机职业中专 梁 伟

触发器是一种最简单的时序逻辑电路,在各类集成触发器中,JK触发器的逻辑功能最为齐全,通过proteus模拟软件进行分析主从式结构JK触发器逻辑功能,能够直观判断JK 触发器逻辑功能。

JK触发器;模拟软件

数字电路按逻辑功能的不同分为组合逻辑电路和时序逻辑电路,组合逻辑电路显著特点没有记忆功能。时序逻辑电路显著特点有记忆功能,时序逻辑电路包含触发器,触发器具有记忆功能,能够存储一位二进制数字信号,是构成其它时序逻辑电路的基本逻辑单元,触发器也是一种最简单的时序逻辑电路。在各类集成触发器中,JK触发器的逻辑功能最为齐全。在实际应用中,它有很强的通用性,能灵活地转换成D触发器和T触发器。

JK触发器电路结构:

JK触发器大多采用主从式结构,是一种功能较完善,应用很广泛的双稳态触发器。如图所示是一种典型结构的JK触发器—主从型JK触发器。它由两个可控RS触发器组成,分别称为主触发器和从触发器,又加上两条反馈线构成。增加两条反馈线目的,是克服电路存在不定态的缺点。在主从R-S触发器的基础上引入两根线,Q引入到门G8的输入端,引入到门G7的输入端,S换成J(,称为置位端),R换成K(,称为复位端)。 J和K是信号输入端。主从JK触发器只在CP时钟脉冲的下降沿触发翻转。

下面通过proteus模拟软件进行分析主从式结构JK触发器逻辑功能:

2、当CP=1时,主触发器的输入门G7和G8打开,主触发器接收信号,主触发器根据输入J、K的状态触发改变,并存储在主触发器中等待输出;而对于从触发器, CP=0,G5和G6被封锁,其状态不受主触发器输出的影响,所以从触发器的状态保持不变。

3、当CP=0时,主触发器输入门G7和G8 被封锁,主触发器的状态保持不变。从触发器输出状态与主触发器的输出状态相同,即主从JK触发器在CP=0期间状态保持不变。

4、当CP从1变成0时,即主从触发器是在CP↓下降沿到来时才使触发器翻转的。主触发器的状态传送到从触发器。下面分四种情况来分析主从JK触发器的逻辑功能。

(1) J=0,K=0 ,当CP↓下降沿到来时,触发器状态保持,即Q n+1=Q n。

无论触发器的现始状态Q n= 0为0还是1,在CP=1期间,由于主触发器的J=0,K=0,主触发器的输入门G7和G8 被封锁,主触发器的状态保持不变。当CP下降沿到来时,从触发器保持状态不变,即Q n+1=Q n。

(2) J=0,K=1 , 当CP↓下降沿到来时,触发器置0,即Q n+1= 0。

若触发器的现始状态Q n=0,在CP=1期间,当J=0,K=l时,反馈线将Q n=0引到主触发器的G8输入端,主触发器的输入门G7和G8同时被封锁,主触发器的0态保持不变。当CP下降沿到来时,从触发器保持0态不变。即Q n+1= 0。

若触发器的现始状态Q n=1,由于主触发器的,根据可控RS触发器功能,主触发器置0。当CP下降沿到来时,从触发器也翻转成0态,即Q n+1= 0,且在CP=0期间状态保持不变。

(3)J=1,K=0,当CP↓下降沿到来时,触发器置1,即Q n+1=1

(4) J= l,K=1,当CP↓下降沿到来时,触发器翻转,即Q n+1=,具有计数功能。

设触发器的现始状态Qn=0,则=1,在CP=1期间,当J=l,K=l时,两条反馈线将引到主触发器的G7和G8输入端,,根据可控RS触发器功能,主触发器置1。当CP下降沿到来时,从触发器也翻转成1态,原来的状态0翻转1,即Qn+1=。

表1

由以上分析,在J=K=1时,每输入一个时钟脉冲,触发器翻转一次。触发器的这种工作状态称为计数状态,由触发器翻转的次数可以计算出输入时钟脉冲的个数,即Qn+1=,具有计数功能。JK触发器的逻辑功能表如表1所示。

JK触发器具有置位、复位、保持(记忆)和计数(翻转)功能;由于接收输入信号的工作在CP↓下降沿前完成,在下降沿触发翻转,在下降沿后触发器被封锁,抗干扰性能好,工作速度快,在实际应用中,它有很强的通用性,能灵活地转换其他类型的触发器。

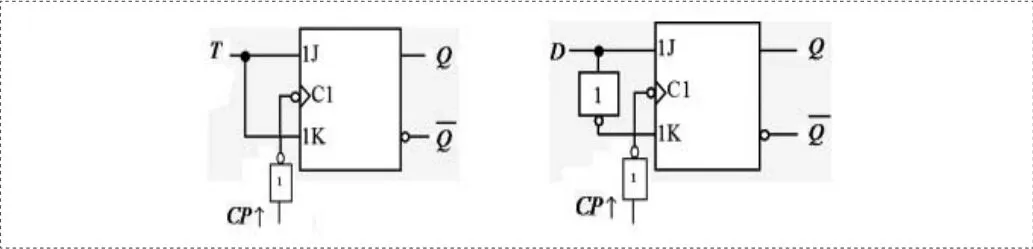

由JK触发器变换得到T触发器,令JK触发器的输入J=K=T,则由JK触发器变换得到T触发器。当T=J=K=0时,CP↑脉冲上升沿到达时,触发器输出状态保持;当T=J=K=1时,CP↑脉冲上升沿到达时,触发器发生计数(翻转)。CP脉冲触发变换:上升沿触发 CP↑。

[1]阎石.数字电子技术基础[M].清华大学电子教研组.