用于无人机卫星通信的LDPC高速编码器实现

2023-09-06田宇卢志鹏

田宇 卢志鹏

摘 要:为满足无人机卫星通信系统中高清音视频数据高通量、低功耗、高可靠传输的需求,提出一种基于DVB_S2标准的LDPC编码器。该编码器采用两级并行RAM存储阵列,可有效提高系统工作频率,降低FPGA逻辑资源的使用率,通过控制模块使编码器自适应兼容三种码率的LDPC编码。上述编码器已在ZYNQ 7Z020系列芯片xc7z020clg400-2上实现,最高稳定工作主频为214.4 MHz,支持1/2、3/4、7/8三种典型码率。

关键词:卫星通信;无人机;FPGA;LDPC;编码器

中图分类号:TN911.22;TN927+.21 文献标识码:A 文章编号:2096-4706(2023)14-0075-05

Realization of LDPC High-speed Encoder for UAV Satellite Communication

TIAN Yu, LU Zhipeng

(Beijing Aerospace Control Instrument Research Institute, Beijing 100854, China)

Abstract: To meet the requirements of high throughput, low power consumption, and high reliability transmission of high-definition audio and video data in UAV satellite communication systems, a LDPC encoder based on DVB_S2 standard is proposed. The encoder adopts a two-level parallel RAM storage array, which can effectively improve the system's operating frequency and reduce the utilization of FPGA logic resources. Through the control module, the encoder is adaptively compatible with LDPC encoding of three different bit rates. The above encoder has been implemented on the ZYNQ 7Z020 series chip xc7z020clg400-2, with a maximum stable operating frequency of 214.4 MHz and supporting three typical bit rates: 1/2, 3/4, and 7/8.

Keywords: satellite communication; UAV; FPGA; LDPC; encoder

0 引 言

高清音视频数据在无人机卫星通信领域的普及,使得无人机载卫星通信传输的数据量大幅增加。由于无人机飞行可携带设备载荷重量有限,无人机载卫星通信系统的系统容量和功耗均受到限制,相比于地面卫星通信息系统,无人机载卫星通信系统的信道传输带宽更窄、接收信噪比更低,这种环境对卫星通信的纠错码性能提出了更高的要求,以保证在带宽受限的情况下准确无误的传输高清音视频等高速数据。

第二代数字视频广播(the second generation digital video broadcat, DVB-S2)标准是专门为支持高清音视频业务建立的,它更符合高清视频数据对卫星通信的需求。其采用BCH+LDPC级联信道编码,纠错性能接近香农限。在支持低阶调制(QPSK、8PSK)的同时还支持16APSK和32APSK高阶调制,大大提高了带宽受限情况下的数据传输速率。其优秀的性能能够支持高清音视频数据在无人机载卫星通信系统上的传输应用。

为满足高清音视频數据在无人机卫星通信上的应用需求,本文作者针对DVB-S2标准的LDPC码特性,在其基础上提出一种高速率、多码率支持的LDPC编码器。该编码器工作速度快,资源占用率低,能够支持码长为16 200,码率为1/2(4/9)、3/4(11/15)以及7/8(8/9)的三种编码结构。

1 DVB-S2标准LDPC编码算法

LDPC码的构造方法有代数构造法、准循环以及随机构造法。随机或伪随机构造方法生成的LDPC码性能接近香农限,DVB-S2标准中LDPC码采用类似方法。

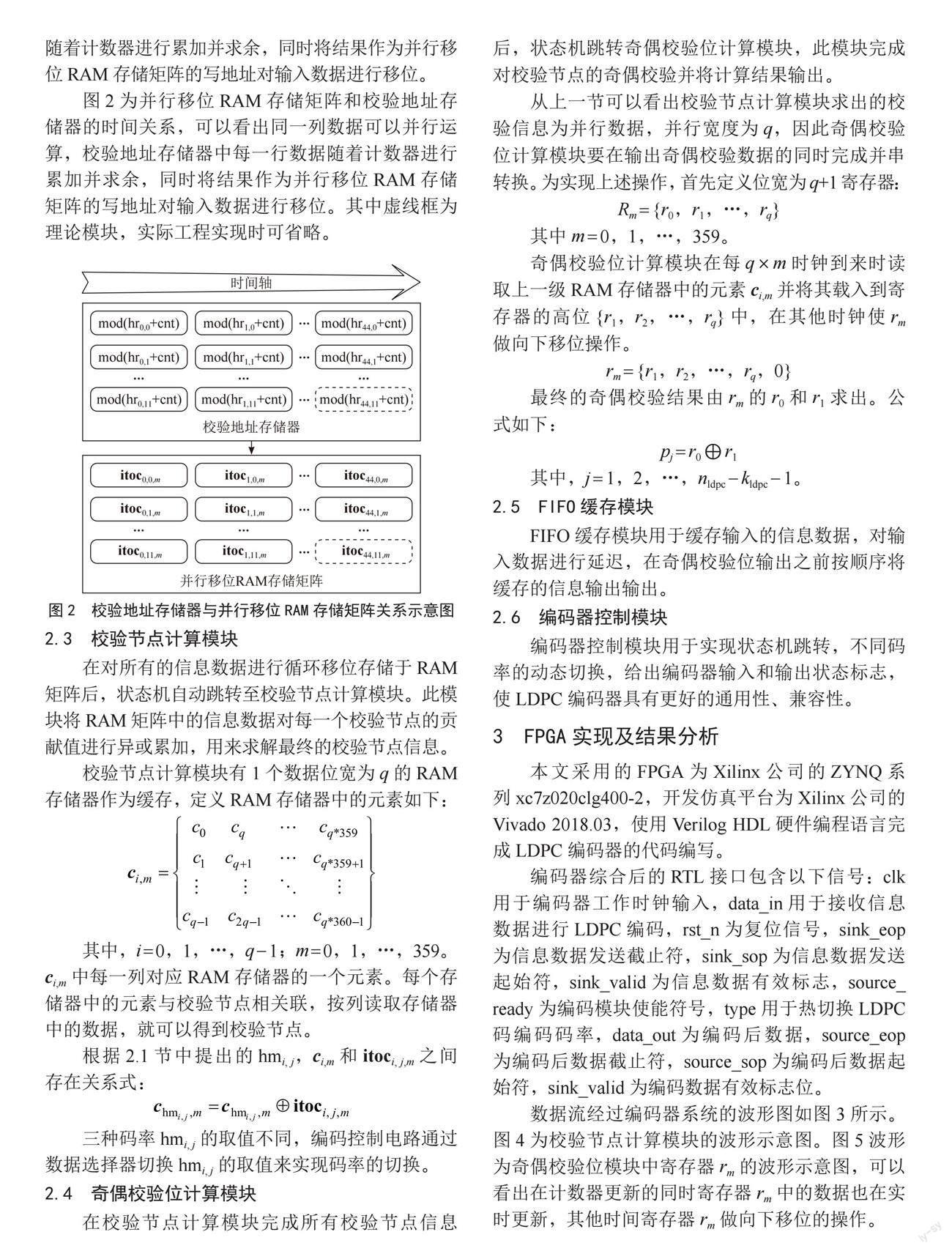

DVB-S2标准中LDPC码为非规则累计码,即IRA码,其校验矩阵可以表示为H = [H1 H2]的形式。其中H1是一个稀疏矩阵,矩阵大小为(nldpc - kldpc)×

nldpc,其中nldpc表示LDPC码总长度,kldpc表示信息比特长度。矩阵H2是固定形式矩阵,为双对角线形式:

H1校验矩阵是稀疏矩阵且具有周期性。DVB-S2标准中H1可以按照每连续的360列为一组分解为kldpc/360组,且每组的列重必须相同。第m列中‘1所在行的位置由DVB-S2标准附录B和C中表格的第 行对应的数据加上m mod(360×q),其中 表示对m/360向下取整,q为步长,与LDPC码的码长和码率有关。

结合H1和H2两个矩阵的特点,其基本编码算法步骤如下:

1)初始化校验位:

2)对校验矩阵非零位置的数据进行累积异或。规则为:

pj = pj ⊕ im

j = {x + m mod360×q} mod(nldpc - kldpc)

其中,pj表示第j校验位,im表示第m信息位,x取值参考DVB-S2标准附录B和C提供的地址表,q表示步长。以码长16 00、码率3/4(11/15)的基校验矩阵第1行第5列为1 481,则其第1列对应的非零坐标行位置{1 481 + (1 mod 360)×12}mod(16 200 - 11 880)。

3)按照下式求解最终的奇偶校验比特,即:

pj = pj ⊕ pj-1

其中,j = 1,2,…,nldpc - kldpc - 1。

4)顺序拼接信息比特和奇偶校验比特并发送。编码后的码字如下:

2 LDPC编码器结构

LDPC编码器主要结构为三段状态机,在状态机时间顺序的基础上进行功能分块,主要分为校验地址存储器、并行移位RAM存储矩阵、校验节点计算模块、奇偶校验位计算模块、FIFO缓存模块和编码器控制单元。系统图如图1所示。

2.1 校验地址存储器

在DVB-S2标准中附录B和C给出了LDPC编码各种码率的校验位地址,因为IRA_LDPC码校验矩阵设计的伪随机特性无法使用数学公式进行描述,所以需将校验位地址存放在ROM中。为了实现信息数据到校验节点的转换,同时降低FPGA除法与求余运算带来的资源消耗,需要对校验位地址进行除法运算并向下取整后存入ROM中,且对校验位地址进行求余运用,运算的结果用于后续模块算法推导。

除法取整公式为:

求余公式为:

hmi, j = mod(x,q)

其中,i = 0,1,2,…,45 - q - 1,j = m/360,x取值参考DVB-S2标准附录B和C提供的地址表,q为步长。

通过标准附录中地址表可以看出,对于码长为16 200的LDPC码在上述公式的计算结果不会大于360,据此设计ROM数据位宽为9×12,其中9为单字节位宽,12为校验矩阵最大列重,这种处理方法可以使ROM一次性载入一整列校验地址。

本文提出的编码器兼容三种码率,此三种码率的校验地址表可存放于同一个ROM中的不同地址上。其中1/2(4/9)码率占用地址0~19,3/4(11/15)码率占用地址20~52,7/8(8/9)占用地址53~93,通过编码控制电路,可设置偏移地址选择不同码率的校验地址。

2.2 并行移位RAM存储矩阵

在有效数据输入信号使能后,程序跳转至并行移位RAM存储矩阵模块,此模块按照标准对信息数据进行循环移位存储并将结果存储于并行RAM存储矩阵中。

参考DVB-S2标准附录,B和C中码长16 200,码率1/2(4/9)、3/4(11/15)和7/8(8/9),最大列重为12,最大列重行数5行。根据以上总结,定义大列重RAM存储矩阵12×5,标准列重RAM存储矩阵3×35,所有RAM存储单元位宽为1,数据深度为360。定义RAM存储矩阵元素为:

itoci, j,m = {itoci, j,0,itoci, j,1,…,itoci, j,359}

RAM存储矩阵单元中数据和信息数据存在如下关系:

其中hri, j由校验地址存储器给出,循环移位操作由一个360的计数器实现。由上述算法可以看出同一列数据可以并行运算,校验地址存储器中每一行数据随着计数器进行累加并求余,同时将结果作为并行移位RAM存储矩阵的写地址对输入数据进行移位。

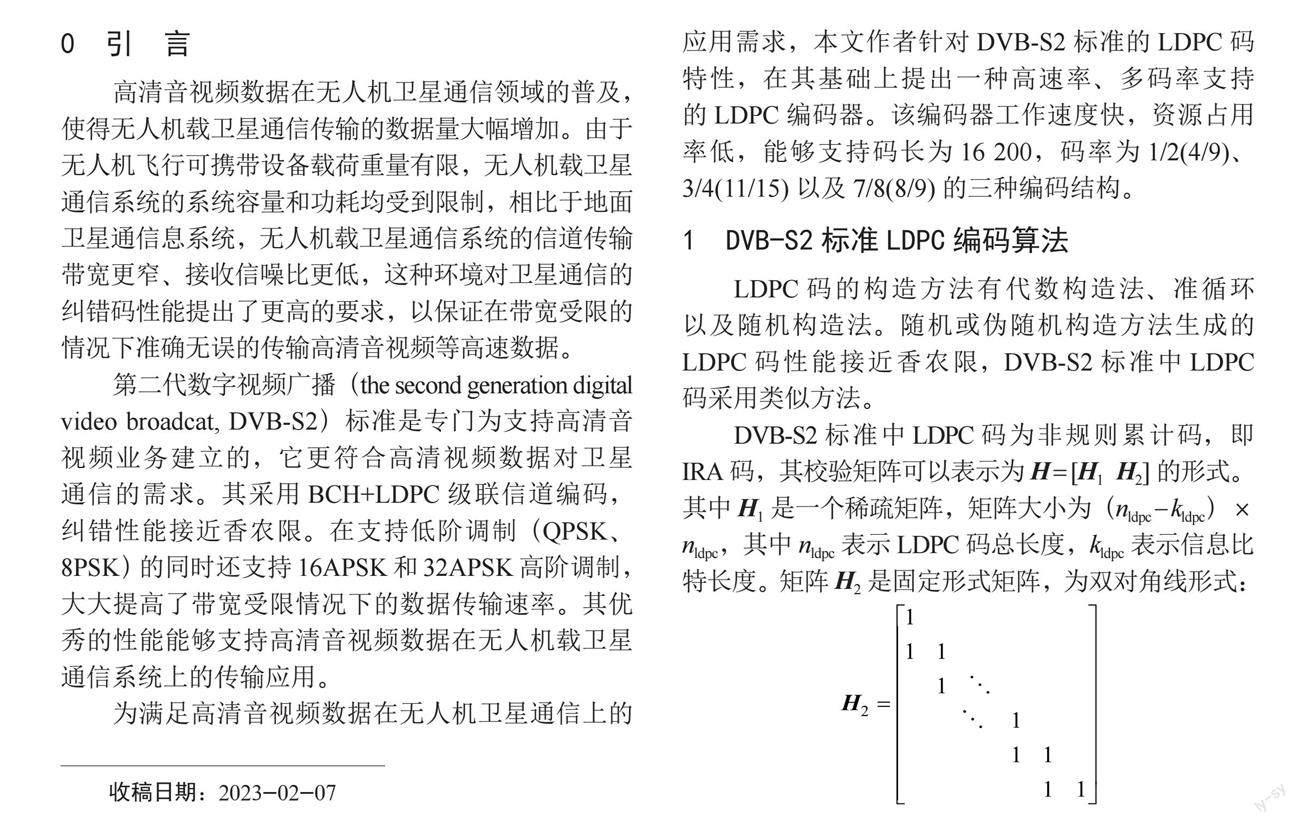

图2为并行移位RAM存储矩阵和校验地址存储器的时间关系,可以看出同一列数据可以并行运算,校验地址存储器中每一行数据随着计数器进行累加并求余,同时将结果作为并行移位RAM存储矩阵的写地址对输入数据进行移位。其中虚线框为理论模块,实际工程实现时可省略。

2.3 校验节点计算模块

在对所有的信息数据进行循环移位存储于RAM矩阵后,状态机自动跳转至校验节点计算模块。此模块将RAM矩阵中的信息数據对每一个校验节点的贡献值进行异或累加,用来求解最终的校验节点信息。

校验节点计算模块有1个数据位宽为q的RAM存储器作为缓存,定义RAM存储器中的元素如下:

其中,i = 0,1,…,q - 1;m = 0,1,…,359。ci,m中每一列对应RAM存储器的一个元素。每个存储器中的元素与校验节点相关联,按列读取存储器中的数据,就可以得到校验节点。

根据2.1节中提出的hmi, j,ci,m和itoci, j,m之间存在关系式:

三种码率hmi, j的取值不同,编码控制电路通过数据选择器切换hmi, j的取值来实现码率的切换。

2.4 奇偶校验位计算模块

在校验节点计算模块完成所有校验节点信息后,状态机跳转奇偶校验位计算模块,此模块完成对校验节点的奇偶校验并将计算结果输出。

从上一节可以看出校验节点计算模块求出的校验信息为并行数据,并行宽度为q,因此奇偶校验位计算模块要在输出奇偶校验数据的同时完成并串转换。为实现上述操作,首先定义位宽为q+1寄存器:

Rm = {r0,r1,…,rq}

其中m = 0,1,…,359。

奇偶校验位计算模块在每q×m时钟到来时读取上一级RAM存储器中的元素ci,m并将其载入到寄存器的高位{r1,r2,…,rq}中,在其他时钟使rm做向下移位操作。

rm = {r1,r2,…,rq,0}

最终的奇偶校验结果由rm的r0和r1求出。公式如下:

pj = r0 ⊕ r1

其中,j = 1,2,…,nldpc - kldpc - 1。

2.5 FIFO缓存模块

FIFO缓存模块用于缓存输入的信息数据,对输入数据进行延迟,在奇偶校验位输出之前按顺序将缓存的信息输出输出。

2.6 编码器控制模块

编码器控制模块用于实现状态机跳转,不同码率的动态切换,给出编码器输入和输出状态标志,使LDPC编码器具有更好的通用性、兼容性。

3 FPGA实现及结果分析

本文采用的FPGA为Xilinx公司的ZYNQ系列xc7z020clg400-2,开发仿真平台为Xilinx公司的Vivado 2018.03,使用Verilog HDL硬件编程语言完成LDPC编码器的代码编写。

编码器综合后的RTL接口包含以下信号:clk用于编码器工作时钟输入,data_in用于接收信息数据进行LDPC编码,rst_n为复位信号,sink_eop为信息数据发送截止符,sink_sop为信息数据发送起始符,sink_valid为信息数据有效标志,source_ready为编码模块使能符号,type用于热切换LDPC码编码码率,data_out为编码后数据,source_eop为编码后数据截止符,source_sop为编码后数据起始符,sink_valid为编码数据有效标志位。

数据流经过编码器系统的波形图如图3所示。图4为校验节点计算模块的波形示意图。图5波形为奇偶校验位模块中寄存器rm的波形示意图,可以看出在计数器更新的同时寄存器rm中的数据也在实时更新,其他时间寄存器rm做向下移位的操作。

经验证,编码器支持码长16 200,1/2(4/9)、3/4(11/15)和7/8(8/9)三种码率的LDPC编码,同时综合后的资源占用率较低,具体如表1所示。

对代码进行时序分析,在工作频率为200 MHz的情况下,其时序报告Worst Negative Slack 0.337 ns。

可以算出芯片最高稳定工作频率为1 / (5 - 0.337) =

214.45 MHz。本文的LDPC编码器为串行编码器,所以总吞吐量为214.45 Mbit/s,当前无人机卫星通信链路带宽最大通信数据量小于8 Mbit/s,可以看出编码器的吞吐量远远高于无人机实际通信的最大带宽,可以满足无人机的通信需求。

经过本文算法的处理,通过Vivado 2018.03软件对LDPC编码器进行功率分析,芯片总功耗为0.287 W,如表2所示。如此低的功耗对于功耗供能有限的无人机卫星通信系统有重要意义。

参考DVB-S2标准中LDPC码纠错性能分析。表3给出码长16 200,码率1/2(4/9)、3/4(11/15)以及7/8(8/9)在误帧率为10-7时的信噪比门限。

无人机在正常通信的情况下接收信噪比最低为7 dB,本编码器最差的信噪比要求为6.2 dB,可以看出编码器能够满足无人机通信对纠错性能的要求。

4 结 论

本文提出的基于xc7z020clg400-2的LDPC编码器为串行编码器,总工作频率为214.45 MHz,可以支持码长16 200,码率为1/2(4/9)、3/4(11/15)以及7/8(8/9)多码率的高效编码器,纠错性能满足人机通信环境。本编码器已在无人机载卫星调制解调器中进行应用,能够满足高清音视频数据在无人机卫星通信系统高通量、低功耗、高可靠传输的应用需求。

参考文献:

[1] FR-AFNOR. Digital Video Broadcasting (DVB); Second generation framing structure, channel coding and modulation systems for Broadcasting, Interactive Services, News Gathering and other broadband satellite applications (DVB-S2):NF Z84-307-2-2020 [S/OL].[2023-01-02].https://telin.ugent.be/~./mm/Jabran/phase_noise/ETSI%2520DVB-S2.pdf.

[2] GALLAGER R G. Low Density Parity Check Codes [M].CANBRIDGE:The M.I.T. press,1963.

[3] MACKAY D J C and NEAL R M. Near Shannon limitperformance of low-density parity check codes [J].ElectronicsLetters,1996,32(18):1645-1646.

[4] 武学彬,薛永林.用于DVB-S2的LDPC编码器设计 [J].电视技术,2007(S1):114-116.

[5] 华力,雍玲,雷菁.基于FPGA的DVB-S2通用LDPC编码器设计与实现 [J].通信技术,2008(1):12-14.

[6] 范光荣,王华,夏添琦,等.基于DVB-S2的高速多码率LDPC编码器的FPGA设计与实现 [J].北京理工大学学报,2008(9):813-816+821.

[7] 闫国强,王勇,植涌,等.基于DVB-S2的通用LDPC编码器的FPGA设计 [J].电视技术,2013,37(1):1-3+7.

[8] 王延鹏,潘申富,杨宏伟.基于FPGA的DVB-S2 LDPC编码器的设计与实现 [J].无线电工程,2015,45(3):30-33.

[9] 兰亚柱,杨海钢,林郁.面向DVB-S2标准LDPC码的高效编码结构 [J].电子與信息学报,2016,38(7):1781-1787.

[10] LEE I K,KIM M H,OH D G,et al. High-speed LDPC encoder architecture for digital video broadcasting systems [C]//2013 International Conference on ICT Convergence (ICTC).Jeju:IEEE,2013:606-607.

作者简介:田宇(1990.12—),男,汉族,山西大同人,工程师,硕士,研究方向:卫星通信应用;卢志鹏(1995.01—),男,汉族,山西晋中人,工程师,硕士,研究方向:卫星通信应用。