幅度校准功能的低附加相移数控衰减器

2023-03-15李想

李 想

(中国西南电子技术研究所,四川 成都 610036)

0 引言

目前,相控阵系统被广泛应用于雷达、卫星通信以及遥测等领域。为了实现高速链路、灵活的信号覆盖和抗干扰能力的结合,需要大量高性能的相控阵发射/接收(Transmit/Receive,T/R)前端模块[1-2]。在相控阵T/R的每个单元中,幅度控制单元用于补偿单元之间的增益变化从而实现天线波束旁瓣水平(Side Lobe Level,SLL)的降低[3]。为了实现SLL 和波束零点的精确调整,需要高精度、大带宽及小步进的幅度控制电路[4]。

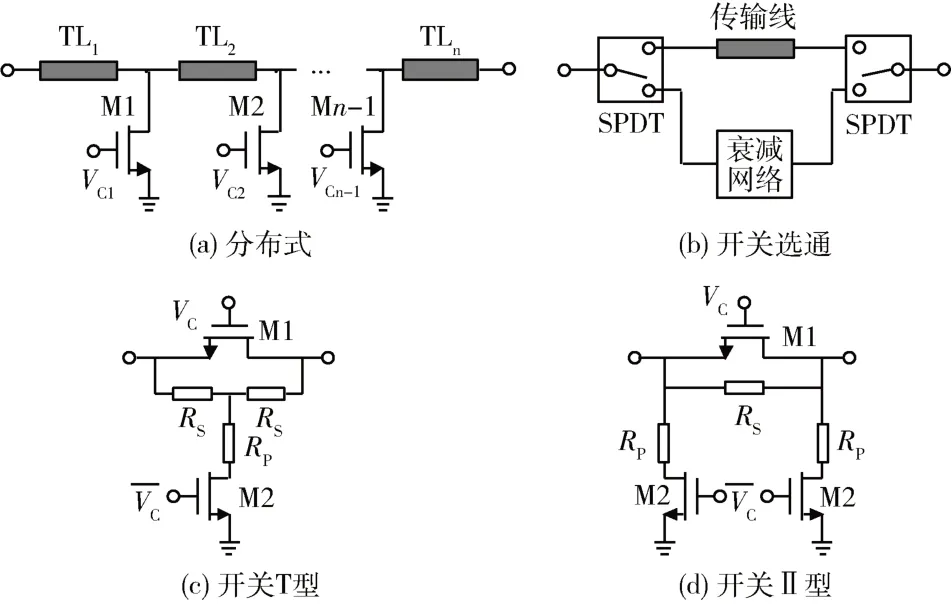

衰减器和可变增益放大器[5](Variable-Gain Amplifiers,VGA)是实现幅度控制功能的两种重要器件。相比于VGA,衰减器具有高线性度、大带宽、大衰减范围、低幅度误差/附加相移以及零功耗等优势,更适合于微波毫米波频段相控阵系统应用。图1 所示为广泛采用的几种典型衰减器拓扑结构。分布式衰减器能提供较宽的带宽和较低的插入损耗,但其占用电路面积较大且一般只能实现小于10~15 dB 的衰减范围[6-7]。开关选通式衰减器能实现较低的幅度/相位误差,但由于大量的串联开关造成损耗较大[8-9]。开关嵌入式T/Π 型衰减器具有较低的损耗、大衰减范围以及面积小等优点,满足大规模相控阵T/R 应用[10-13]。然而,开关嵌入式T/Π 型衰减器依然存在着一些技术难点:(1)多级衰减单元级联时,由于衰减单元对负载阻抗比较敏感以及工艺波动和高低温变化,造成衰减幅度精确性降低;(2)不同衰减状态时的附加相移变化较大,需特别补偿;(3)由于晶体管和电路互联布线的寄生电容影响,高频(毫米波频段)应用受到限制。

图1 典型衰减器拓扑结构

针对上述存在的技术难点,本文提出了一种具有幅度校准功能的低附加相移五位数控衰减器(Digital Controlled Attenuator,DCA)。该DCA 采用嵌入式开关T型、简化T 型和Π 型衰减结构结合幅度校准功能单元实现了高精度衰减性能,解决了不同工艺角条件下幅度误差变化问题。另外,采用相位补偿电容优化其高频衰减性能,有效降低了附加相移。

1 电路设计与分析

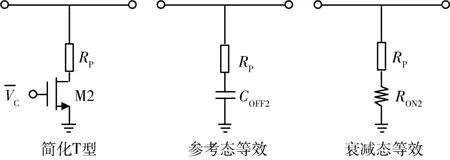

1.1 0.5 dB 和1 dB 衰减位

当衰减量较小时,T 型衰减结构中并联电阻与串联电阻的比值会达到几百比一,串联MOS 开关和串联电阻可以去掉且对端口阻抗匹配影响可忽略。因此,0.5 dB和1 dB 衰减位采用的开关简化T 型结构,如图2 所示。参考态时,MOS 管M2关断且信号到地呈现高阻状态,对应地插入损耗趋近于零。衰减态时,MOS 管M2导通,信号泄漏到地实现衰减效果。图2 同时给出了简化T 型衰减结构参考态与衰减态等效电路,其中COFF2是MOS 管关断时的等效电容,RON2是MOS 管导通电阻。选择合适的MOS 开关管尺寸后,通过调节并联电阻RP的大小即可得到所需的衰减量。

图2 简化T 型衰减结构原理图及其参考态/衰减态等效电路

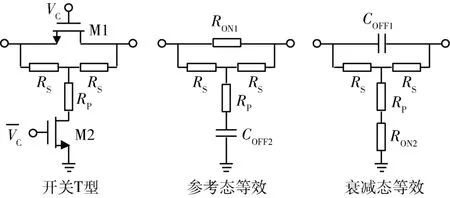

1.2 2 dB 和4 dB 衰减位

2 dB 和4 dB 衰减位采用典型开关T 型衰减结构,图3给出了其原理图以及参考态/衰减态等效电路。相比于简化T 型结构,由于串联电阻RS的存在可提供更好的阻抗匹配。参考态时,M1管导通,M2管关断,插损由M1管的导通电阻和串联电阻RS决定,对应的传输S 参数可表示为:

图3 开关T 型衰减结构原理图及其参考态/衰减态等效电路

衰减态时,M1管关断,M2管导通,信号衰减量由T型衰减网络电阻值和M2管导通电阻决定,传输S 参数可表示为:

为了实现ΔS21的相对衰减量,参考态与衰减态的S21需满足:

同时,参考态与衰减态的S11需尽量小来保证阻抗匹配。其中,M1管一般会选择比较大的尺寸(导通电阻RON1较小)来减小插损,因此参考态的阻抗匹配较好。衰减态的S11由T 型衰减网络决定并可表示为:

令S11,att-T=0,结合式(2),可得:

针对求解最佳阻抗匹配条件下的RS和RP,文献[14]给出了一套优化策略,可根据式(1)、式(3)、式(5)和式(6)求得。

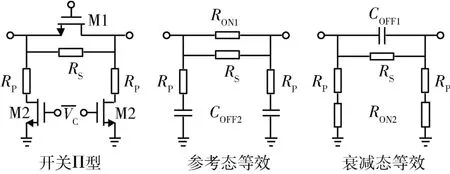

1.3 8 dB 衰减位

8 dB 衰减位采用开关Π 型衰减结构,图4 给出了其原理图以及参考态/衰减态等效电路,其在保证良好阻抗匹配条件下能实现大衰减量。参考态时,M1管导通,M2管关断,对信号提供输入到输出的低损耗路径,对应的传输S 参数如下:

衰减态时,M1管关断,M2管导通,部分信号由Π 型网络泄漏到地。对应的传输S 参数如下:

相对衰减量ΔS21需参考态与衰减态插损满足式(9),衰减态S11,att-Π(式(10))需最小化。

同样地,令S11,att-Π=0,结合式(8),可求得:

类似T 型衰减结构,可根据式(7)、式(9)、式(11)和式(12)求得最佳的Π 型衰减结构RS和RP。

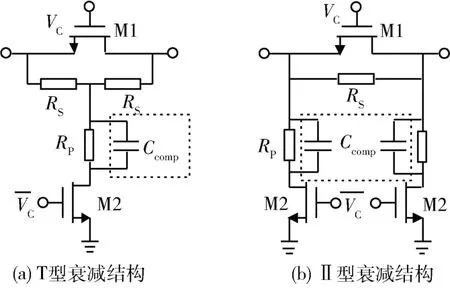

1.4 高频补偿技术

如图3 和图4 所示,受MOS 开关管的寄生电容和导通电阻的影响,T/Π 型衰减结构在参考态和衰减态对射频信号分别呈现低通和高通特性,造成高频工作时实际衰减量会偏离设计值。另外,参考态与衰减态之间存在较大的相位差。因此,本文采用在串联电阻RP上增加并联电容Ccomp的方法来对高频衰减误差和附加相移进行补偿,如图5 所示。

图4 开关Π 型衰减结构原理图及其参考态/衰减态等效电路

图5 具有附加相移补偿电容的T/Π 型衰减结构

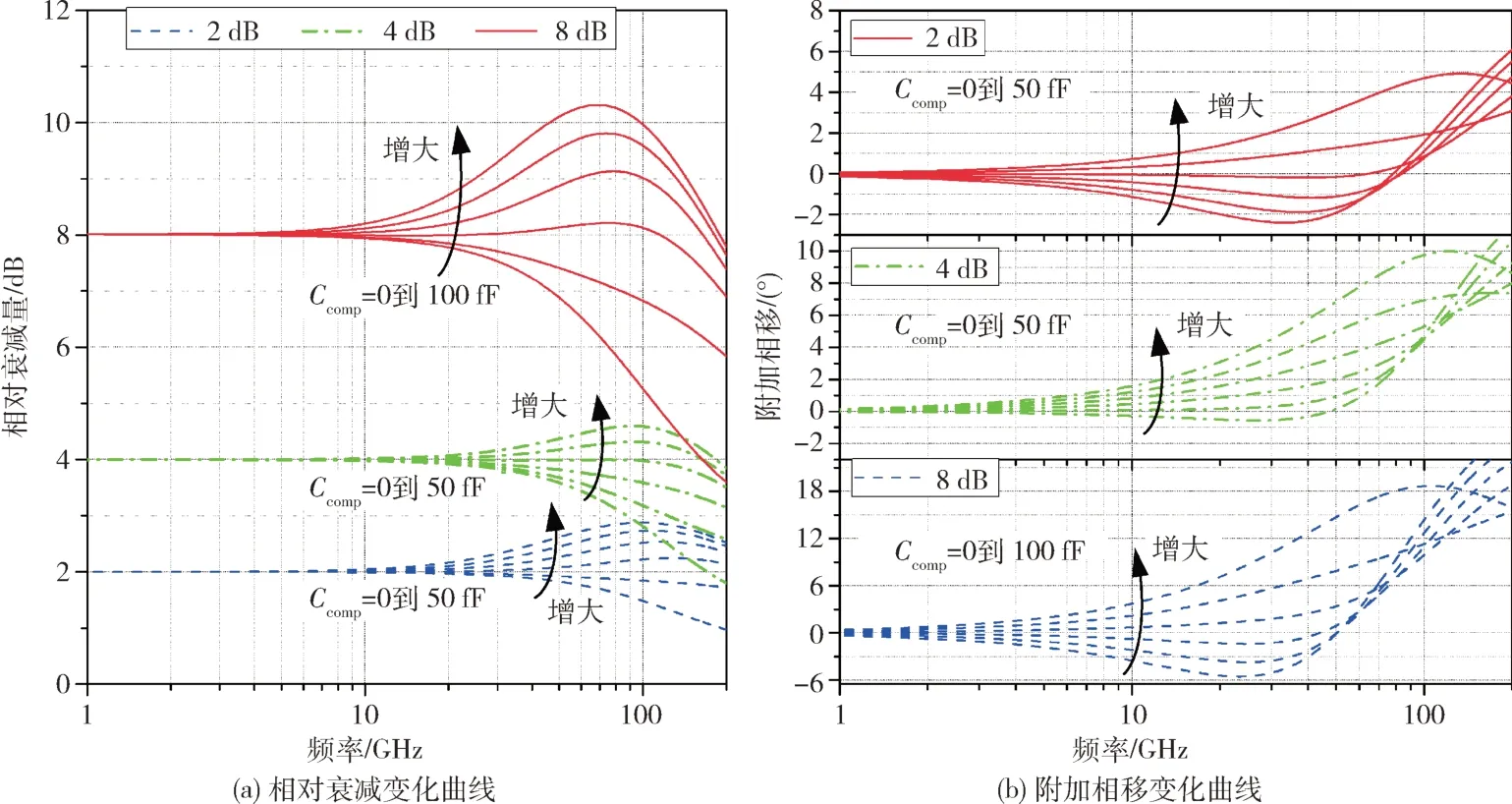

图6 是2/4/8 dB 衰减位的相对衰减量与附加相移随Ccomp增大的变化曲线。当Ccomp为零时,T/Π 型衰减结构的相对衰减量随着频率升高均变小(偏离设计值越大);当Ccomp逐渐增大,高频相对衰减量变大,如图6(a)所示。此外,由于电容补偿效果,附加相移随Ccomp的增大而从滞后向超前变化,如图6(b)所示。因此通过选择合适的Ccomp的大小可以使得高频衰减量满足设计值的同时得到较小的附加相移。

图6 2/4/8 dB 衰减单元相对衰减量与附加相移随补偿电容具有附加相移补偿电容Ccomp 变化仿真结果

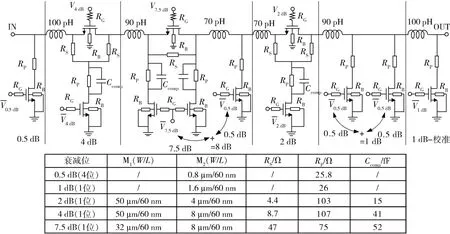

1.5 幅度校准功能的DCA

图7 所示为本文提出的具有校准功能的DCA 原理图。该DCA 采用8 个衰减位级联的方式实现5 比特衰减功能,其中增加了3 个校准位。工作频率为25~35 GHz,衰减范围为15.5 dB,步进为0.5 dB。通过仿真发现0.5/2/4 dB 三个衰减位的衰减幅度误差随工艺角变化的波动较小,而1 dB 和8 dB 衰减位幅度误差可达±0.3~±0.5 dB。因此,本文分别将1/8 dB 衰减位拆分为0.5 dB加0.5 dB 和7.5 dB 加0.5 dB,且增加1 个1 dB 校准衰减位,如图7 所示。因此,该DCA 可实现±1 dB 衰减幅度调节范围,克服工艺波动对幅度误差的影响。另外,为了增强各个衰减位之间的阻抗匹配性能,在各级之间插入了匹配电感。最终,通过版图电磁场仿真S 参数提取和电路后仿真优化确定的元件参数值如图7 所示。

图7 所提出的带幅度校准功能的DCA 原理图

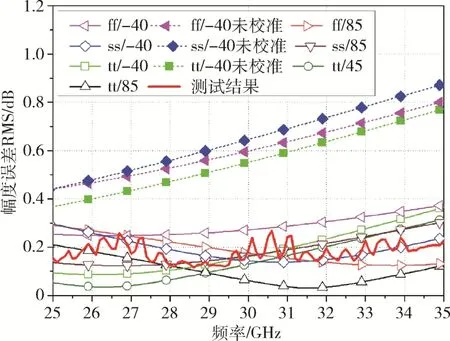

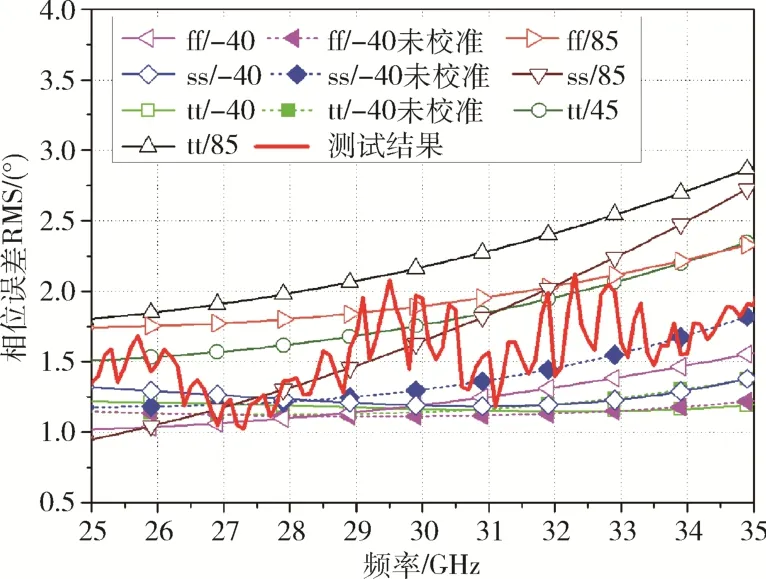

图8 和图9 给出了幅度误差RMS 和相位误差RMS在不同工艺角条件下的仿真结果。其中,在ff/-40°、ss/-40°和tt/-40°条件下幅度误差RMS 较大,在25~35 GHz频率范围内最大可达0.88 dB。通过3 个校准位的组合实现对幅度误差较大的衰减态校准,可使得在所有工艺角条件下的幅度误差RMS 在整个工作频带下降到0.37 dB以下。另外,从图9 可以看出,在所有工艺角条件下相位误差RMS 均比较好(最大值为tt/85°条件下的2.88°),且进行幅度校准时对相位误差的影响很小,最大值出现在tt/85°。因此本文所提出的衰减器未对附加相移进行校准功能设计。

图8 衰减幅度误差RMS 仿真与测试结果

图9 相位误差RMS 仿真与测试结果

2 测试结果与分析

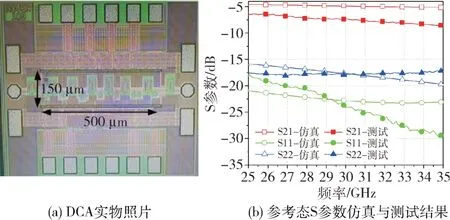

本文基于65 nm CMOS 工艺,对所提出的幅度校准功能的DCA 进行了流片与测试验证,实物照片如图10(a)所示,芯片核心部分尺寸为500 µm×150 µm。芯片通过探针进行片上测试。参考态的S 参数测试与仿真结果如图10(b)所示,可以看出测试与仿真结果吻合较好。其中,插入损耗测试结果在25~35 GHz 频率范围内为6.54~8.6 dB,高于仿真值2~3.4 dB。主要原因是设计仿真提取的寄生参数精度有限以及级间匹配电感电磁场仿真提取的品质因素高于实际值,且随着频率升高误差增大。

图10 DCA 实物照片及参考态S 参数仿真与测试结果

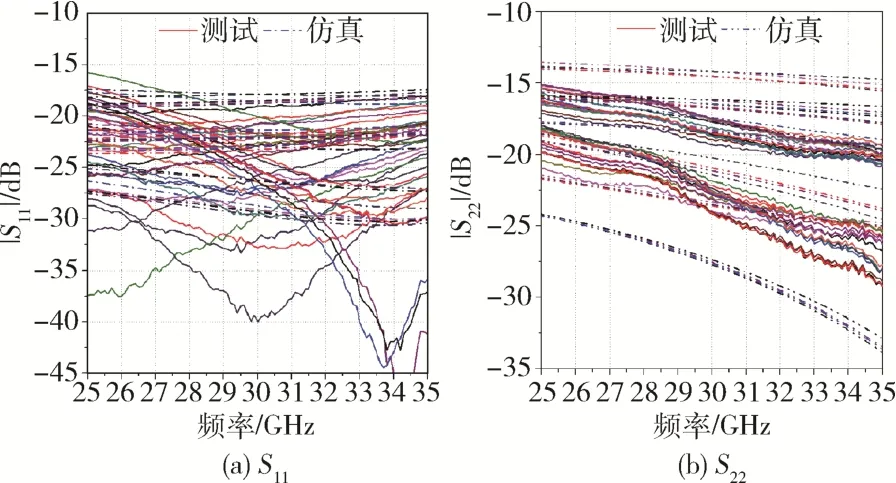

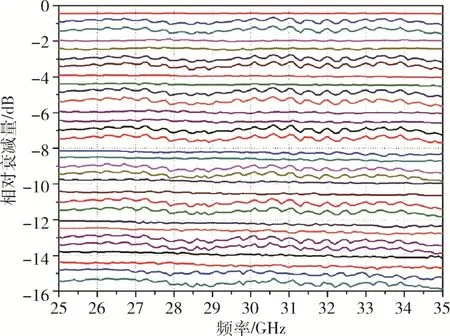

32 个衰减态的回波损耗S11和S22测试与仿真结果如图11 所示,实测结果表明25~35 GHz 频率范围内均小于-15 dB。说明该DCA 在整个工作频带内输入/输出阻抗匹配性能良好。图12 给出了32 个衰减态的相对衰减量测试结果,表明本文提出的DCA 实现了15.5 dB 最大衰减和0.5 dB 步进幅度控制功能。

图11 32 个衰减态测试与仿真结果

图12 32 个衰减态的相对衰减量测试结果

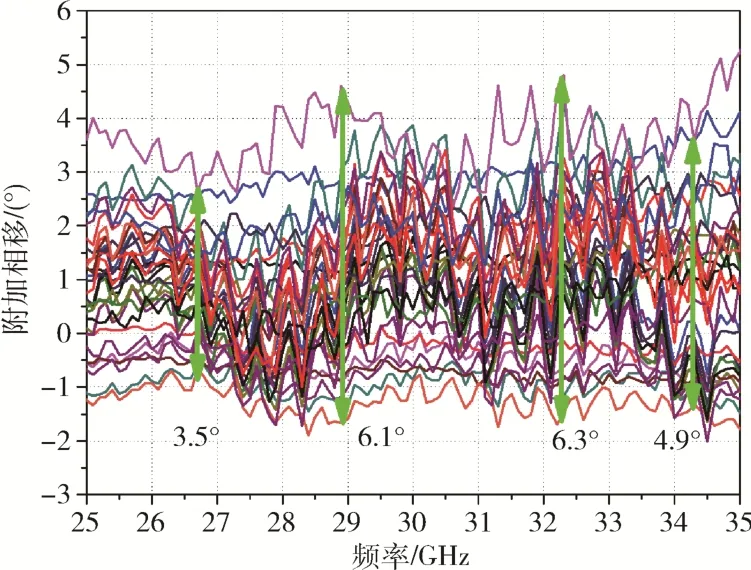

图13 所示为32 个衰减态的附加相移测试结果,可以看出附加相移变化在3.5°~6.3°范围内。幅度误差RMS 和相位误差RMS 测试结果如图8 和图9 所示。测试过程中,对部分衰减态进行了幅度误差校准。实测结果表明:幅度误差RMS 为0.12~0.26 dB,相位误差为1.02°~2.07°,实现了高衰减精度和低附加相移特性。此外,当频率范围限定在27.5~30 GHz 时,可得到最好的幅度误差RMS(0.12~0.18 dB)性能。

图13 32 个衰减态的附加相移测试结果

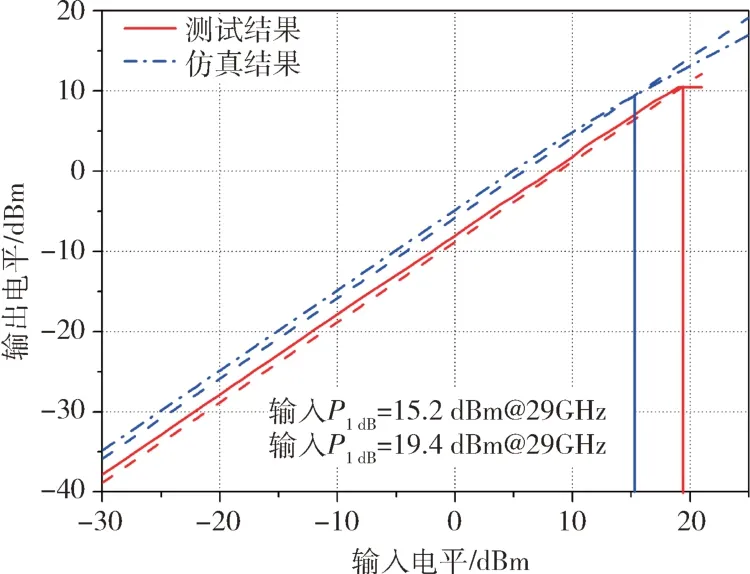

参考态时的输入P1dB测试与仿真结果如图14 所示,仿真结果低于测试结果的主要原因是插入损耗测试结果偏大。在29 GHz 频点的输入P1dB实测结果为19.4 dB,说明该DCA 具有足够高的功率性能,不会成为限制相控阵系统线性度的因素。

图14 输入P1dB 仿真与测试结果

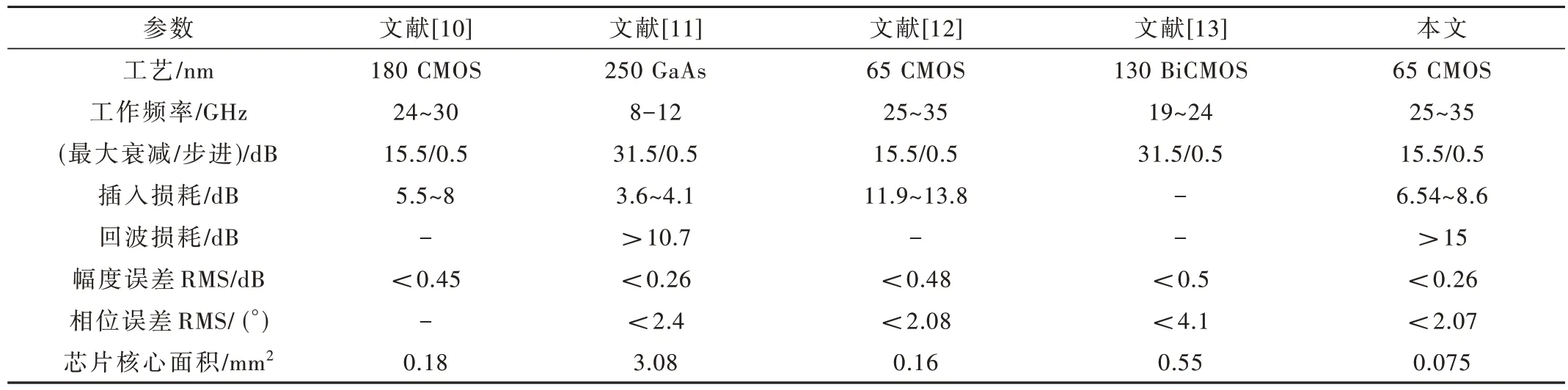

表1 所示是本文与相关文献中DCA 的性能对比。所提出的DCA 由于幅度校准功能的引入具有较小的幅度误差RMS,并且相位误差RMS 同样较小。综合来看,该DCA 在插入损耗、回波损耗以及芯片面积方面均呈现比较优越的性能。

表1 本文与其他文献中DCA 的性能对比

3 结论

本文基于65 nm CMOS 工艺,提出了一种具有幅度校准功能的低附加相移DCA。首先,针对不同工艺角条件下衰减误差变化大的衰减位引入校准位设计,有效降低了幅度误差RMS,增强了电路设计的鲁棒性。其次,通过在T/Π 型衰减结构中采用电容补偿技术提高了DCA 的高频性能,实现了低附加相移。最终,实测结果表明在25~35 GHz 频带范围内,该DCA 具有较小的幅度误差RMS 和相位误差RMS 性能,分别为0.12~0.26 dB 和1.02°~2.07°。另外,芯片核心尺寸仅为0.075 mm2。因此,该DCA 非常适合用于Ka 波段相控阵系统。