多态性PCIE 桥扩展芯片的设计和硅后验证

2023-03-15邓佳伟张梅娟张明月杨楚玮

邓佳伟,王 琪,张梅娟,张明月,杨楚玮

(中国电子科技集团公司第五十八研究所,江苏 无锡 214060)

0 引言

PCIE 是一种高速串行计算机扩展总线标准,由Intel在2001 年提出,旨在替换老旧的PCI、PCI-X 的总线标准。

PCIE 属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不贡献总线带宽,主要支持主动电源管理、错误报告、端对端的可靠性传输、热插拔等功能。PCIE 有多种规格,从PCIE x1 到x32。

芯片流片完成后,硅后系统测试开始,验证人员依照系统集成的顺序从底层单元开始测试。验证前,需将芯片测试开发板结合起来,或将芯片驱动程序编程到开发系统。随后和设计人员和验证人员沟通。一旦验证出现问题,需要验证人员评判缺陷情况,从软件层面给出是否有可行补救方案。如果芯片存在最终无法避免的缺陷,该缺陷严重影响芯片功能,就需要在下个芯片周期中去修复该问题[1]。

多态性指的是多种表现形态,指同一事物通过不同的执行方式实现了不同内容的行为。换言之,同一个芯片通过不同的执行流程,最后形成了不同的芯片功能。

1 PCIE 总线架构

1.1 PCIE 总线拓扑

PCIE 总线系统存在着多种种类的设备,有根聚合体RC(Root Complex),PCIE 转换桥SWITCH,端节点EP(Endpoint)。这几种设备组成了完整的PCIE 拓扑结构[2]。

RC 的作用:处理器连接到RC,RC 负责完成CPU 的内部地址域到PCIE 内部的总线域之间的转换,同时实现了各种总线的数据汇合。实现了从CPU 地址总线域到PCIE 域地址、PCIE 域到CPU 地址总线域的双向映射。RC 同时具备以下属性:

(1) RC 是I/O 层次结构的根节点,连接CPU 的Memory 内存子系统到I/O 子系统,实际为PCIE 总线结构中的主桥;

(2) 一个RC 可以支持多个PCIE 端口,每个端口有独立的I/O(In/Out)层次结构域,独立的I/O 层次结构域下连接一个单独的EP,或者连接一个SWITCH 组件,SWITCH 下连接一个以上的EP;

(3) I/O 层次结构域通过RC 进行点对点(Peer to Peer)的对等网络传输功能是可选的;

(4) RC 作为事务请求者时,支持的包类型有配置请求(configuration request)、IO 请求(I/O request)和锁定请求(locked request)。

SWITCH 的作用:SWITCH 的内部由多个PCIE-to-PCIE 虚拟桥设备组成,用于扩展PCIE 的总线端口,实现多设备互连,内部逻辑实现了数据路由寻址转发、仲裁等功能。SWITCH 具备以下属性:

(1) SWITCH 转接桥由两个以上的PCI-to-PCI 虚拟桥组成;

(2) SWITCH 桥使用PCI 桥的数据传输机制实现了数据传递,其中最常用的基于地址的路由机制实现;

(3) SWITCH 桥必须支持在任何的端口之间传输任意类型的TLP(Transaction Layer Packet)数据包;

(4) SWITCH 桥上游端口作为发起方需要支持Locked Request 请求,下游端口作为发起方时发起的Locked Request 不需要支持;

(5) 使能的SWITCH 桥端口需要遵循流控协议;

(6) SWITCH 桥不可将TLP 类型的数据包分割成多个小数据包进行数据传输。

EP 的作用:EP 是PCIE 体系中总线拓扑结构的根节点,担任的角色为传输的请求方或者结束方。EP 是指该PCIE 设备只具有上游端口的一种PCIE 设备。

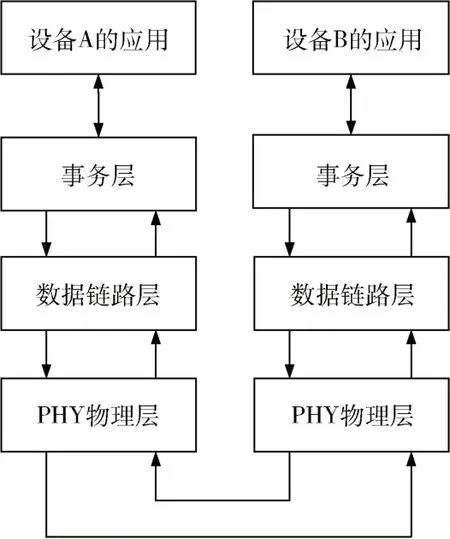

1.2 PCIE 协议层次结构

PCIE 规范对设备的协议为分层结构,如图1 所示,具体由事务层、数据链路层和物理层组成。每层都有发送和接收功能[3-4]。

图1 PCIE 协议层次结构

发送端:发送端的应用程序在事务层组成事务层数据包TLP(Transaction Layer Package),在发送缓存中向下层发送。在数据链路层,在TLP 数据包中加附加信息,信息是对方接收到TLP 数据包时错误检查时需要的,其数据链路层数据包DLLP(Data Link Layer Package);在物理层,对DLLP 数据包数据编码,通过链路中的可用通道,从发送器发送出去[5]。

接收端:实际为发送端的反过程。接收端实际就是把发送端组合的数据包反向拆包,最后提取有用的数据信息给接收端设备的应用程序使用[6]。

2 芯片设计架构

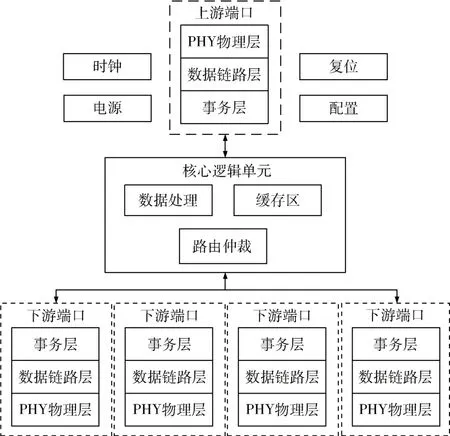

2.1 芯片整体设计

本芯片的主要逻辑包括桥芯片核心逻辑单元、上下游端口、配置逻辑单元、时钟单元、复位单元、电源管理单元等,如图2 所示。

图2 整体方案设计图

(1)核心逻辑单元

核心逻辑单元包括数据处理、路由仲裁和缓存区子单元。其中数据处理子单元负责桥芯片核心数据处理逻辑,包括数据报文处理功能;路由仲裁子单元负责对每个传输数据包进行仲裁处理;数据处理完成后,按照数据包的目标地址,将数据包传送到指定的地址,进行路由;缓存区子单元负责将数据缓存[7-9]。

(2)上下游端口单元

芯片上游端口有1 个,下游端口支持4 个,每个端口有PHY(Port Physical Layer)物理层、数据链路层、事务层,通过端口将数据接收和发送给上下游[10]。

(3)配置逻辑单元

芯片通过SPI 配置接口,连接外部EEPROM。配置逻辑单元负责通过读取外部EEPROM,再解析EEPROM中的配置数据,最后通过配置数据重配置芯片,芯片根据不同的配置属性具备了更多的形态。芯片具备了多态性配置接口[11-13]。

(4)时钟单元

芯片上的时钟单元主要负责提供时钟信号给芯片上的各逻辑单元,桥芯片外部时钟输入有两个,一个是从金手指上获取的100~125 MHz 时钟信号,还有一个是外部晶振提供的25 MHz 时钟信号,芯片的时钟单元接收到外部信号后,通过时钟单元将时钟分频倍频,最后提供给每个逻辑单元[14]。

(5)复位单元

复位单元提供给芯片复位信号,芯片接收到复位信号后,重新启动芯片的逻辑,和各芯片子单元。

(6)电源单元

电源单元提供给芯片内部各逻辑子单元电源信号。

2.2 关键逻辑单元设计

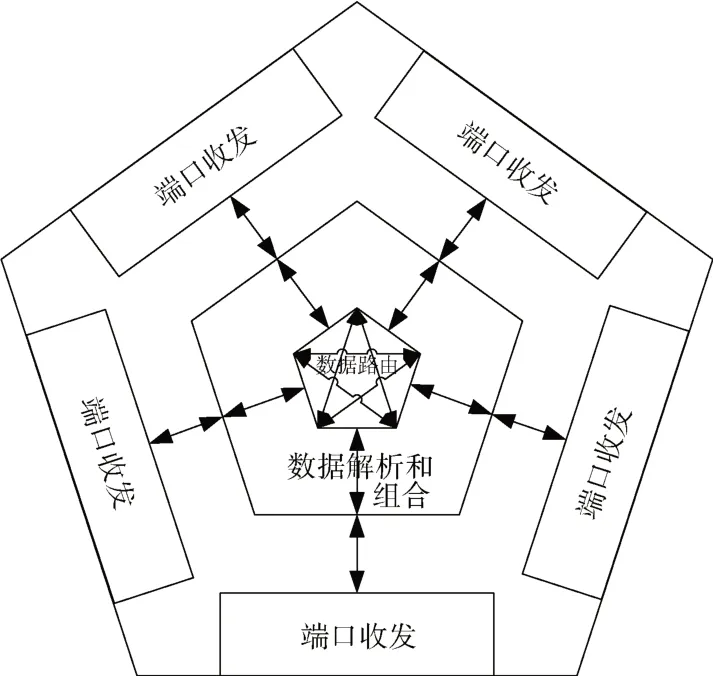

2.2.1 核心逻辑模块设计

桥芯片核心结构主要完成了输入报文的头部解析和路由,输出报文的数据端口仲裁。

核心逻辑模块设计如图3 所示。当数据从一个端口发送来数据后,端口接收单元接收数据,放到对应端口的数据缓存中,缓存数据调用数据解析和组合单元,同时将数据的相关信息提取起来,对数据进行仲裁,核心逻辑按照路由信息,将数据路由到对端端口上,通过数据解析和组合单元,将数据重新组合成数据包,发送到对端的端口收发单元,将数据发送出去[15]。

图3 核心逻辑模块设计

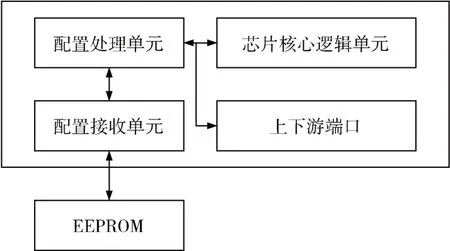

2.2.2 多态性配置单元设计

PCIE 桥芯片通过配置接收单元的SPI 接口连接外部EEPROM 存储。在EEPROM 可以按照约定的格式保存每个端口的配置信息。桥芯片上电过程中,读取EEPROM 是否为空,不为空时开始配置。配置处理单元将数据解析后,分发给芯片核心逻辑单元和上下游端口。图4 为配置单元设计图[16-17]。

图4 配置单元设计

电路上电后,芯片初始化加载其步骤可总结如下:

(1)芯片上的配置单元为在芯片加载过程中通过指令逐个命令访问EEPROM 中的配置信息;

(2)读取 EEPROM 返回的配置信息后,将数据进行解析;

(3)将相应的配置信息反馈给芯片中寄存器;

(4)寄存器操作相关逻辑单元,逻辑单元进行处理;

(5)处理完毕后,整个配置过程结束。

3 具体验证方案设计及其实现

3.1 验证方案介绍

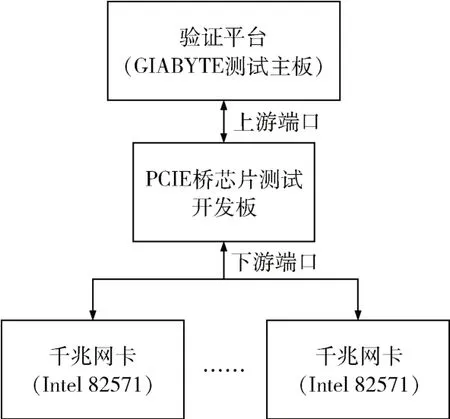

验证平台由通用Intel 处理器平台(GIGABYTE 测试主板)、PCIE 桥芯片测试开发板、Intel 公司的82571 千兆网卡组成。通过Linux 操作系统(CentOS7.0)和Linux 网络测试工具iPerf 验证芯片功能。图5 为验证平台的整体方案设计。

图5 验证平台的整体方案

3.2 验证方案具体电路设计

3.2.1 PCIE 桥芯片测试开发板整体电路设计

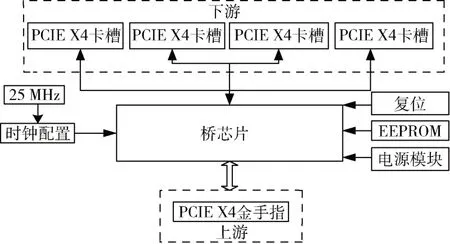

测试板卡主要包括以下几个部分:芯片时钟激励、外部EEPROM、复位按键、电源芯片、PCIE 卡槽和桥芯片,图6 为测试开发板整体设计图。

图6 验证板卡电路整体设计

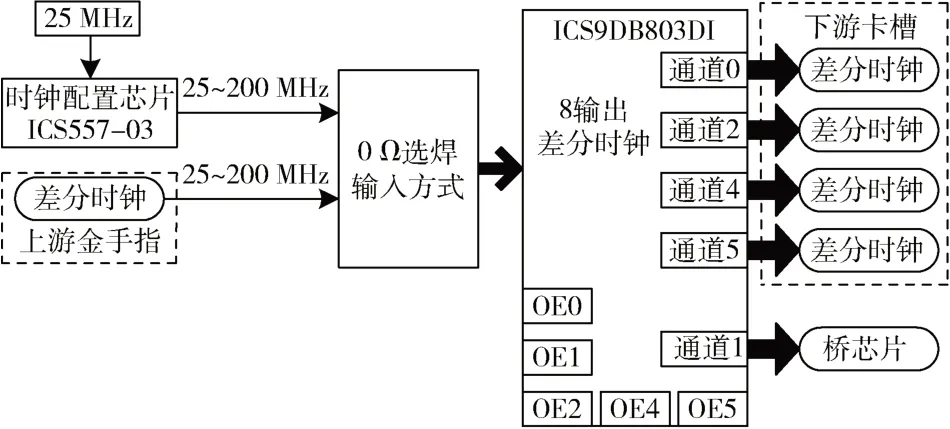

3.2.2 PCIE 桥芯片时钟电路设计

开发板时钟电路分为两个激励源,可以通过0 Ω 电阻选焊方式确定输入方式,当通过晶振输入时,频率选择为25 MHz,板卡可以通过金手指上从验证平台上直接输入100 MHz 时钟信号。输入到时钟配置单元后,其主要提供给桥芯片的逻辑。图7 为具体电路设计。

图7 时钟电路设计

3.2.3 PCIE 桥芯片电源电路设计

电源电路设计中通过电源芯片提供不同的电压给芯片内部不同的电压。电源模块电路设计如图8 所示。

图8 电源模块电路设计

3.3 验证方案软件设计

3.3.1 PCIE 设备枚举

Linux 系统会在系统上电过程中枚举PCIE 所有总线下设备。通过主桥依次向下枚举,同时配置PCIE 设备的配置空间。Linux 内核中枚举的关键步骤可总结如下[18-19]:

(1)内核创建主桥(host bridge)的数据结构,将其注册到系统,注册的过程中创建一个根总线bus0,将其挂载到主桥下,然后解析设备树,为总线分配资源和地址空间。

(2)函数pci_scan_child_bus 开始,扫描总线下所有的设备和桥。

(3)函数 pci_scan_child_bus_extend 分为两部分:扫描PCIE 设备,每条总线下可分配32 个设备,每个设备可最多8 个功能,若配置空间版本号和设备号不为0xff,创建PCI_DEV 设备,填充PCIE 设备信息到数据结构中,再设置PCIE 设备的BAR(Base Address)地址寄存器,将设备树读到的IO 空间分配给PCIE 设备,再将设备注册到总线。扫描PCIE 桥设备,当发现下一级桥设备时,继续创建总线,扫描该下一级总线下的设备,进行枚举,通过DFS 枚举(Depth First Search)深度遍历算法,最终枚举出所有设备。

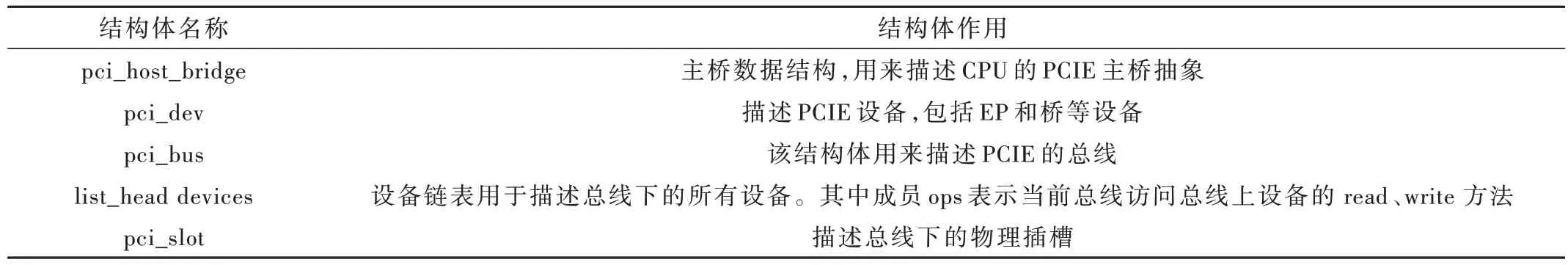

3.3.2 关键结构体

PCIE 设备在Linux 枚举过程中涉及的主要结构体如表1 所示。

表1 关键结构体

4 硅后验证结果及其分析

4.1 测试现场图

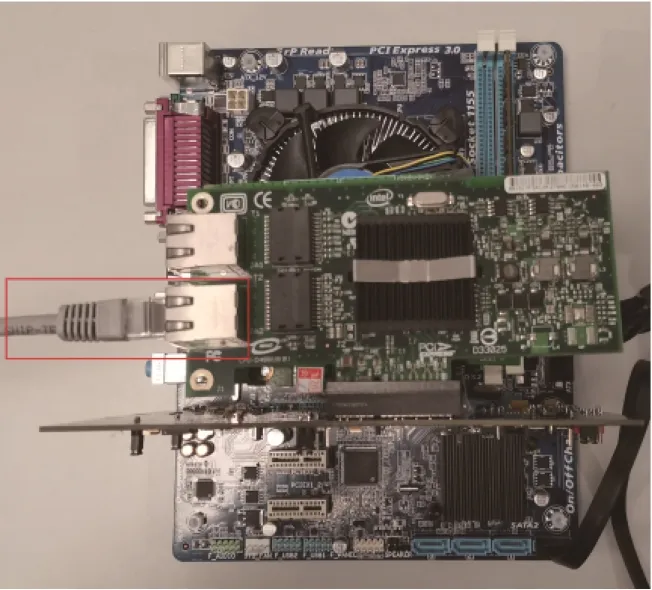

图9 显示了测试现场图,图中左侧的是验证平台,其通用Intel 处理器平台(GIGABYTE 测试主板)。右侧的为PCIE 桥芯片测试开发板。图中矩形框处,以太网线连接一台主机PC。

图9 测试现场图

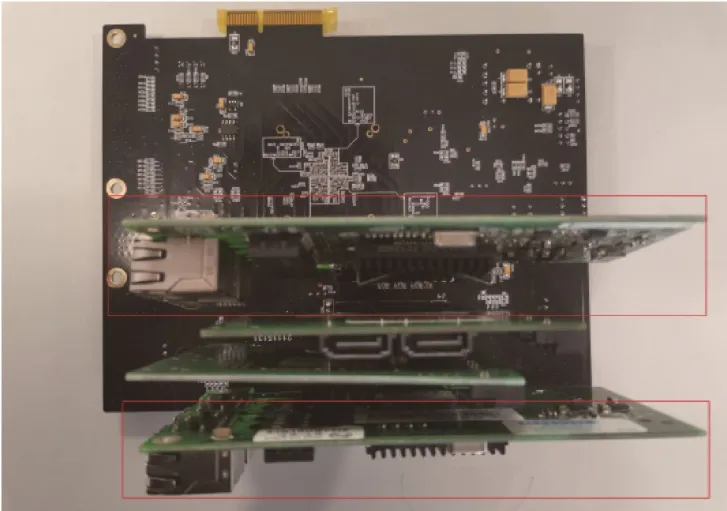

图10 为PCIE 桥芯片测试开发板和Intel 公司的千兆网卡组成测试子卡。图中有多种不同PCIE 板卡,矩形框内为千兆网卡。

图10 板卡实物图

4.2 测试结果图

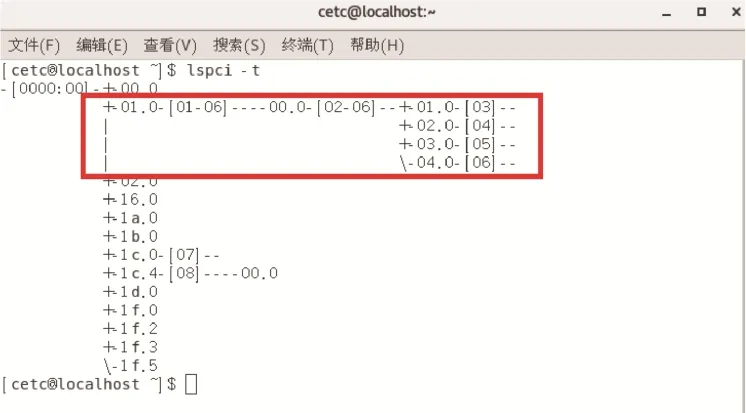

图11 为验证平台上正常枚举所有桥端口的测试图。从图中可以看出4 个下游端口。

图11 下游4 端口图

图12 为通过EEPROM 重新配置芯片,当上电后,Linux 系统枚举得到的下游端口,在EEPROM 中关闭了两路PCIE 通道。

图12 下游2 端口图

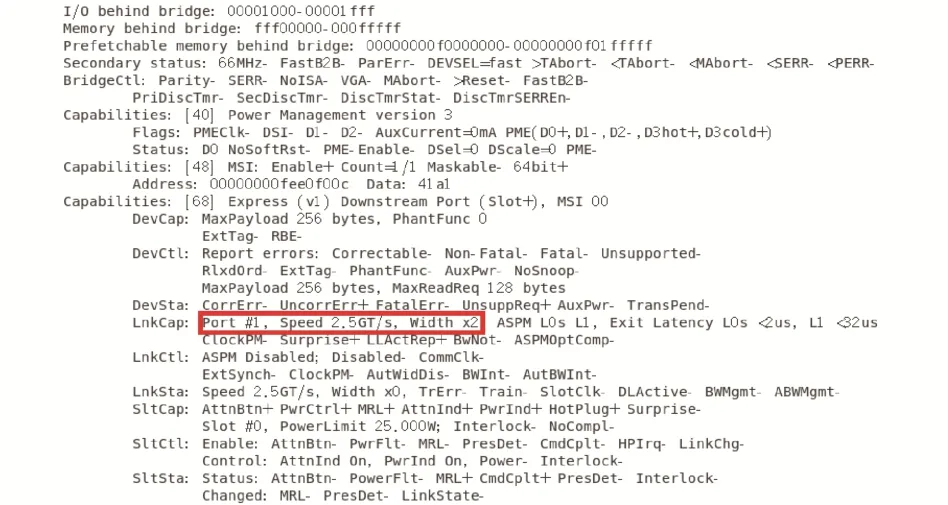

图13 为通过EERPOM 重新配置芯片,当上电后,Linux 系统枚举后,查看下游PCIE 速率能力,其已下降到PCIE1.0,速率为2.5 Gb/s。

图13 EEROM 重新配置链路状态图

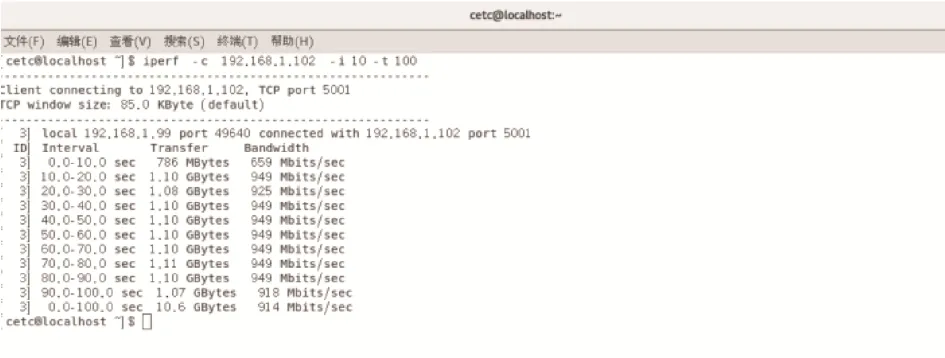

图14 为通过iPerf 测试,可以看到通过INTEL 82571,网络数据通过PCIE 桥后,数据可以通信,且速率可以到达千兆网卡的峰值。

图14 网络压力测试PCIE 性能图

5 结论

随着PCIE 类型的外围设备种类越来越多,传统的处理器在扩展高速接口的能力上已经捉襟见肘。具备多态性的PCIE 扩展桥应运而生。

本芯片设计出一款多通路、高通量的四通道PCIE 扩展桥,同时芯片内部的配置逻辑单元实现了芯片的多态性,使芯片具备了不同的属性适应不同的应用。芯片有效弥补了传统处理器能力不足的缺点,同时也为下一步设计更多通道的PCIE 扩展芯片提供了技术支撑。