一种像增强器阴极高重频选通电路的设计

2022-12-06宋海浩倪小兵李梦依刘佳音任莹楠张琳琳

宋海浩,延 波,倪小兵,智 强,李梦依,刘佳音,任莹楠,司 可,张琳琳

(1. 微光夜视技术重点实验室,陕西 西安 710065;2. 昆明物理研究所,云南 昆明 650223)

引言

激光/微光距离选通成像是目前水下探测、恶劣天气下目标探测、遥感探测中较为有效的途径[1-4]。像增强器是实现激光/微光距离选通成像的关键部件之一。一般地,激光/微光距离选通成像系统中的同步触发信号为低电压信号[5],而对于像增强器,为保证其阴极能够正常工作通常需要上百伏特的高压来驱动。这就需要采用阴极选通电路作为中间部件,根据激光器的同步触发信号对像增强器阴极进行控制,实现距离选通门的功能[6-7]。因此,阴极选通电路的开关速度将直接影响像增强器阴极的开启速度,进而影响距离选通成像系统的性能[8]。

目前产生脉冲的主流方法主要有2 种:一种方法是采用模拟器件特性产生脉冲[9-10],利用诸如隧道二极管,阶跃恢复二极管,雪崩晶体管等半导体特性设计脉冲产生电路,此类电路结构相对简单,但存在脉冲宽度等参数不易调节或调节范围有限等缺点[11-12];另一种方法是采用数字逻辑门电路的组合实现窄脉冲,可根据设计需要,灵活组合高速的逻辑门电路单元,产生窄脉冲,这种电路的脉冲参数可以根据需要来配置外围电路参数,缺点是门逻辑电路结构相对较为复杂,并且产生信号幅度较小,需要后级电路进行放大。

本文以数字逻辑门脉冲电路为思路,提出了一种利用高速门电路的逻辑组合提升阴极开启/关闭速度的阴极高重频选通电路。输出级以金属氧化物半导体场效应晶体管(MOSFET)推挽电路为基础,采取分阶段、分级驱动的策略,利用高速逻辑门、触发器搭建逻辑输出,控制中间级驱动电路产生3 路阶段性驱动信号,提高输出级驱动电路导通/关闭速度,达到加速像增强器阴极开关速度的目的。

1 像增强器阴极选通信号需求分析

1.1 脉冲电压需求分析

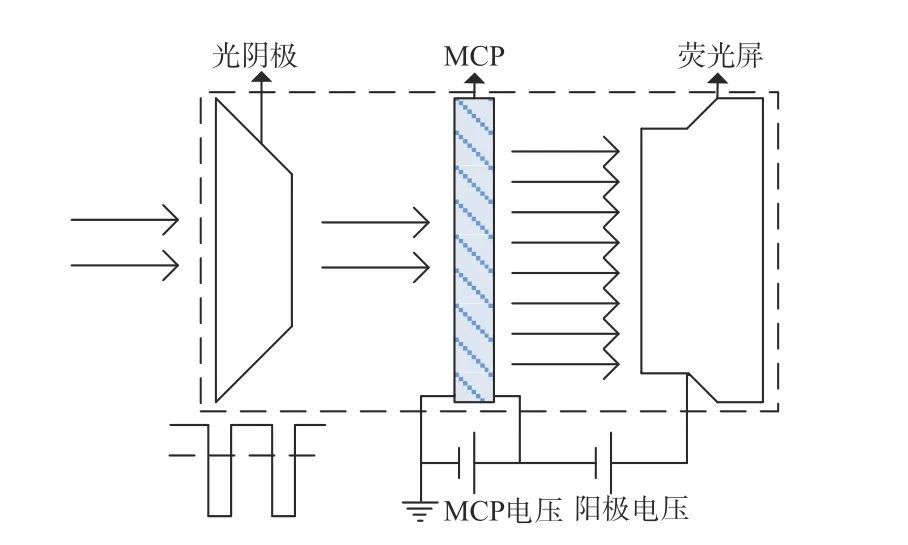

像增强器在选通成像系统中主要起到2 个作用:1) 光增强 利用光电转换,光电倍增将微弱的光信号放大成千上万倍;2) 光快门 利用真空光电子易于被电子透镜偏转、聚焦和加速的特点,实现对瞬态过程的记录[13]。像增强器结构如图1 所示,包括光电阴极、微通道板(MCP)和荧光屏。阴极选通电路输出信号主要作用于像增强器的光电阴极,控制像增强器工作在开启与关闭2 种模式下,与高速成像系统的快门功能相似。

图1 像增强器结构Fig. 1 Structure diagram of image intensifier

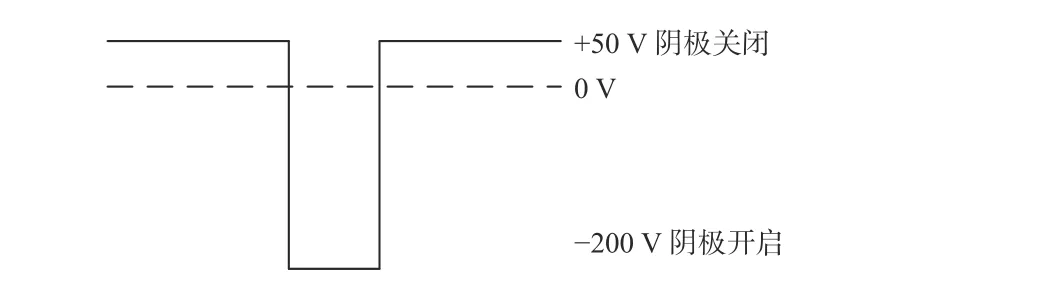

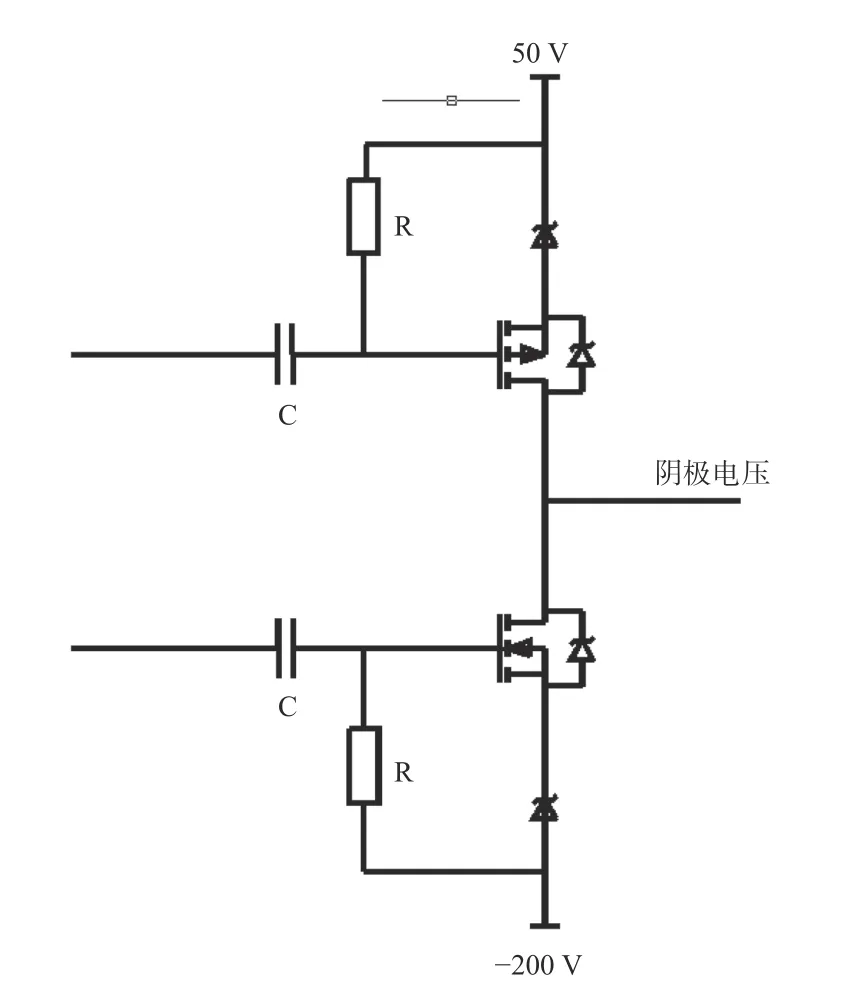

对于二代/超二代像增强器,其最佳工作状态时光电阴极与微通道板输入端的电压需要达到−200 V,光电阴极光电转换发射出的电子受到电场力的作用,到达微通道板并产生光电倍增效应,像增强器开始工作。当像增强器的光电阴极与微通道板输入端为正压时,微通道板的电子被电场力束缚,无法向后发射,像增强器处于停止工作的状态。为使像增强器阴极快速阻断电子的移动,本文采用+50 V 作为像增强器阴极的关闭电压。上述分析可知,像增强器阴极选通信号为−200 V 到+50 V 的脉冲信号,如图2 所示。

图2 阴极选通信号需求Fig. 2 Demand diagram for cathode gating signal

1.2 脉冲时间需求分析

根据激光/微光距离选通成像系统输出信号关系:

其中:PM为 激光脉冲 功 率(W); τ为激光 脉 冲 宽度(s);f为激光/探测器重复频率(Hz);S为探测器(像增强器光电阴极)灵敏度(A/W);G为系统增益。由(1) 式可知,激光/探测器重复频率越高,其他条件不变的情况下,选通成像系统的信号输出越强。选通成像系统距离判定最小误差为

其中:c为激光在水中的传播速度; τ为脉冲宽度。即脉冲宽度越窄,选通成像系统的测距误差越小。

综合上述分析,阴极选通信号的重复频率应与激光脉冲信号一致,最小脉冲宽度尽可能窄,边沿时间尽可能短,通常为ns 级[14]。

2 分阶段加速原理

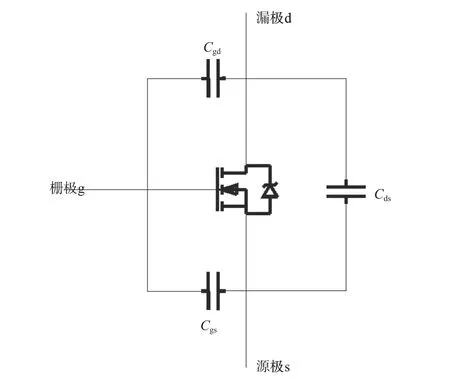

为了让阴极选通电路正负电压尽可能满幅值地输出,输出级驱动采用MOSFET 推挽结构的电路。MOSFET 因制造工艺的原因存在极间寄生电容[15]。通常将MOSFET 等效为如图3 所示的电路模型,这些寄生电容是主导MOSFET 开关动作的主导因素。MOSFET 生产厂商通常提供的参数是输入电容Ciss, 输出电容Coss和反馈电容Crss,与极间电容的关系为

图3 MOSFET 等效电路Fig. 3 Equivalent circuit diagram of MOSFET

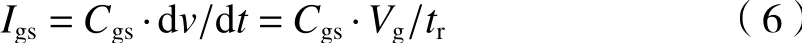

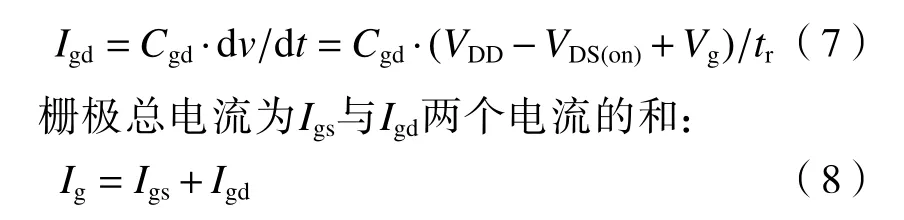

MOSFET 在开启时,栅极开始向电容Cgs充电,栅源电压逐步超过阈值电压,MOSFET 进入导通状态。假设,栅极上升电压为Vg,上升所用时间为tr,此时,栅极所需要的驱动电流为

由于Cgd的存在,栅漏电容在MOSFET 导通时快速放电,栅极电流逐渐发生转移,源漏电容Cgd的上端电压下降了VDD−VDS(on), 其下端电压上升了Vg,此时所需的电流为

由于Igd对 栅极电流的分流,使得栅源电容Cgs的电压上升变缓,产生米勒效应,这时漏极电压开始变化。一旦漏极电压完成转换,Cgd不再有电流流过,至此MOSFET 完全开启。同样,MOSFET 关闭时,Cgs通 过外部驱动电路放电,Cgd通过上升的漏极电压与栅极允许的电流进行充电。充电结束后,栅极电压继续下降到阈值电压以下,MOSFET完全关闭。正是由于栅漏电容Cgd的充放电过程延缓了栅源间电容Cgs的变化,使得MOSFET 的通断速度变慢。

针对MOSFET 的开关特性,采取阶段加速的策略,将整个驱动过程分为3 个阶段:加速开启阶段,信号保持阶段,加速关断阶段。加速开启阶段采用较高幅值的脉冲驱动,利用瞬时快边沿的脉冲给栅极电容快速充电,让MOSFET 的导通时间降低。但是瞬时的脉冲信号过后无法持续保持栅极电容的电荷。在加速开启阶段结束后,栅极电荷会缓慢放电,从而影响源漏之间的阻抗,使得输出无法保持。本文在信号保持阶段采用与触发信号相同逻辑的信号让MOSFET 持续导通,保持输出信号的幅度不变。在MOSFET 对管交替的阶段,预关MOSFET 采取加速关断的策略,使栅极电位迅速拉回到之前的状态,经过一个死区时间后,预开MOSFET 加速导通,继续按照以上的加速策略进行MOSFET 的交替导通。为保证上升边沿时间与下降边沿时间尽可能相近,最后一级输出采用一对参数相匹配的MOSFET 对管,栅极采用电容耦合,MOSFET 源极串联一个稳压二极管,有利于MOSFET 尽快进入导通状态,如图4 所示。

图4 输出级驱动电路Fig. 4 Diagram of output-stage drive circuit

3 驱动逻辑电路设计

3.1 时间偏置电路单元

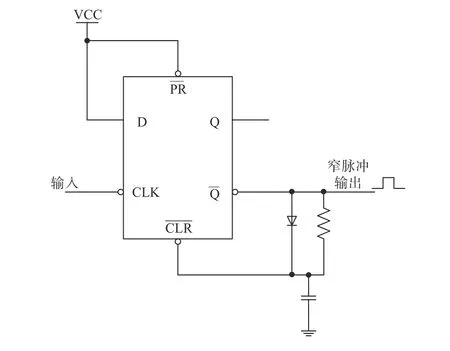

为实现MOSFET 多信号的逻辑顺序控制,设计使用如图5 所示的时间偏置电路单元。利用高速D 触发器自身的触发延时与一个一阶RC 电路延时,获得窄脉冲输出。

图5 D 触发器时间偏置电路单元原理图Fig. 5 Schematic diagram of time bias circuit unit of D flipflop

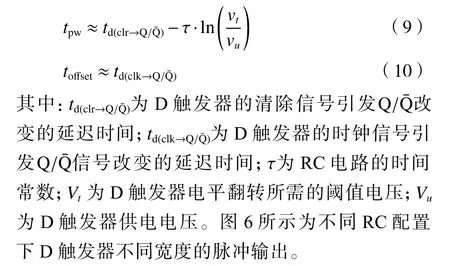

窄脉冲宽度与偏置时间可按公式(9)、(10)进行计算:

图6 D 触发器时间偏置电路单元仿真Fig. 6 Simulation of time bias circuit unit of D flip-flop

利用多级D 触发器时间偏置电路输出、时钟引脚级联,将前一级D 触发器的输出边沿作为下一级D 触发器触发边沿,可通过配置前一级外围RC 充放电路的时间 τ来调整窄脉冲宽度,即改变窄脉冲后边沿的触发时间来调控后一级的偏置时间,最终得到ns 级的时间偏置控制。如图7 所示,为2 级D 触发器时间偏置电路级联后的偏置输出。

图7 D 触发器时间偏置电路2 级级联偏置仿真Fig. 7 Simulation diagram of two-stage cascaded bias of D flip-flop time bias circuit

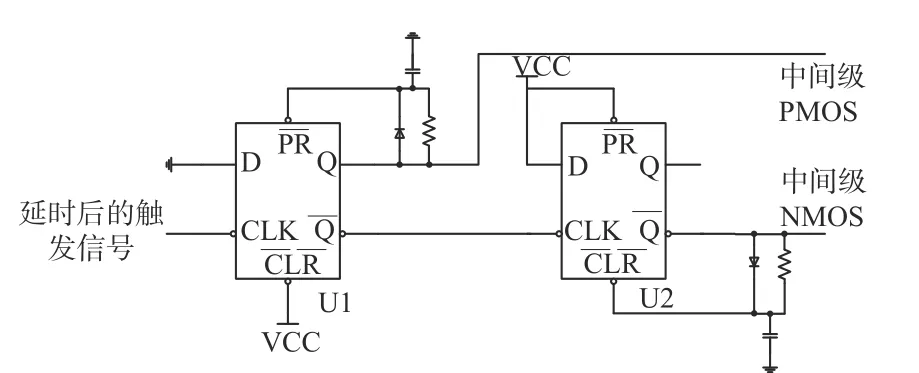

3.2 死区时间控制

MOSFET 推挽电路的驱动信号设计中要尽量避免2 个MOSFET 同时导通的情况,防止MOSFET 因瞬时的大电流损坏。这就需要在2 个MOSFET 交替导通过程中引入对死区时间的控制。由于本文在中间级与输出级均采用MOSFET 对管结构,都需要注意对死区时间的控制。死区时间控制单元电路如图8 所示。U1 的作用是利用时间偏置将一级驱动MOSFET 对管的时钟触发边沿分离。如图9 所示,为一次MOSFET 交替的控制时序图。即U2 输出的上升边沿触发短暂的NMOS开启信号,在NMOS 关闭后采取ns 级延时,待栅极的电荷泄放完毕,源漏通道夹断后,用延时结束后的信号边沿触发对管PMOS 导通的控制信号,开启对管PMOS,如此反复做双MOSFET 交替导通。

图8 死区时间控制单元电路Fig. 8 Circuit diagram of dead time control unit

图9 死区时间时序逻辑Fig. 9 Diagram of dead time sequential logic

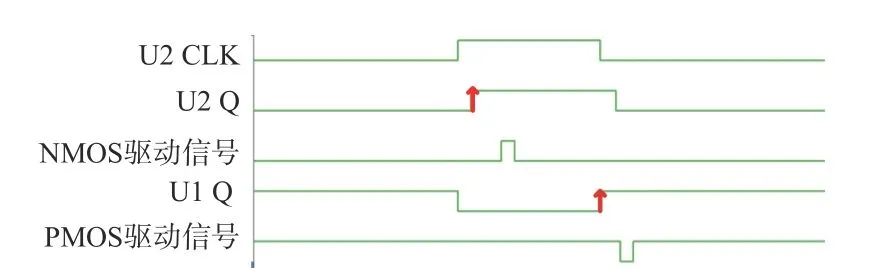

3.3 最小脉宽微调

考虑到使用环境的不同,光阴极输出端等效负载会有较大的变化,对最小脉冲有一定的影响。本文利用微调电容器做触发时间的补偿修正如图10 所示。通过调整时间偏置脉冲A 的触发时间,在与偏置信号与非运算后作为NMOSFET 的触发信号。通过调整微调电容,可以对输出级驱动NMOS 加速开启的偏置时间进行ns 级的微调,如图11 所示。

图10 最小脉宽微调电路Fig. 10 Diagram of minimum pulse width trimming circuit

图11 最小脉宽微调的时序逻辑Fig. 11 Diagram of sequential logic of minimum pulse width trimming

3.4 分阶段加速的逻辑设计

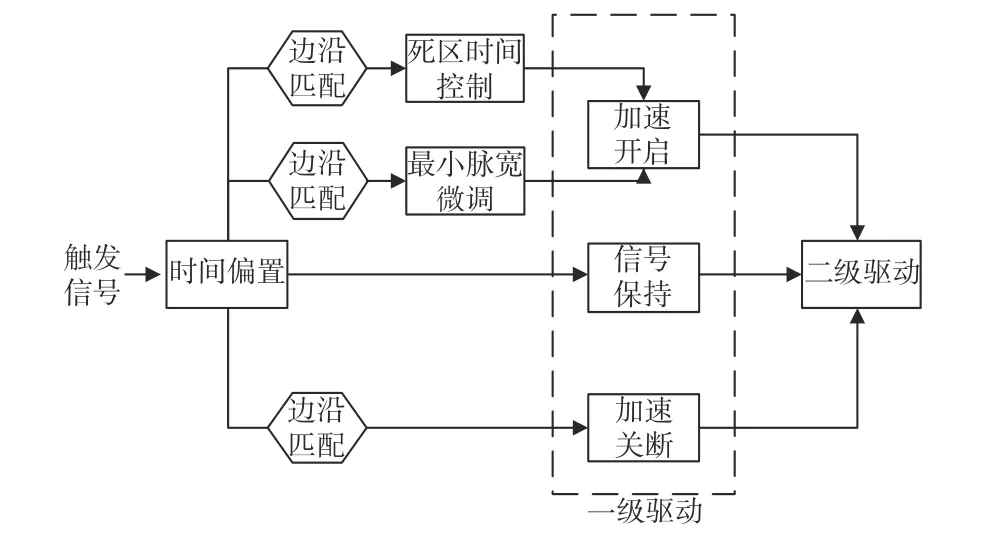

在逻辑设计上,采用3 个阶段、两级加速的驱动逻辑,如图12 所示。触发信号通过高速逻辑门构成的时间偏置电路,分为3 路子信号。一路子信号经一级驱动后,将电平偏移驱动输出端MOSFET,作为保持输出端MOSFET 栅极电压的保持信号。一路子信号通过门电路分NMOS 驱动、PMOS 驱动2 路进行边沿匹配,经过死区时间控制电路与最小脉宽控制电路进行中间级驱动,作为输出级驱动MOSFET 加速开启的驱动信号。最后一路子信号通过边沿匹配,在主信号的下降过程中产生一个脉冲,加速输出级驱动MOSFET 栅极的电荷释放。以触发信号的上升边沿为时间基准,驱动控制逻辑顺序为加速N 管关闭,加速P 管导通,信号保持,触发信号下降边沿亦然。

图12 驱动逻辑框图Fig. 12 Block diagram of drive logic

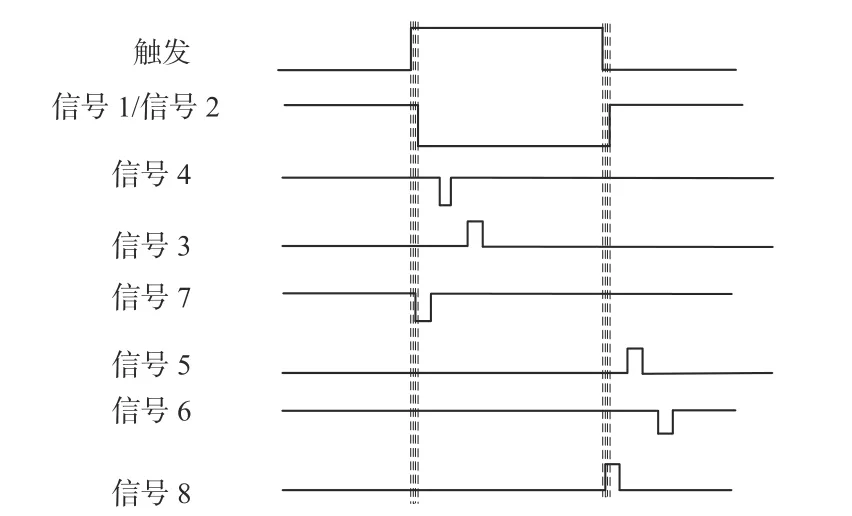

部分驱动逻辑如图13 所示,信号1/ 信号2 为保持信号,信号3、信号4 组成N 管的加速脉冲,信号5、信号6 组成P 管的加速脉冲,信号7、信号8 分别为PMOS 与NMOS 的加速关断信号。加速关断信号需置于交替管开启之前并保持一定时间,以避免2 个MOSFET 同时导通的情况。

图13 部分驱动逻辑Fig. 13 Diagram of partial drive logic

4 MOSFET 电路设计

4.1 MOSFET 加速导通电路

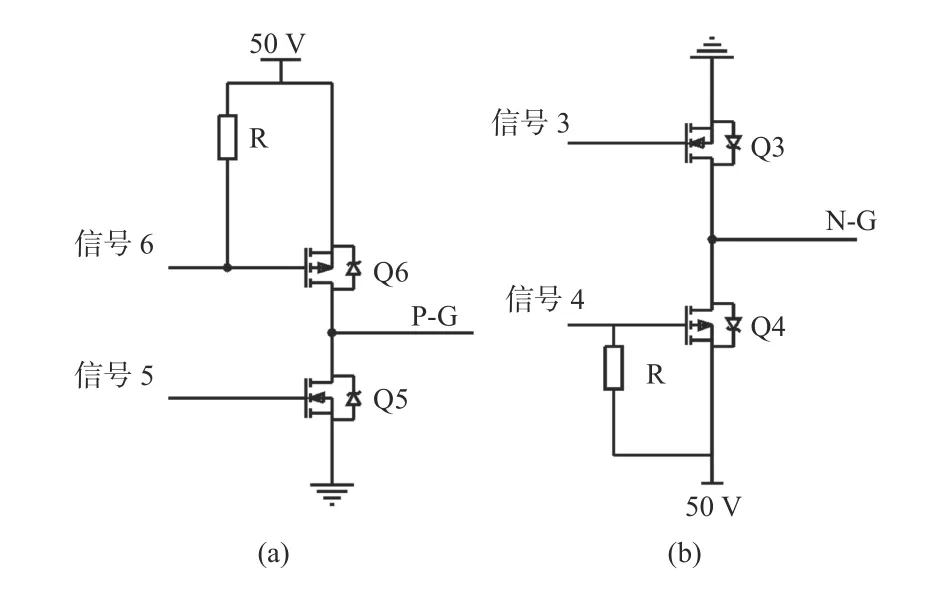

为了加速MOSFET 栅源电容的充电过程,最大限度地达到MOSFET 最快的导通速度,加速导通阶段的栅极采用50 V 驱动。为了让输出级驱动MOSFET 快速的通过线性区,同样采用MOSFET推挽电路的方式,获得快边沿脉冲,如图14 所示。信号5 首先到达NMOS 栅极,NMOS 导通,P-G 电位迅速拉至0 V。经过一个死区时间后,信号6 到达PMOS 栅极,PMOS 导通,P-G 电位迅速拉升至50 V,输出级驱动PMOS 的栅极P-G 接收到如图15所示的加速脉冲,中间级驱动完成上升沿加速过程。下降沿加速过程与加速过程相似,信号4 使Q4 先行导通,使N-G 电位上升至50 V,经过一个死区时间,信号3 使Q3 导通,N-G 拉至0 V,中间级驱动完成下降沿加速过程。

图14 加速导通(一级驱动)电路Fig. 14 Accelerated conduction (primary drive) circuit

图15 加速导通驱动信号Fig. 15 Accelerated conduction drive signal

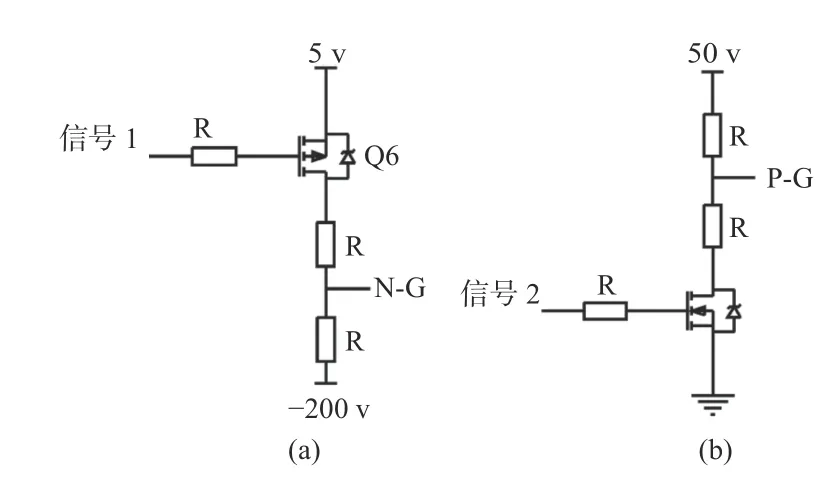

4.2 MOSFET 信号保持电路

瞬时较高幅值的加速信号能够使MOSFET 更加快速地导通,获得更加陡峭的上升边沿。但是随着加速信号结束,MOSFET 栅极电容开始放电,MOSFET 会趋于关闭,这时的输出电压无法保持。为使电平更加平稳,在MOSFET 加速导通阶段后采用保持信号作为衔接,保证加速阶段信号的完整性,如图16 所示。信号1 与信号2 为原触发信号经过ns 级延时的触发信号。

图16 信号保持(一级驱动)电路Fig. 16 Signal holding (primary drive) circuit

4.3 MOSFET 加速关闭电路

NMOSFET 与PMOSFET 交替过程中,应注意避免MOSFET 双开,否则瞬时的大电流会使MOSFET发热,甚至损坏MOS 器件。若只采用电阻回路放电的方式,其边沿时间较长,容易与匹配管的加速开启阶段相冲突,引起短时间内的MOSFET 同时导通。故在MOSFET 关断时刻,采用加速关断电路,利用MOSFET 的开关特性,迅速连通电荷泄放回路,将MOSFET 栅极的电位瞬间拉至源极电位,加速输出级MOSFET 关断,如图17 所示。

图17 加速关断(一级驱动)电路Fig. 17 Accelerated shutdown (primary drive) circuit

5 电路板级验证

因本文设计中的驱动逻辑信号较多,在控制板的电路板设计中采用4 层板设计,自顶向底为信号层、GND 层、电源层、信号层,如图18(a)所示。控制板的底部通过接插件与电源板相连接。电源板为双层板设计,可提供+50 V 与−200 V 两个电压,如图18(b)。为避免选通电路在工作中受到外界环境的影响,也防止人体静电损坏MOSFET,将2 块电路板组装后封进如图18(c)所示的金属壳内进行测试。

图18 硬件设计Fig. 18 Hardware design

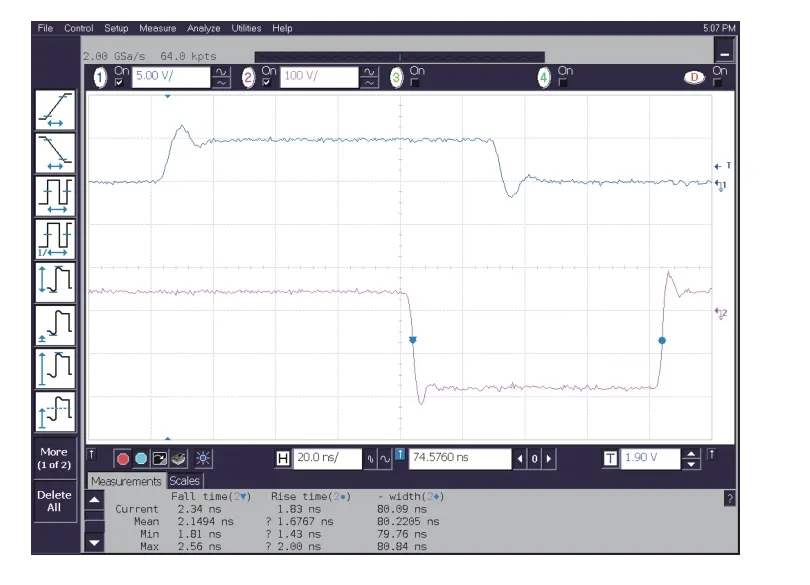

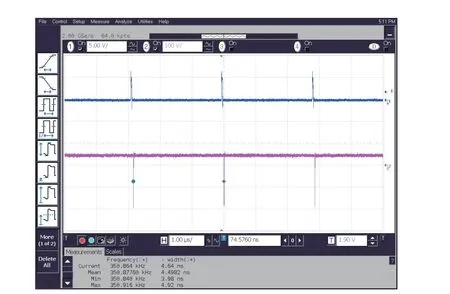

测试平台采用安捷伦MSO8104A 型示波器进行波形参数的测量,采用安捷伦33250A 型信号发生器作为脉冲触发源,使用直流稳压源提供模块所需的直流电压,如图19 所示。通过测试,如图20所示测得仅使用一路保持信号驱动输出的阴极上升信号,上升边沿达到了μs 级。图21 是在图20栅极控制电压幅值不变的基础上,利用提出的加速驱动电路输出的阴极上升信号与下降信号,上升下降沿均达到了2 ns,边沿时间提升明显。

图19 测试平台Fig. 19 Test platform

图20 加速前的上升边沿Fig. 20 Diagram of rising edge before acceleration

图21 加速后的上升边沿Fig. 21 Diagram of rising edge after acceleration

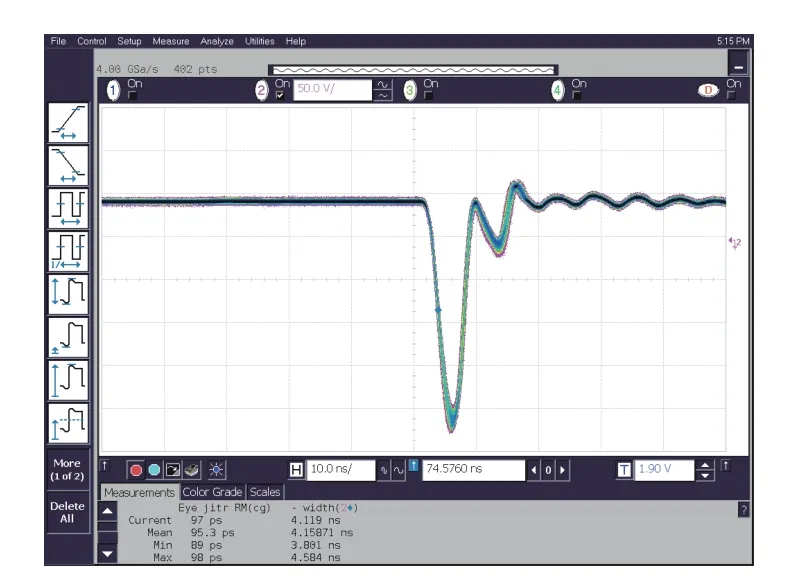

将信号发生器设置为最小脉宽,本文设计的选通电路输出3.7 ns,幅值为+50/−200 V 的脉冲,如图22 所示。对阴极选通电路高重频性能进行测试,在350 kHz 下,电路输出的波形仍能保持完整,如图23 所示。将示波器调整为叠加模式对波形抖动进行测试,可以看到脉冲抖动RMS 约为0.1 ns左右,电路输出较为稳定,如图24 所示。

图22 最小脉冲宽度输出Fig. 22 Diagram of minimum pulse width output

图23 选通电路高重频测试Fig. 23 Diagram of high repetition frequency test for gating circuit

图24 波形抖动测试Fig. 24 Diagram of waveform jitter test

6 结论

本文以MOSFET 推挽电路为基础,提出一种利用分阶段、多级加速工作的阴极高重频选通电路。经试验测试,本文研制的样机可提供+50 V/−200 V 的阴极关闭/开启电压,实现0~350 kHz 的重复频率,0~100%的占空比调整,3.7 ns 的最小脉冲宽度,脉冲输出延时时间抖动约0.1 ns。利用时间偏置电路单元相互级联产生2 级驱动信号,分3 个阶段对模块的输出级驱动MOSFET 的开启与关闭过程进行加速,这对于提升高速高压选通电源的最小脉冲宽度性能、最高工作重复频率以及降低器件功率损耗具有重要的指导意义。目前,英国Photek 公司与法国PHOTONIS 已推出相关产品,通过与Photek 公司最新同类产品GM300-N 的指标进行比较,本文设计除迸发模式工作频率略低于该进口产品,在脉冲边沿时间、最小脉冲宽度、幅值输出、脉冲重复频率等其余指标上基本与该进口产品处于同一水平,可作为该产品在相关领域中的国产化替代。国内也有机构在进行相关样机的研制,相比之下本文的设计在缩短脉冲边沿时间、实现更小脉宽等方面具有一定优势。