微通道板输入电极对开口面积比的影响及改进研究

2022-12-06王鹏飞邱祥彪邵爱飞孙赛林丛晓庆孙建宁乔芳建陈坤杨

王鹏飞,邱祥彪,邵爱飞,孙赛林,丛晓庆,金 戈,孙建宁,王 健,乔芳建,高 鹏,赵 胜,陈坤杨

(1. 北方夜视科技(南京)研究院有限公司,江苏 南京 211106;2. 北方夜视技术股份有限公司,云南 昆明 650217))

引言

微通道板(microchannel plate, MCP)是一种厚度0.3 mm~1 mm 左右的薄玻璃板,分布有几百万个相互平行的圆形通道,每个通道是一个独立的通道式电子倍增器。MCP 作为一种关键的电子倍增元件,广泛应用于微光像增强器、微通道板型光电倍增管、电子显微镜及荧光光谱仪等领域[1]。开口面积比(open area ratio, OAR)是MCP 的一项关键性能指标,通常微通道板的开口面积比为58%~65%。在像增强器中,开口面积比越大,阴极出射电子进入通道内被放大的概率也就越大,与MCP非开口面碰撞而损失的概率降低,从而提高探测效率[2-3]。

增大开口面积比是MCP 性能提升的重要方面,刘术林等通过将皮料玻璃管的内外径之比调整到接近微通道板的孔径和通道中心距之比,再控制单丝直径、复丝对边距和复丝内单丝的根数,实现了开口面积比在65.7%~69.2%范围内可控[4];苏德坦等人提出了一种大长径比皮料玻璃管加工技术,提高了MCP 阵列及开口面积比的一致性,对于提升开口面积比有进一步的促进作用[5]。随着MCP 孔径的不断缩小,通过减薄皮料厚度提升开口面积比导致孔壁越来越薄,很容易出现破损等疵病导致的发射点、黑点等问题,开口面积比的提升越来越困难。输入面扩口技术是提升MCP 开口面积比的另一种途径,S. Matoba 等人提出获得一种90%开口面积比的方法,并极大提高了探测效率[6];傅文红等将MCP 的开口面积从58%提高到73%,电流增益由3652.6 提高到4622.8[7],但由于工艺复杂、工艺可控性差等原因,经多年的研究目前尚未能够批量应用。

在新技术得到突破之前,开口面积比的提升还需要在传统工艺中深入挖掘。MCP 的电极膜层通常使用NiCr 合金,其具有良好的导电性能、热稳定性和低电阻温度系数[8-9]。MCP 输入面镀制的电极是开口面积比的重要影响因素:镀膜过程中,膜层镀制在表面的同时不可避免地会镀在一定深度内的侧壁上,导致镀膜后孔径缩小,关于此部分的影响尚未研究。针对镀膜对开口面积比的影响,本文通过构建理论模型,定量计算了镀膜对于MCP开口面积比的影响。在理论计算的基础上,通过调整镀膜工艺、改变镀膜方式降低了电极膜层对开口面积比的不利影响。

1 输入端电极膜层对开口面积比影响的理论分析

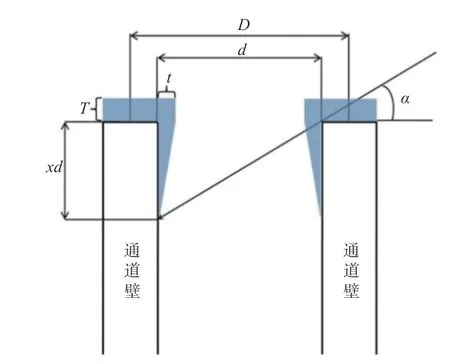

根据MCP 输入面实际镀膜状态建立理想模型如图1 所示。图中:D为孔间距;d为基底孔径;α为镀膜角度;xd为镀膜深度(x=tanα);T为表面膜层厚度;t为通道内壁侧壁膜层最大厚度,为方便计算,理论模型中斜切角设置为0。

图1 电极膜层影响开口面积比模型Fig. 1 Model of OAR influenced by electrode film

未镀膜时开口面积比计算公式为

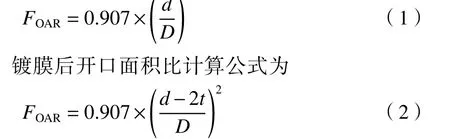

设置镀膜角度为90°时,表面的镀膜速率为V,镀膜角度为α,MCP 无自转时,通道内壁镀膜俯视示意图如图2 所示。

图2 通道内壁镀膜俯视图Fig. 2 Top view of coating in channel inner wall

沿镀膜方向直径CD剖面,C点处表面镀膜速率为V·sinα,侧面镀膜速率为V·cosα,C点处侧壁厚度t计算为

由于MCP 正常镀膜时存在自转,侧壁的膜厚为单个通道圆周上各位置平均的膜厚。由于遮挡,半圆ADB通道内壁无膜层,进半圆ACB能够镀上膜层。其中半圆ACB中,以弧长ef为例,镀制在弧ef内的镀膜料与直径方向虚拟的e'f'相同,根据微积分思想,镀制在半圆ACB上的膜层总量与虚拟的台阶直径AB上相同,计算出准确的t:

将(4)式带入(2)式,得到考虑电极膜层影响之后的开口面积比的计算公式(5)以及镀膜所导致的开口面积比损失量:

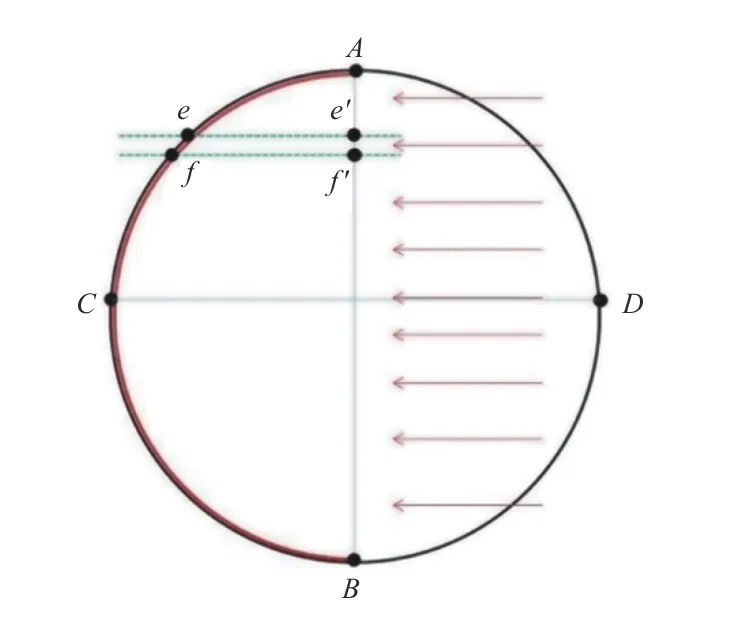

从公式中可以看出,影响因素主要有:镀制电极的膜层厚度、镀膜深度以及基底的孔径、孔间距。当MCP 基底不变时,膜层厚度越厚,镀膜深度越浅,则开口面积比的损失量越大;当膜层厚度与镀膜深度不变时,基底孔径越小,则开口面积比的损失量越大。MCP 实际参数为:孔径6.7 μm、孔间距7.9 μm、镀膜深度3.35 μm、膜层厚度300 nm,以此为基础进行模拟计算,结果如图3 所示。

图3 膜层厚度、孔径对于MCP 开口面积比的影响Fig. 3 Effect of film thickness and aperture on opening arearatio of MCP

从模拟的结果来看:基底不变,开口面积比损失量与膜层厚度基本呈现线性关系;镀膜工艺不动,膜层厚度一致,MCP 孔径越小,所受到的影响越大。

2 试验结果与分析

2.1 试验条件和方法

本试验电极膜层的镀制采用物理真空蒸发法,加热方式为电子束加热,分别采用2 种方式来有限减少电极膜层厚度,一是使用Ni80Cr20 为膜料,改变工艺参数,控制Ni、Cr 比例改善面电阻;二是使用Ni、Cr 金属单质,利用叠加膜层的镀制方式来控制Ni、Cr 比例,改善面电阻。本试验所用的MCP 为Φ25-6 型号的MCP,其外径为25 mm,厚度为0.31 mm,孔径为6.7 μm,斜切角为6°,裸板的开口比为65%。输入和输出电极的深度固定,其中输入电极深度约为0.5d,输出电极深度约为2.0d,d为MCP 的孔径。

2.1.1 镀膜工艺调整法

合金在气化过程中,由于各成分的饱和蒸气压不同,使得其蒸发速率也不同,会发生分解和分馏,因而合金中各元素原子的蒸发过程实际上可以被看做是相互独立的过程。根据相平衡理论,温度高蒸气压就高,固态金属的蒸发量就大。同理,蒸气压越高的金属也越容易受热蒸发,所以,合金蒸发出来的蒸气可能具有完全不同于其固态或液态的成分,后果是沉积后的薄膜成分偏离其固态的化学组成[10-11]。

MCP 镀膜通常使用的是Ni80Cr20 合金,原有的镀膜工艺,镀制出的电极膜层Cr∶Ni 通常为1∶1~1∶1.5 左右。根据合金中各组分蒸发速率的公式[12]:

说明镍铬合金中铬的初始蒸发速率为镍的2.8 倍,正是由于这种分馏现象,使得MCP 电极膜层的Cr、Ni 比例与镀膜料自身的比例存在差异。

一般情况下,采用真空蒸镀方法来制备合金薄膜,可以使用闪蒸法、多源共蒸法来控制成分[13]。本文在原工艺基础上进行相关设备工艺参数的调整,提高镀膜料的加热速度,以较大的功率密度实现快速蒸发,使之接近闪蒸法的效果,减少初始阶段合金分馏和蒸发速率的差异,使镀制的薄膜成分更加接近蒸发物材料成分,最终实现MCP 上镍铬电极中Ni、Cr 元素比例的控制。

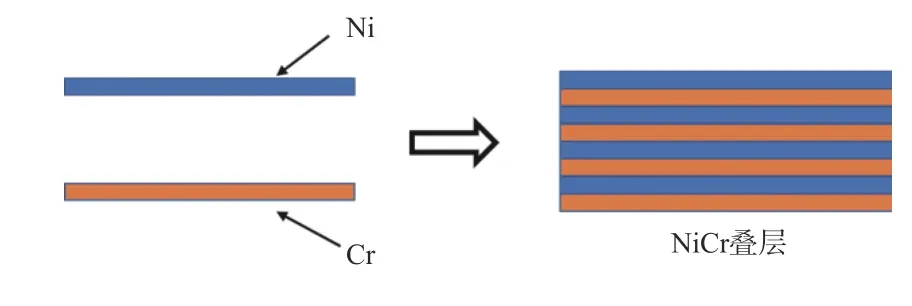

2.1.2 镀制叠层法

叠层顾名思义就是将2 种或2 种以上材料,根据设计需要一层层叠加起来,如图4 所示。为保证膜层在MCP 上的牢固度,叠层镀制必须先镀与玻璃附着比较牢固的Cr[14]。叠层材料能够基于各组元材料的本征性能,充分发挥各组元间的复合、协同及多性能响应机制,是透明导电薄膜领域常用的技术手段,通过叠层元素的改变,可以实现低方块电阻、高透过率的双重要求[15]。

图4 NiCr 叠层结构示意图Fig. 4 Schematic diagram of NiCr laminated structure

叠层电极的具体工艺过程如下:1) 将经氢气还原过的MCP 装在镀膜夹具上,放进镀膜机腔室内,抽高真空;2) 在高真空下,旋转夹具,高温下对MCP 进行烘烤;3) 烘烤结束,电子束先加热Cr,打开挡板蒸镀一定膜厚,关闭挡板;4) 坩埚切换到Ni,电子束加热,打开挡板蒸镀一定膜厚的Ni,关闭挡板;5) 根据设计比例重复一定次数的3)和4);6) 完成镀膜,关闭电子束加热装置,自然冷却至室温,停止抽真空,充气至大气压,取出。经过上述过程,可以在MCP 的端面镀制任意Cr、Ni 比例的电极膜层。

为了比较 MCP 端面电极膜层Cr、Ni 比例改变带来的增益变化,将其装入像增强器管壳中,在MCP 综合测试仪上进行测试。

2.2 试验结果与讨论

2.2.1 镀膜工艺调整法

2.2.1.1 工艺参数与电阻率关系

通过改变电子枪的设置参数,调整镀膜料的蒸镀温度。我们试验发现随着蒸镀温度的升高,电阻率呈减小趋势,这就可以在满足面电阻要求(20 Ω/□~30 Ω/□)的前提下,减薄电极膜层厚度,表1为蒸镀工艺调整与电阻率的对应关系。

表1 蒸镀工艺与电阻率的关系表Table 1 Relationship between evaporation process and resistivity

通过分析,我们认为蒸镀温度的升高,使合金快速蒸发,有利于减弱Ni、Cr 之间蒸气压的差异带来的影响,使蒸发过程接近“闪蒸法”的镀膜效果。

2.2.1.2 工艺参数对开口面积比影响

使用同批次MCP,未镀膜MCP 半成品孔径为6.7 μm,孔间距为7.9 μm,开口面积比为65%。按照20 Ω/□的面电阻要求,我们使用工艺二与原工艺进行镀膜后开口面积比的对比,通过测量镀膜后的实际开口面积比,结果如表2 所示,工艺二可减少开口面积比的损失约2 个点。

表2 蒸镀工艺与方块电阻的关系表Table 2 Relationship between evaporation process and square resistance

2.2.2 镀制叠层法

2.2.2.1 镀制叠层与电阻率关系

通过增加Ni 膜层的厚度,可以提高Ni 的比例。在膜层厚度一致的前提下,随着Ni 的比例升高,电极膜层的电阻率呈减小趋势,如表3 所示,较小的电阻率对减小膜层厚度,提高开口面积比是十分有利的。通过使用胶带剥离法测试,叠层的最底层为Cr 膜层时,叠层的牢固度与镍铬合金膜层相比没有差异,镀制叠层的MCP 完全符合使用要求。

表3 叠层工艺与方块电阻的关系表Table 3 Relationship between lamination process and square resistance

2.2.2.2 镀制叠层对开口面积比影响

使用同批次MCP,未镀膜MCP 半成品孔径为6.7 μm,孔间距为7.9 μm,开口面积比为65%。按照20 Ω/□的面电阻要求,选择1∶5 比例与正常工艺镀膜制作MCP 进行对比。

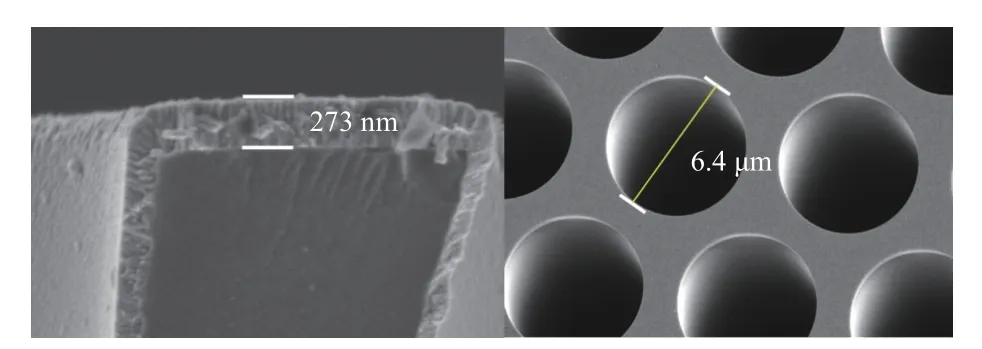

叠层镀制1∶5 膜层厚度仅为86 nm,镀膜后孔径为6.6 μm,开口面积比为63%,如图5 所示。

图5 MCP 输入端NiCr 叠层实物图与孔径测量实物图Fig. 5 Physical drawing of NiCr laminated film and aperture measurement at MCP input terminal

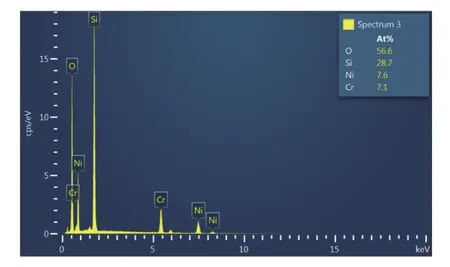

对输入端膜层进行了EDS 能谱测试,Cr∶Ni=1∶4.98,比例符合设计值,测试结果如图6 所示。

图6 输入端膜层Cr∶Ni=1∶5 的EDS 能谱图Fig. 6 EDS energy spectrum of input terminal film when Cr∶Ni = 1∶5

原镀膜工艺膜层厚度273 nm,镀膜后孔径为6.4 μm,开口面积比为59.5%,如图7 所示。图8为EDS 能谱测试图,结果显示Cr∶Ni=1∶1.1。

图7 原镀膜工艺膜层实物图与孔径测量实物图Fig. 7 Physical drawing of film layer and aperture measurement of original coating process

图8 原镀膜工艺制出输入端膜层EDS 能谱图Fig. 8 EDS energy spectrum of input terminal film prepared by original coating process

相较于原镀膜工艺,使用叠层镀膜工艺,控制Cr∶Ni=1∶5 时,在达到相同的面电阻要求下,开口面积比从60%提升到63%。与未镀膜的毛坯板相比,开口面积比仅损失3 个百分点。

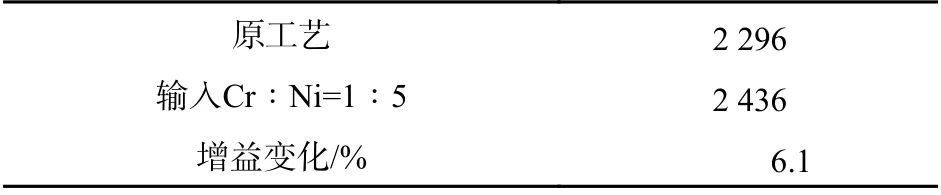

2.2.2.3 镀制叠层对增益的影响

将上述2 种对比试验的MCP 装在MCP 测试仪上进行增益测试,Cr、Ni 膜层的MCP 增益高约6%,MCP 电压在800 V 下的增益测试结果如表4所示。

表4 原镀膜工艺与Cr∶Ni=1∶5 时,800V 电压下MCP 增益对比表Table 4 Comparison of MCP gain under 800 V voltage between original coating process and Cr∶Ni = 1∶5

3 结论

本文建立了电极膜层对MCP 开口面积比影响的理论模型,通过理论分析,量化了电极膜层对MCP 开口面积比的影响程度。为了改善电极膜层对开口面积比的影响,提出了镀膜工艺调整与镀制叠层2 种工艺方法,通过控制MCP 端面电极膜层Cr、Ni 比例,可控制MCP 端面电极的电阻率。通过提高电极膜层Ni 含量,在满足面电阻要求的前提下,实现了将输入端电极膜层减小到86 nm的水平,减少膜厚对开口面积比的损失,使开口面积比提高3%~4%,通过实际测试,增益可提高6%左右。