红外地球敏感器光电组件测试系统设计

2022-10-12佟亚珍宋佳赟李晶晶王培超

潘 攀,佟亚珍,宋佳赟,李晶晶,王培超

(北京东方计量测试研究所, 北京 100086)

0 引言

圆锥扫描式红外地球敏感器是中低轨道航天器姿态测量的关键部件,其中,光电组件的性能参数直接影响卫星姿态角的测量精度。卫星控制系统对光电组件测试系统提出的要求为:信号幅值采集精度优于50 mV/20 V,信号频率测试精度优于1 Hz/100 kHz。鉴于国内对相关电信号测量的研究不多,设计了一种红外地球敏感器光电组件测试系统,精确测量了光电组件的光栅信号和基准信号的幅度、频率等参数,对实现卫星姿态的精准定位,有效提高卫星在轨的自主性具有参考意义。

1 系统硬件电路

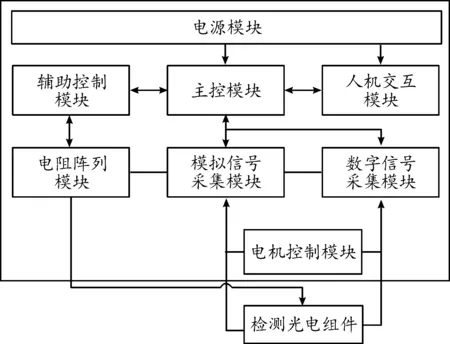

红外地球敏感器光电组件测试系统的硬件电路构成主要包括模拟信号采集模块、数字信号采集模块、电阻阵列模块、电机控制模块、辅助控制模块、主控模块和电源,测试系统组成如图1所示。

图1 红外地球敏感器光电组件测试系统框图

主控模块为核心控制器模块,它一方面将软件界面设置的电机转速等参数传输给电机控制模块以驱动电机并提取转速等信号,另一方面完成测试过程的动作实施,通过反馈的相关信号进行计算并存储;模拟信号采集模块为电机电流遥测信号及被测光电组件模拟信号采集硬件电路;数字信号采集模块为电机转速及被测光电组件信号频率采集硬件电路。

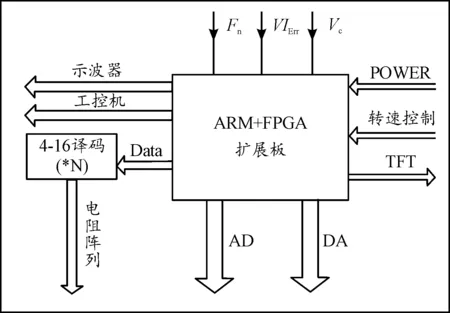

1.1 主控模块

主控模块采用ARM+FPGA方案,设计原理如图2所示。ARM在控制方面性能优异,能够很好地完成分配调度任务和运算工作,且在驱动TFT、通信等方面非常稳定。对于信号采集,采用FPGA+高精度AD实现。双核ARM Cortex-A9提供最大667 MHz的频率,极大增强了控制单元的控制和处理能力,并包含丰富的存储功能,提供HDMI、VGA等多种接口形式满足设备各种通信需求。

图2 主控模块设计原理框图

1.2 模拟信号采集模块

由于系统需要进行A/D转换的信号较多,精度要求高,故采用TI的ADS8568作为A/D采集芯片,设置成8通道同步采样,保证基准信号、光栅信号可独立通断使用,也可以并行使用。

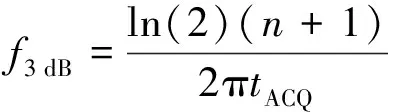

ADS8656为SAR类型ADC,对输入信号要求较高,输入电流由实际采样率、输入电压、源阻抗决定。ADC工作时需要信号将内部的充电电容充满直到转换周期开始,设转换周期为tACQ,则其 -3 dB带宽为:

(1)

式中:n为ADC的有效位数。以最小转换时间280 ns为例,此时需要的前置ADC带宽约6.7 MHz,如果小于该值,引起的增益误差将不能被修正。

SAR ADC对信号源输出阻抗也有较高要求,信号源的输出阻抗比满足:

(2)

式中:n为ADC有效位数;Cs为充电电容(4Vref时为10 pf);RSER为200 Ω输入电阻值;RSW为内部开关电阻值。以最小转换时间280 ns时为例,此时源阻抗必须小于2 kΩ,而在很多电压测量环节,要求源阻抗小于2 kΩ几乎不可能,所以在ADC之前需要增加一个高带宽的ADC驱动器,要求其带宽足够大,输出阻抗尽可能小。

1.3 数字信号采集模块

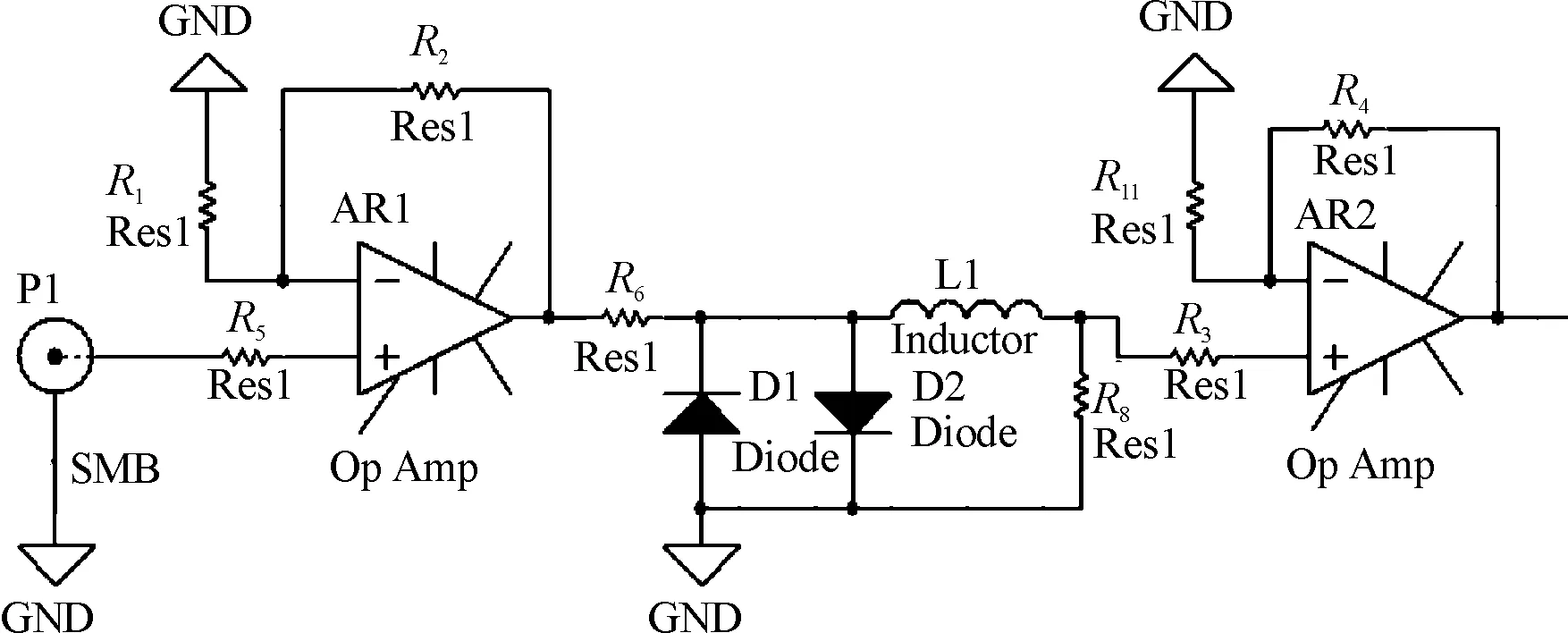

数字采集模块实质上是FPGA对IO口TTL波形的计数。而基准输出信号、光栅输出信号为正弦波信号,信号的幅值为0.1~12 V,不符合TTL信号电平要求,需要一个前端电路将其调理成TTL电平。该频率测量前端电路如图3所示。

图3 频率测量前端电路图

图3中被测信号通过P1输入,R5为限流电阻,AR1为放大电路,使得0.1~12 V的电压信号能放大到后级限幅电路的限制范围。D1、D2将输入信号限幅到0.7 V左右,再通过AR2放大到近似TTL电平的幅值范围。AR2的输出接到施密特芯片74HC14,转换成标准的TTL信号,再输入FPGA的IO做等精度频率测量。

FPGA内部时钟频率需要做出厂标定,通过内部程序将100 MHz系统时钟10分频输出,由片上系统内部的选择器将信号输出到后面板,校准时使用外接频率计即可。

1.4 电阻阵列模块

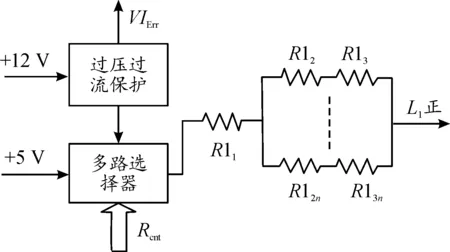

光栅信号、基准信号通过调节电阻的阻值调节发光二极管强度。电阻阵列模块原理如图4所示。

图4 电阻阵列模块原理图

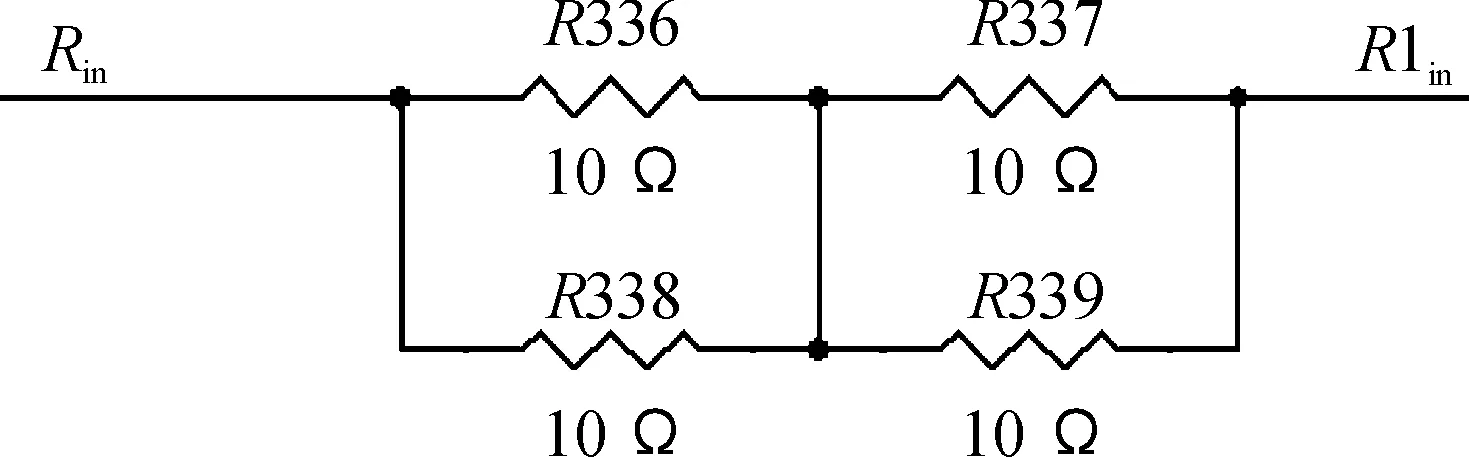

12 V电源通过过压过流保护进入电子开关。电子模拟开关输入经过R11采样电阻进入电阻阵列R12~R12n,电阻阵列的输出连接发光二极管L1的正极。L1通过的电流约为几十毫安,所以采样电阻选择718厂RMK(1206)型有失效率等级的片式薄膜系列贴片电阻,阻值为10 Ω。电阻温度系数为±10×10-6/K,阻值偏差±0.05%,极限电压为100 V,满足此处的电流采样要求。同时,选用4只10 Ω(70°额定功率0.25 W)电阻串并联组成10 Ω(图5),此时采样电阻上的额定功率增加到1 W,系统正常工作时采样电阻上的最大功率为:

(3)

额定功率远大于该采样电阻上正常工作时的最大功率,满足系统稳定性要求。

图5 10 Ω采样电阻电路图

2 系统软件设计

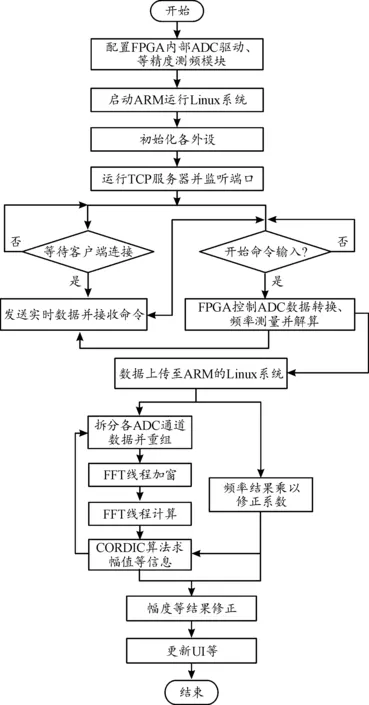

系统软件运行在Linux 系统中,总体设计流程如图6所示。系统上电启动应用程序,应用程序开始后配置FPGA内部ADC驱动、频率测量模块驱动,初始化各外设,运行TCP服务器并监听设定端口;ADC、频率测量模块得到的数据传输到ARM Linux中进行处理,ADC数据经过滤波、加窗、FFT、幅值恢复及显示等处理,频率结果直接修正显示。

图6 系统总体设计流程框图

光电组件光栅信号和基准信号的幅值采用傅里叶变换将时域连续的信号转换到频域内,通过适当的探测算法得到想要的幅度谱数据。为了提高幅值的精度,通常采用加窗、频谱修正等技术,加窗的目的是压低旁瓣、减小频谱的泄露。连续信号经过加窗截断后的数据再通过FFT计算可得到信号的频谱,频谱经过相关计算即可得到信号的幅度谱。FFT计算过程中包含各种窗函数,不同的窗函数得到的幅度谱精度不同,Flat Top窗函数可以较精确地恢复各个不在分辨率上的信号幅度。本文采用目前应用较广的Flat Top窗函数进行幅度谱分析计算,该窗函数的形式为:

(4)

其中:ck为关于k的常数;N为FFT计算点数。

不同维度的Flat Top窗能得到不同的精度,HFT248D是Flat top窗中误差最小的算法,也最复杂,其公式为:

ωj=1-1.985 844 164 102cos(z)+

1.711 764 385 06cos(2z)-

1.282 075 284 005cos(3z)+

0.667 777 530 266cos(4z)+

0.240 160 796 576cos(5z)+

0.056 656 381 764cos(6z)-

0.008 134 974 479cos(7z)+

0.000 624 544 650cos(8z)-

0.000 019 808 998cos(9z)+

0.000 000 132 974cos(10z)

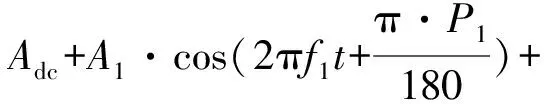

时域、频域的波形如图7所示。

假设原始信号为

(5)

式中:Adc为直流分量幅值;f1为被测信号频率;P1为初始相位;fn为干扰信号频率。

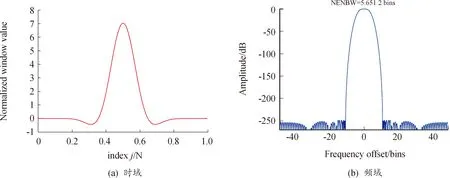

假定Adc=1.5,A1=3.1,A2=1.5,f1=6 274.25,f2=2 000.5,P1=-30,P2=90,其时域波形如图8(a)所示,加窗后时域波形如图8(b)所示,FFT结果如图8(c)所示。

图7 时域、频域波形

图8 信号FFTW前后波形

FFTW库是美国麻省理工学院计算机科学实验室超级计算组开发的目前世界上公认运算较快、使用广泛的串行C程序自适应软件包。FFTW库能自适应系统硬件,可移植性强,可用于计算任意维数的实、复数类型的离散傅里叶变换。FFTW库主要通过灵活运用运行时性能分析和相关的搜索技术来选择离散傅里叶变换的最优分解路径,可适应于不同的计算机体系结构。FFTW库主要由底层的代码生成器和上层的运行框架两部分组成,FFTW底层基本实现了所有的快速傅里叶变换算法。在FFTW库自动化配置时会记下每一个算法的执行时间和对于任意问题规模的快速傅里叶变换。

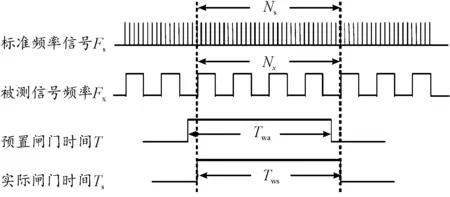

光电组件光栅信号和基准信号的频率为0~44 kHz,测试精度不大于5″。采用等精度测量方法。等精度频率测量法是在直接测频方法基础上发展而来,其实际闸门时间不固定,是被测信号周期的整数倍,与被测信号同步,因此又称为多周期同步法。此方法利用闸门与被测信号同步消除对被测信号计数时产生的±1个周期误差,测量精度大为提高,实现了在整个测量期间的等精度测量。频率测量原理及波形如图9所示。

图9 等精度频率测量原理及波形

在测量过程中,有2个计数器分别对标准频率信号Fs及被测频率信号Fx同时计数。首先给出预置闸门上升沿开启信号,此时2个计数器并不开始计数,而是等到被测频率信号的上升沿到来时才真正开始计数。当预置闸门下降沿关闭信号到来时,2个计数器并不立即停止计数,而是等到被测频率信号的上升沿到来时才停止计数,完成一次测量过程。

设标准信号的频率为Fs,被测信号的频率为Fx,在测量时间段Tws内被测频率信号的计数值为Nx,标准频率信号的计数值为Ns,则式(6)成立。

(6)

设被测信号的频率准确值为Fx0。在一次测量过程中,由于被测信号Fx计数的起停时间是由该信号的上升沿控制的,因此在测量时间段Tws内对Fx的计数Nx无误差。在此时间段内对Fs的计数Ns最多相差1个脉冲,即|ΔNs|≤1,则下列等式成立:

(7)

根据相对误差公式:

(8)

则被测信号Fx的相对误差

(9)

由式(9)可知:被测信号频率的相对误差与被测信号的频率无关,增大测量时间段Tws或提高Fs可以增大Ns,从而减小相对误差,提高测量精度。测量精度与实际闸门时间和标准信号频率Fs有关,与被测信号频率无关,因此能获得较高的精度。

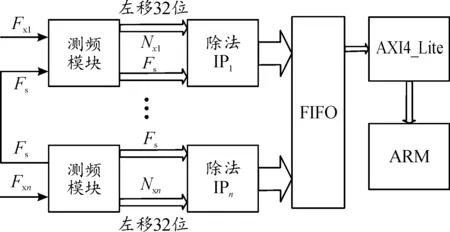

等精度测量过程中会产生2个量:Nx和Ns,位宽都是32 bit,而AXI4_Lite位宽为8 bit,两接口的对接使用到双口RAM,且N通道的频率测量模块结果将达到N*32 bit,无法直接连接到只有8bit的AXI4_Lite接口,中间还需要一级FIFO转换,利用这种方法可实现数据传输。但由于在ARM中实时读取设备文件时保证Nx和Ns数据对齐异常困难,很容易出现错误,因此设计了一种新型频率采样方案。该方案能够有效解决同步传输易出错和CPU占用率高的问题,其计算流程见图10。

图10 测量结果计算流程框图

如图10所示,左移32位是为了减少ARM中处理FPGA产生的复杂小数带来的运算,Nx扩大了232倍,小数结果保存到整数部分的64位数据中,在FIFO写入数据过程中可保证不会丢失任何一个通道的数据,也不存在Nx和Ns不同步的情况。结果传输到ARM中只需右移32 bit,再乘以修正晶振频率即可得到精确结果,该算法带来的误差为2-32,对于测量来说可忽略不计。同时,控制器的结果计算只需要32移位操作,极大降低了CPU使用率。

3 系统测试

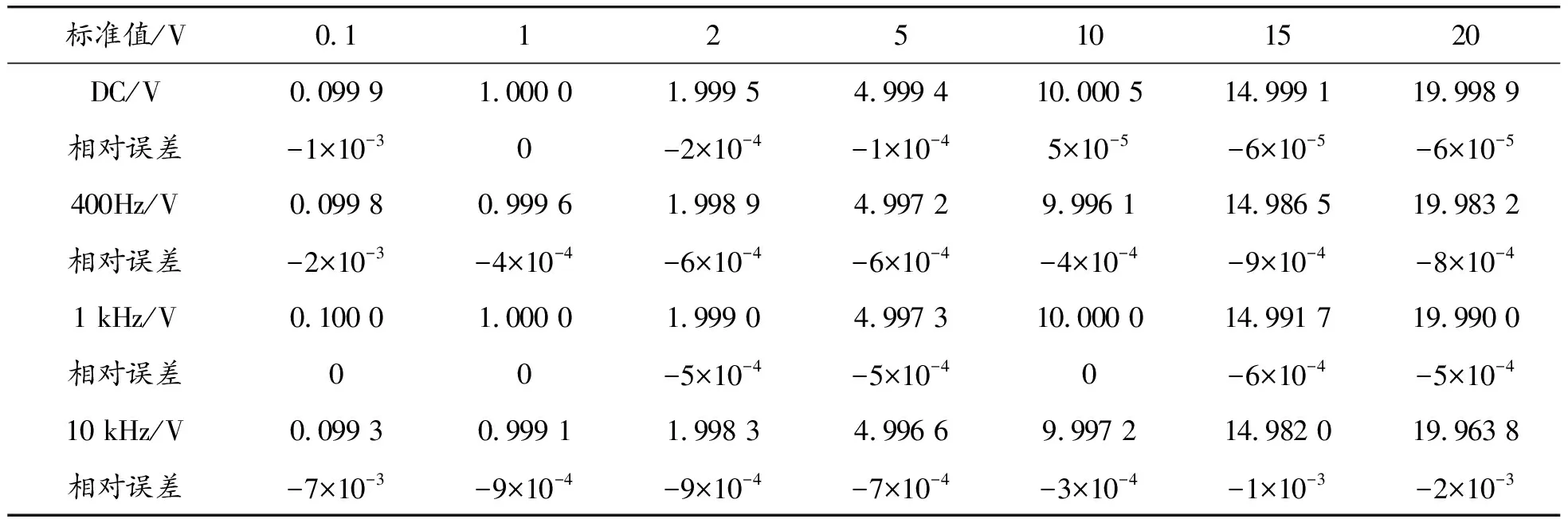

3.1 幅度测试

采用红外地球敏感器光电组件测试系统对幅值范围为0.1~20 V,频率范围为DC~10 kHz的被测信号进行测试,测试结果如表1所示。

测试结果表明,设计的光电组件测试系统信号幅值采集精度优于0.2%(47 mV/20 V,10 kHz),能够满足设计要求。

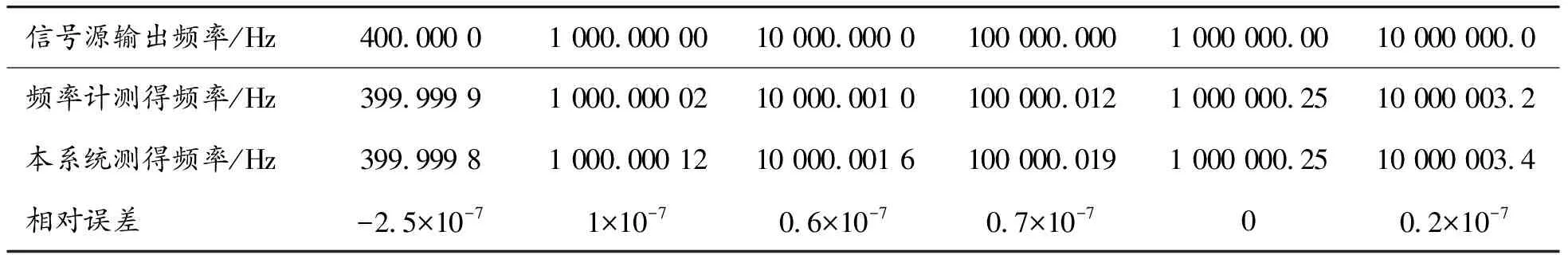

3.2 频率测试

采用设计的红外地球敏感器光电组件测试系统和频率计分别对400 Hz~10 MHz的被测频率进行测试,测试结果如表2所示。测试结果表明,设计的光电组件测试系统信号频率测试精度优于1×10-7(0.01 Hz/100 kHz),能满足设计要求。

表1 幅度测试结果

表2 频率测试结果

4 结论

1) 设计的红外地球敏感器光电组件测试系统能够满足光电组件测试系统的设计要求,能够实现光电组件的光栅信号和基准信号的幅度、频率的精确测量。

2) 该系统在达到较高集成度的同时保证了较强的性能和较好的计量特性。