冗余箭载计算机余度管理*

2021-10-26张卓政杜建峰范崇盛张晶晶王亚平

张卓政,杜建峰,范崇盛,陈 川,张晶晶,王亚平

(1.上海航天控制技术研究所·上海·201109;2.上海空间推进研究所·上海·201112)

0 引 言

箭载计算机主要承担飞行控制任务,工作在强电磁辐射、冲击、振动等恶劣环境中。作为运载火箭控制系统的核心,箭载计算机对故障应对能力和可靠性有着非常高的要求。余度技术可采用可靠性相对较低的部组件组合成高可靠性的系统,从而提升火箭控制系统的任务可靠性和安全性。随着对元器件自主可控要求的不断提高,余度技术也有利于进一步促进国产元器件替代进口器件。

余度管理一般涉及以下方面:

(1)余度配置:余度计算机的冗余方式包括双模冗余、三模冗余和更高级别的N模冗余。双模冷备份或热备份的长期可靠性均高于三模冗余表决系统。但是,一旦发生故障而不能及时定位故障,则不能保证正确的输出,而N模冗余的成本和复杂度均太高。多种航空航天无人飞控系统采用三模、四模冗余计算机实现了飞控任务。文献[2]中的某火箭上面级计算机采用了3主1备冗余,逻辑复杂,由于空间飞行任务的时间过长,故障模块的恢复期最长达到了8s。

(2)时钟同步:同步是余度计算机余度管理的基础和前提条件,只有在同步的前提下,对输入、输出的结果进行监控或表决才具备意义。时钟同步可以通过硬件实现,也可以通过软件实现,通过软件实现的时钟同步也被称为松散同步。

常用的硬件同步方法包括:公共外部时钟同步、精确独立时钟同步、互反馈独立时钟同步。

公共外部时钟同步:所有冗余模块共用一个时钟源。配置简单,相位和频率均有保证。但由于是一个单点,有共因失效的风险。

精确独立时钟同步:所有冗余模块使用自己的时钟源。由于各个时钟相互独立,相位误差是随机的。实践表明,各个时钟源的频率稳定性和精确性只能够维持短时间的同步,时钟漂移累积误差最终将造成失步。

互反馈独立时钟:所有冗余模块有自己的时钟源,各模块之间通过交互反馈调节漂移而得出最终的同步时钟。这种配置较为复杂,但可提供长时间的时钟同步。

松散同步以软件算法为基础。例如,各模块之间采用软件通信方式完成交互反馈即是一种松散同步的实现方法。由这种方式所获得的冗余模块的同步程度取决于通信速率、各模块的自身时钟精度和交互频率。

文献[1]采用主备份时钟实现了冗余模块同步,采用单独的硬件实现了表决功能,但是对时钟晶振需要进行特别的筛选,且表决器本身是单点;文献[5]和文献[7]通过软件方式实现了任务级的时钟同步。

(3)表决逻辑:文献[5]默认冗余模块序号较小的模块具有较高的优先级,这一假设不够合理。

(4)自检测:文献[7]设计了机内测试(Built-in Test,BIT)。目前,新一代运载火箭XX-5、XX-7电气系统均采用了BIT自检测技术。BIT自检测技术能够提高故障诊断的精确性、显著缩短诊断时间,但未能充分发挥其系统表决功能。

运载火箭控制系统具有对实时性的要求高、任务时间较短的特点,因此大部分运载火箭控制系统采用的是三模冗余方式。本文研究的余度管理设计主要包括冗余模块的配置,通道表决、时钟,以及输入输出冗余信号的监控与表决。冗余配置取消了表决器单点;时钟同步采用了互反馈的独立时钟,并通过软件备份实现了任务级的同步;开关量的输出级额外设计了 “五管冗余”硬件冗余表决进一步提高了可靠性,并充分引入BIT信息参与通道表决,改善了表决的完备性。

1 箭载计算机余度配置

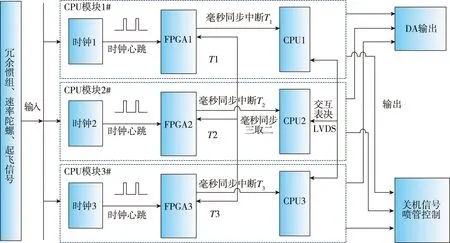

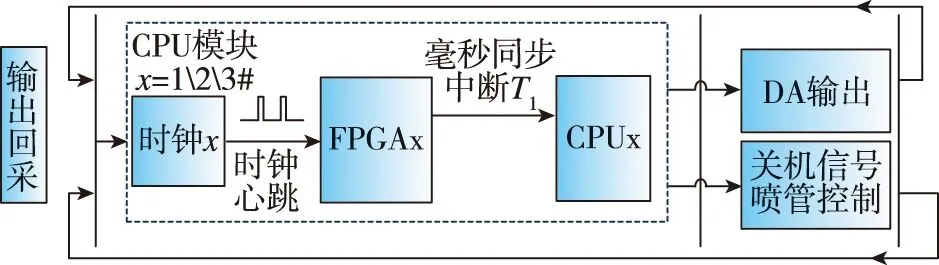

如图1所示,本文研制的三模冗余箭载计算机主要由三个相同的处理器单元(CPU)模块构成。三个模块的组成完全相同,且每个模块的关键器件配备有精密时钟、FPGA、CPU,以及必要的隔离驱动电路。每个模块都有自己的时钟脉冲,通过FPGA与其他两个模块的时钟脉冲交互表决,产生毫秒并同步中断给本模块的CPU。每个CPU都产生自己的输出,其他两个CPU通过内部LVDS总线交互关键信息,再表决及输出。

图1 三模冗余箭载计算机余度结构示意图Fig.1 Topology diagram of triple modular redundancy computer of launch vehicle

由于箭载计算机的信息输入和运算输出控制的下一级执行机构被执行了冗余配置,相应的输入和输出接口须进行余度设计。

冗余惯组、速率陀螺输入信号为RS422数据,起飞信号输入为开关量,测试用舵反馈输入为模拟量;输入链路一分三而进入三个CPU模块。DA输出控制伺服机构的舵摆角为模拟量,其关机和喷管控制输出为开关量;输出链路为三个CPU模块,均为对外输出。

典型的三模冗余构型的计算机在输出端都配置有一个硬件表决器,一般可通过一块FPGA来实现。表决器的引入构成了一个单点。为了消除单点,可充分利用后续伺服机构的冗余特性。本设计中的三个CPU模块可独立承担表决功能,表决功能可由FPGA软件和DSP软件实现。

2 时钟同步

本文研制的冗余箭载计算机三机同步时钟技术采用了互反馈独立时钟模式,其主要原理是通过FPGA对三机时钟进行同步处理:即三个模块中的每个模块均有一个由独立时钟源产生的时钟心跳,每个FPGA以50MHz的晶振时钟分频产生频率为1kHz、占空比为1:9999的高电平有效毫秒脉冲信号,高电平宽度为0.1μs。三个模块间的毫秒脉冲在交互以后通过三取二表决最终产生一个同步毫秒中断(共有三个),并提供给对应的CPU处理器,同步触发任务处理。由FPGA各自表决而得到的三个毫秒中断同步误差可被控制在ns级,同步过程如图2所示。各个CPU模块以接收到的三路毫秒脉冲信号中的第二路到达信号作为毫秒同步时钟信号,并将其发送给各自的CPU。

图2 毫秒时钟同步过程Fig.2 The process of millisecond clock synchronization

由于飞行控制运算的任务处理均以毫秒为处理节拍,在毫秒中断同步的情况下,三个模块间的飞行控制运算任务需同步向前推进。类似地,对由箭机产生的5ms同步信号进行了相同的处理:为了适应冗余惯性信息的输入、满足后续余度管理的需要,将由三个CPU模块经过三取二表决而产生的多路同源的5ms同步信号分别发送给冗余惯性测量设备,冗余惯性测量设备将其作为基准来进行陀螺加速度计测量信息的采集、打包和RS422数据发送。

此外,在时钟同步处理时,还采取了备份措施。一旦由于某种原因(例如断线)而导致FPGA的毫秒时钟脉冲交互失败,还可以利用DSP软件、通过LVDS总线以1ms的频率完成通信交互反馈,以进行任务级时钟同步。控制输出的典型周期为20ms,在同步时间点刷新输出,不同步性可以控制在μs级别。

3 输入表决

输入表决主要涉及数字量、开关量、模拟量问题。

(1)数字量输入:对于来自冗余惯性测量设备的多路同步通信数据包,首先对传输内容进行校验,校验为错误的数据包直接丢弃。如果校验通过,则对冗余数据包进行后续的一致性比对或表决。

(2)开关量输入:由于开关量是离散信号,分别用A

、B

、C

三个通道符号表示模块序号1、2、3,输入表决可以采用布尔代数表达式Yin

=AB

+BC

+AC

获得。其中,Yin

为三取二表决结果。将8种可能的输入结果进行归并,将离散量的值相加。考虑一度故障时,可能的情况有以下几种:3、2、1、0。①如果结果是3,则所有信号有效为1;

②如果结果是2,则信号为0的通道故障;

③如果结果是1,则信号为1的通道故障;

④如果结果是0,则所有信号有效为0。

(3)模拟量输入:经采样得到的模拟量数据和来自通信数据的模拟量数据均是浮点数类型。在对其进行表决时,首先需要完成三个数据通道的一致性比对,主要采用了基于门限的算法。门限值的设计综合考虑了各通道的不一致性和由输入数据表示的物理量的变化特性。在一定的门限内,模拟量输入均可认为是正确值。

对于某一个实测模拟量s

,i

=A

,B

,C

,系统给定的不一致性门限为ε

(t

)>0。定义三个通道间的不一致偏差为S

=|s

-s

|,i

=A

,B

,C

,j

=A

,B

,C

且i

≠j

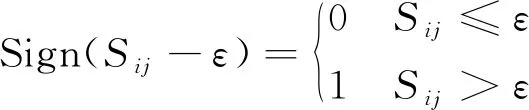

定义符号函数为

三个模块通过数据交互计算不一致偏差,将不一致偏差与门限进行比较并进行余度管理,可得到各自用于飞控计算的数据。

表1中,序号1表示三模冗余模块采用各自的输入值。由于不一致性偏差都在门限内,这些数据都是对真实物理参数的反映。

表1 基于门限的模拟量输出表决Tab.1 Analog output voting based on threshold

考虑到将不一致性偏差的二值化结果定义为不同位权的二进制位有利于软件的实现,定义如下的由三位二进制表示的整数:S

=D

D

D

,其正则化后的结果如表2所示。其中,D

=Sign(S

-ε

),D

=Sign(S

-ε

),D

=Sign(S

-ε

)。

表2 正则化的模拟量输出表决Tab.2 Formalization of analog output voting

4 输出表决

输出信号开关量和模拟量的表决机制与输入信号基本一致。

(1)开关量输出

在三模冗余的CPU模块输出表决的基础上,箭载计算机在输出级采用了五管冗余机制。如图3及表3所示,五个固态继电器输出通道(XYZRS

)并串联冗余构成了输出级的冗余。与常用的串并连冗余或并串连冗余相比,这里所用的五管冗余机制具备两个显著的优点:一方面,其可有效应对由固态继电器短路或断路失效而带来的危害;另一方面,其能够对来自三个CPU模块的控制信号再次进行三取二表决,以确保在一路误判和在一个输出继电器失效的情况下电路功能不被影响。

图3 五管冗余输出结构Fig.3 The structure of output with five redundant solid relays

表3 五管冗余输出真值表Tab.3 Logic truth table of five redundant solid relays

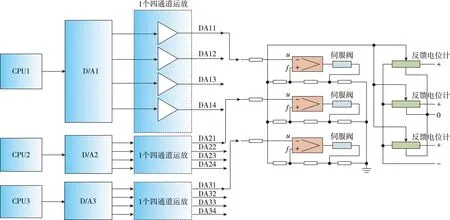

(2)模拟量输出

为了尽量减小伺服机构力纷争的可能,采用与输入不同的方式,对表2中序号1考虑的情况进行调整,即三模冗余模块不再采用各自的输出值,而是统一取中间值。如图4所示,将箭载计算机输出控制三冗余伺服阀的信号统一为由运算得出的中间值。从软件优化角度来看,排序算法的效率较低,且得不到故障通道的信息,在毫秒中断中对数据进行排序的耗时较长。表2序号2~7中的标量在实际算法中选取了中值,所取得的算法与直接对数值s

(i

=A

,B

,C

)进行大小排序、进而选取中间值的计算结果一致。文献[5]所描述的方法为,优先选择序号小的模块。相比文献[5]所描述的方法,本方法更加合理。

图4 伺服控制DA输出示意图Fig.4 The schematic diagram of DA output for servo control

对于结构化的数据向量而言,其无法被直接排序。不一致性偏差定义可以扩展为向量的欧式距离,而欧式距离可进一步与门限进行比对表决。

余度算法采用中间值的优点为,中间值相对保守折中,其与真实值的误差不是最大的一个;同时,将中间值选择和持续的故障计数相结合,可满足拜占庭故障抑制的要求。

不失一般性,假设有s

≤s

≤s

,物理量的真实值为s

,可得s

-s

≤s

-s

≤s

-s

①0≤s

-s

≤s

-s

⟹|s

-s

|≤|s

-s

|;②s

-s

≤s

-s

≤0⟹|s

-s

|≤|s

-s

|5 自检测

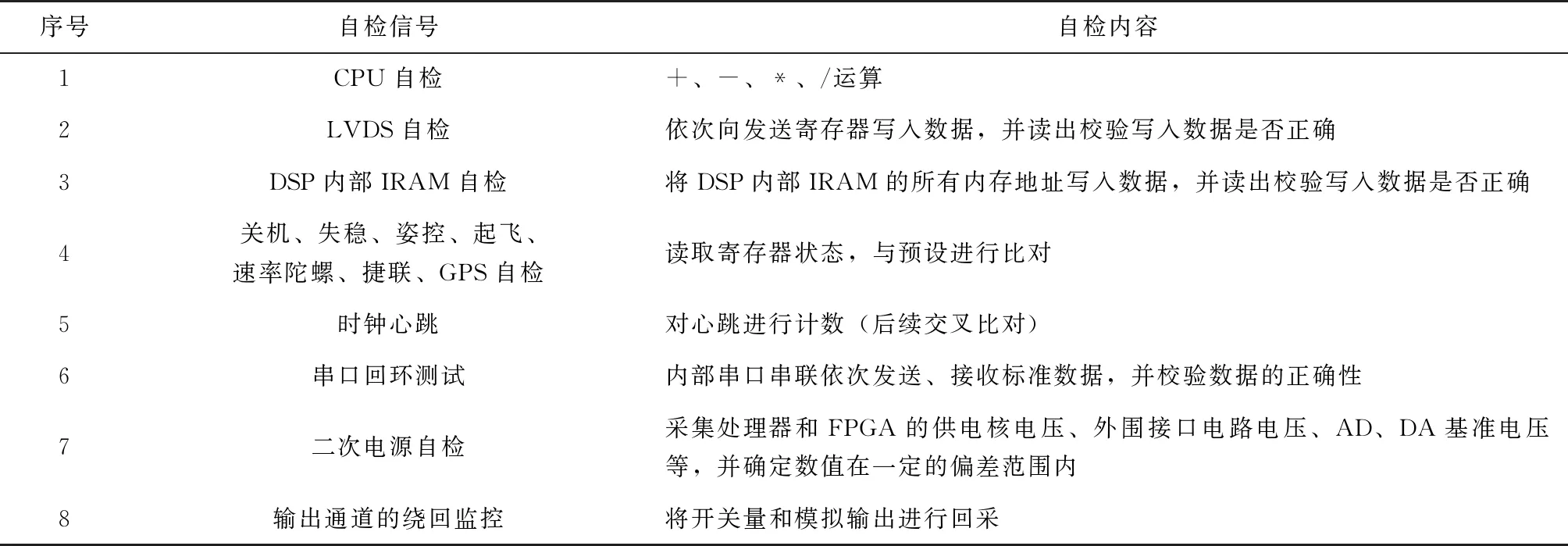

本文研制的冗余箭载计算机采用了BIT自检测技术。一方面,该技术提升了测试覆盖性改进余度设计,验证了门限设计的有效性;另一方面,BIT自检测技术增加了一个维度,参与了余度的管理,改善了表决的合理性。冗余计算机BIT自检测技术可分为3种工作模式:加电启动BIT自检测技术、飞行前BIT自检测技术、飞行中BIT自检测技术。由于运载火箭不可维修,因此无需考虑BIT自检测技术的维护。

加电启动BIT自检测技术的测试内容最为全面,包括了CPU、LVDS总线、DSP内部IRAM、关机信号、失稳信号、姿控信号、起飞信号、串口回环测试、时钟心跳、二次电源测试以及输入输出通道的自检。加电启动BIT自检测技术通过自检为系统建立了一个正常工作的初始基准。

飞行前和飞行中BIT自检测技术为周期性测试,由飞行软件实现。测试安排在飞行计算的空隙进行,测试内容包括LVDS传输、时钟心跳、二次电源和输出通道的监控,如表4所示。

表4 BIT参数表Tab.4 List of parameters of BIT

自检测中的关键参数包括

(1)LVDS传输:三个CPU模块间的输入输出表决均依赖LVDS交叉通信,这对其自检具有至关重要的意义;

(2)时钟心跳:三个CPU模块都拥有自己的独立毫秒中断。飞行控制软件以此为节拍进行计算,时钟心跳作为关键的自检信息参与输入输出的表决,并作为首先被考虑的参数。软件计数比对不正确的原因有可能为晶振失效,FPGA采样计算的毫秒中断不正确,也可能源于软件计算的故障;

(3)二次电源:对DSP和FPGA等核心器件的供电电压、关键外围接口、AD、DA基准电压进行周期采样,监控系统的工作状态;

(4)开关量:开关量保持时间范围为20ms~200ms,如图5中的关机、喷管控制信号。FPGA具备足够的精度,飞行控制软件也有足够的时间裕度将此类信号进行回采。通过将回采信号与由三个CPU表决运算输出的信号进行比对,可有效监控接口器件功能的正确性;

(5)模拟量:模拟量DA输出的更新周期为20ms。如图5所示的回采方式可以充分利用每一个CPU模块的AD通道,将最终的输出回采与CPU表决运算值进行比对。如果比对后的误差在一定门限内,则可监控该模块对应的接口芯片是否正常工作。如果发生了一定程度的漂移,还可以进行对应的补偿,使得三个CPU模块的输出尽可能一致。

图5 控制输出回采示意图Fig.5 The schematic diagram of sampling of control output

6 通道表决

当三个CPU模块的工作均正常时,须对输入输出进行参数表决。当关键特性累计超过故障计数门限时,须对故障通道做进一步处理。选取可表征三个冗余模块正常工作的关键特性,即LVDS交叉传输、时钟心跳计数、控制输出信号,进行模块级表决或通道表决。

(1)LVDS交叉传输需在一定时间内完成,引起传输失败的原因包括:未在约定的通信周期内完成传输;传输的数据校验和未通过。判定通道是否发生故障的标准是:当A通道没有获得其他通道的正常数据的连续次数超过了门限,则认为其他通道故障。无法进行交叉通信,则无法进行后续的参数表决。

(2)通过软件进行时钟心跳计数的交互比对。参照模拟量表决故障计数的规则,当连续超差次数超过门限时,则认为该通道故障。故障的含义为该通道与其他通道不同步。同时,该故障模式在严重到一定程度时,会引起传输时间超差。根据第一条判定原则,该通道将会被其他通道判定为故障,也会导致后续模块间输入输出的表决点不匹配。

(3)控制输出信号按照开关量和模拟量表决故障计数规则,在连续超差次数超门限时,判定该通道故障。

三模冗余CPU模块可对以上三个关键特性独自进行通道表决,由各特性的表决结果得到的故障通道数可能为0、1、2、3。

通道表决流程示意图如图6所示。表决按上述(1)、(2)、(3)的顺序进行,各个通道对交叉传输通路的表决结果可以存在不一致的情况,交叉传输通路表决不会出现故障通道数为3的情况;即使A通道由于交叉传输通路接收通道发生故障而判断B、C通道出现故障,发送通路也并不一定发生故障,所以需要将A通道的输出转发给其他通道。

图6 三模冗余通道表决算法的流程图Fig.6 Flow chart of voting algorithm of triple modular redundancy channels

7 仿真验证

(1)互反馈独立时钟仿真

三模冗余时钟需考虑如下几种故障模式,在Modelsim软件中使用Verilog-HDL对时钟进行建模,验证在某一模块的时钟源发生故障时,互反馈独立时钟是否可以正常工作。仿真结果如图7~图9所示。

图7 1个时钟相位存在偏差Fig.7 One of the three channel clocks with phase error to the others

图8 3个时钟之间的相位均有偏差Fig.8 Every two of the three channel clocks with phase error to the other

图9 1个时钟完全故障Fig.9 One of the three channel clocks totally failed

① 其中1个时钟与其他2个时钟的相位有偏差(毫秒脉冲2相位滞后)

② 3个时钟之间的相位存在偏差(以第二个到来的时钟时刻作为同步输出)

③ 1个时钟完全故障(毫秒脉冲3完全失效,无有效时钟脉冲输出)

上述仿真验证表明,三机冗余时钟设计方式既保证了毫秒中断的同步输出,又能够在某一模块时钟源发生故障时确保模块正常工作。即在三个时钟均正常的情况下三取二表决同步输出,在一个时钟源误差较大或是完全失效时也可正常工作。

(2)通道表决仿真

考虑图6中NF=2的分支故障情况,在正常通信初始状态,人为地在特定时刻将CPU2、CPU3发送给CPU1的LVDS通信使其能禁止,模拟LVDS的交叉传输通信故障,验证通道表决算法的正确性。

将三个CPU通道的表决信息通过测试口下传并进行解析。图10~图12列表显示了LVDS在通信正常和交互异常情况下由各CPU收发的控制输出DA信息。

图10 CPU1通道表决结果Fig.10 Channel voting result of CPU1

图11 CPU2通道表决结果Fig.11 Channel voting result of CPU2

图12 CPU3通道表决结果Fig.12 Channel voting result of CPU3

图10~图12演示了对关键特性LVDS交叉传输故障的冗余表决。3个CPU各自进行了通道表决,CPU1判别出的故障通道数为2,而CPU2、CPU3判别出的故障通道数为0。

图10中,LVDS2_1为CPU1接收CPU2的通道正常标志。第一拍中的2>1_OK表示CPU1接收CPU2通道正常,后续所有时间拍中的2>1_ER 表示CPU1接收CPU2通道异常。CPU交互的数据在第一拍之后出现了通信异常,因此CPU1接收到的其他CPU的数据值均为错误,错误数据可用FF_FF表示。

CPU1接收的CPU2、CPU3的通信链路均发生了故障,并在5拍以后被判别出。此时,CPU1发送功能正常。如图11、图12所示,CPU2、CPU3接收到了正确的信息,对DA输出进行了有效的取中值表决,即为CPU1的输出值。

8 结 论

本文研究了运载火箭三模冗余箭载计算机的余度管理,对CPU模块的冗余配置、通道表决、时钟同步、输入输出信号监控表决、自检测等方面设计了余度管理策略。该余度管理的设计思路在某型箭载计算机工程样机中实现了功能验证,试验表明该方法可有效应对典型的失效模式。

进一步优化的设计工作可以从以下几个方面展开:考虑到运载火箭飞行任务时间较短,在体积、功耗、代价、可靠性限制下针对故障通道设计合理的切断隔离措施,以及针对瞬时计算故障能断电重启;硬件的冗余模块,通过合理选配多个生产厂家器件等方法,提供非相似余度来避免共因失效;软件通过多样化设计,来防护系统性设计错误所产生的共模故障。