低谐次肖特基二极管倍频器研究进展

2021-08-06唐家轩李少甫何婷婷马得原

唐家轩,李少甫,何婷婷,马得原

(西南科技大学 信息工程学院,四川 绵阳 621010)

为拓展太赫兹收发系统的工作频段,进一步地开发和利用太赫兹频谱资源,需要提供一定信号功率和可调谐频率的太赫兹波源。全固态太赫兹倍频源具备结构紧凑、高工作寿命、低直流输入功率等优势,成为了获取太赫兹波的主流方式。在实际应用中,如何产生更高频段、输出功率相对稳定的太赫兹波源一直是研究的难点和重点。

国外一些顶尖研究单位和学者将多个输入输出探针和多个频率倍增结构集成在一张芯片上,通过片上探针将一路输入信号分割成两路信号,并送入片上非线性器件进行倍频,在输出端将倍频后的两路信号组合成一路经波导输出,实现了单个输出频率在1 THz 以上的倍频器[1]。由于国内受到非线性器件的微波在片测试条件、片上集成工艺和输入驱动功率的制约,较为理想的倍频器成果主要集中在太赫兹低频段。为满足太赫兹技术应用中对于高品质频率源的需求,如何研制出更高性能的倍频器受到了更多关注。

固态倍频器常用的非线性器件主要有肖特基二极管和CMOS 管。肖特基二极管具有高截止频率、非线性特性不单一、低噪声等优点广泛应用在倍频器的设计中。此外,随着硅基CMOS 工艺的发展,CMOS 管也显现出它在太赫兹信号源的应用潜力。Turhaner等[2]采用硅锗BiCMOS 工艺制作了一款三倍频器芯片。但受限于CMOS 管的截止频率,当工作频率超过截止频率的一半,器件的性能会急剧恶化,因此目前难以应用到更高频段。本文以肖特基二极管为出发点,归纳了低谐次倍频器设计中存在的研究难点和解决方案,综述了低谐次倍频器设计的几种常用电路结构,并总结了低谐次倍频器在太赫兹领域中的应用场景。

1 肖特基二极管

太赫兹倍频器按照采用的非线性元件可以分为无源倍频器和有源倍频器。在无源倍频器中,阶跃恢复二极管和雪崩恢复二极管常用作高次倍频,异质结势垒二极管受特性限制主要用于三次以上的奇次倍频。肖特基二极管多用于倍频系数小于4 的低谐频变换,因此基于肖特基二极管的二次和三次倍频电路最为常见,其具有宽带、可调谐和温度稳定的优点,成为主流的设计对象。

肖特基二极管具有可变电容和可变电阻两种非线性特性,常根据输入功率幅度和不同指标要求针对性地选取或研制合适的肖特基二极管。二极管的非线性应用是倍频器研制的核心,如何选取或研制合适的肖特基二极管是倍频器设计的关键问题。二极管的非线性电阻过大会造成功率耗散,倍频器的输出功率会恶化,从而影响倍频效率,非线性电阻过小宽带特性会减弱;二极管的非线性电容过小则无法输出一定功率,增大非线性电容有利于增加二极管的功率容量,但非线性电容过大会给倍频器的电路匹配带来巨大困难。不论是阻性或容性二极管都需要折中考虑非线性电阻和非线性电容带来的影响,即阻性二极管在保证宽带匹配的同时要留有一定的功率容量,容性二极管在保证能够输出较大功率的同时要留有一定的匹配带宽。

目前对倍频肖特基二极管的研究有三个方面:(1)探究先进的半导体工艺。例如代鲲鹏等[3]提出了渐变掺杂提高倍频效率的解决方案。采用垂直结构的二极管相比于采用水平结构的二极管更利于实现高击穿电压和更高的功率容量[4]。如图1 所示,Qi 等提出了一种新型肖特基结接触结构[5],该新型结构能够消除肖特基电极边缘附近积累的电荷,同时更好地隔离金属电极与轻掺杂层,消除了电极边缘附近产生的额外电流路径。与采用常规肖特基二极管结构的倍频器进行测试对比,采用新型肖特基二极管结构的倍频器在输出功率上得到显著提高;(2)采用新型材料如多层石墨烯,因具有很强的非线性特性,基于该材料的倍频器能够输出很大的奇次谐波功率。采用砷化铟代替砷化镓,能够提高倍频管的功率承受能力,同时降低倍频管的输入驱动功率;(3)分析以混合材料制成的肖特基二极管的高频寄生效应,如等离子体共振效应、趋肤效应等,建立更加精确的二极管等效电路模型,提高仿真精度,使仿真结果更逼近实测结果。

图1 砷化镓肖特基二极管横截面示意图。(a)新型肖特基接触结构;(b)常规肖特基接触结构[5]Fig.1 Schematic diagram of the cross-section of gallium arsenide Schottky diode.(a) New Schottky contact structure;(b) Conventional Schottky contact structure[5]

2 低谐次肖特基二极管倍频器

2.1 肖特基二极管二倍频器

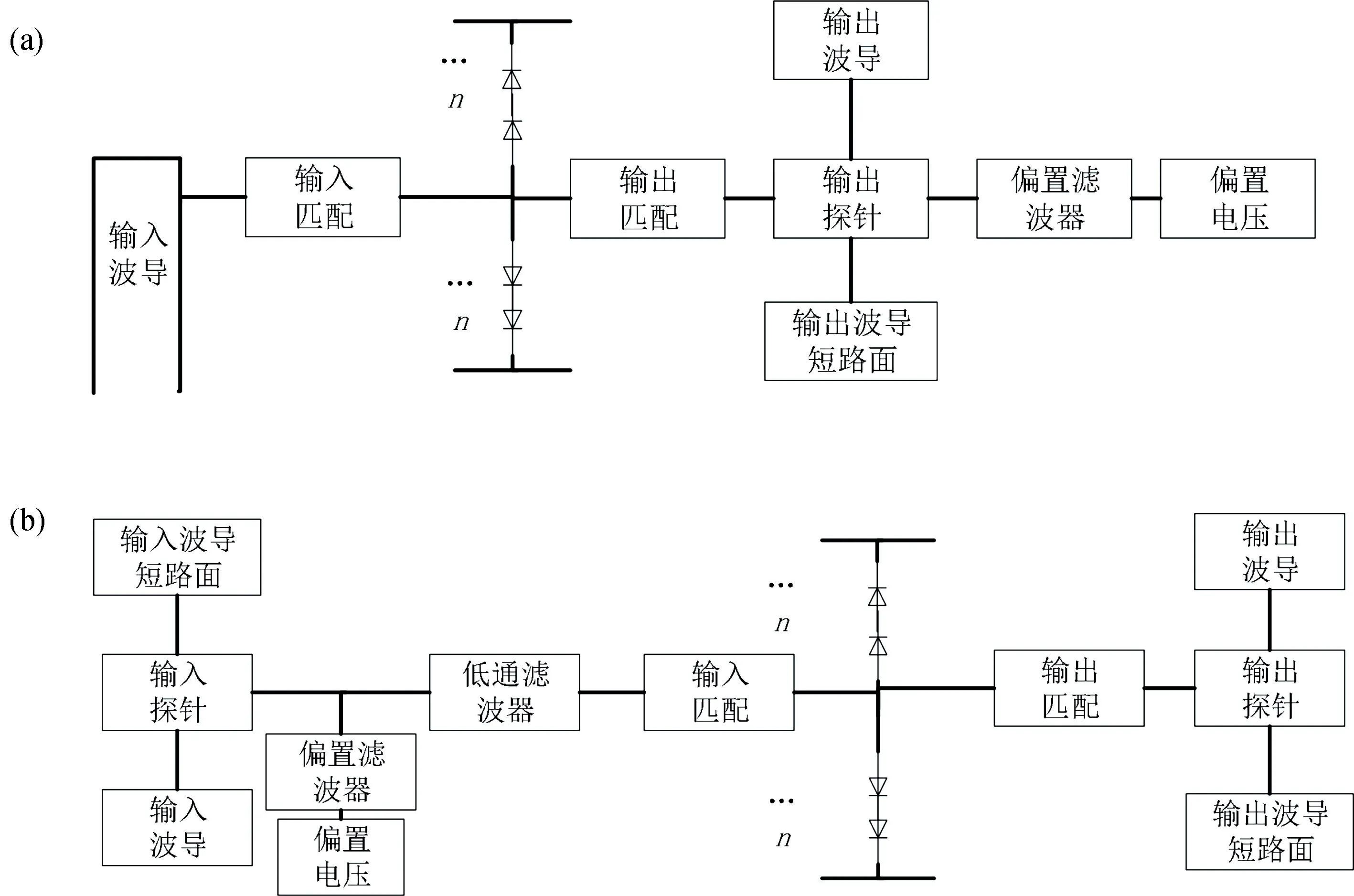

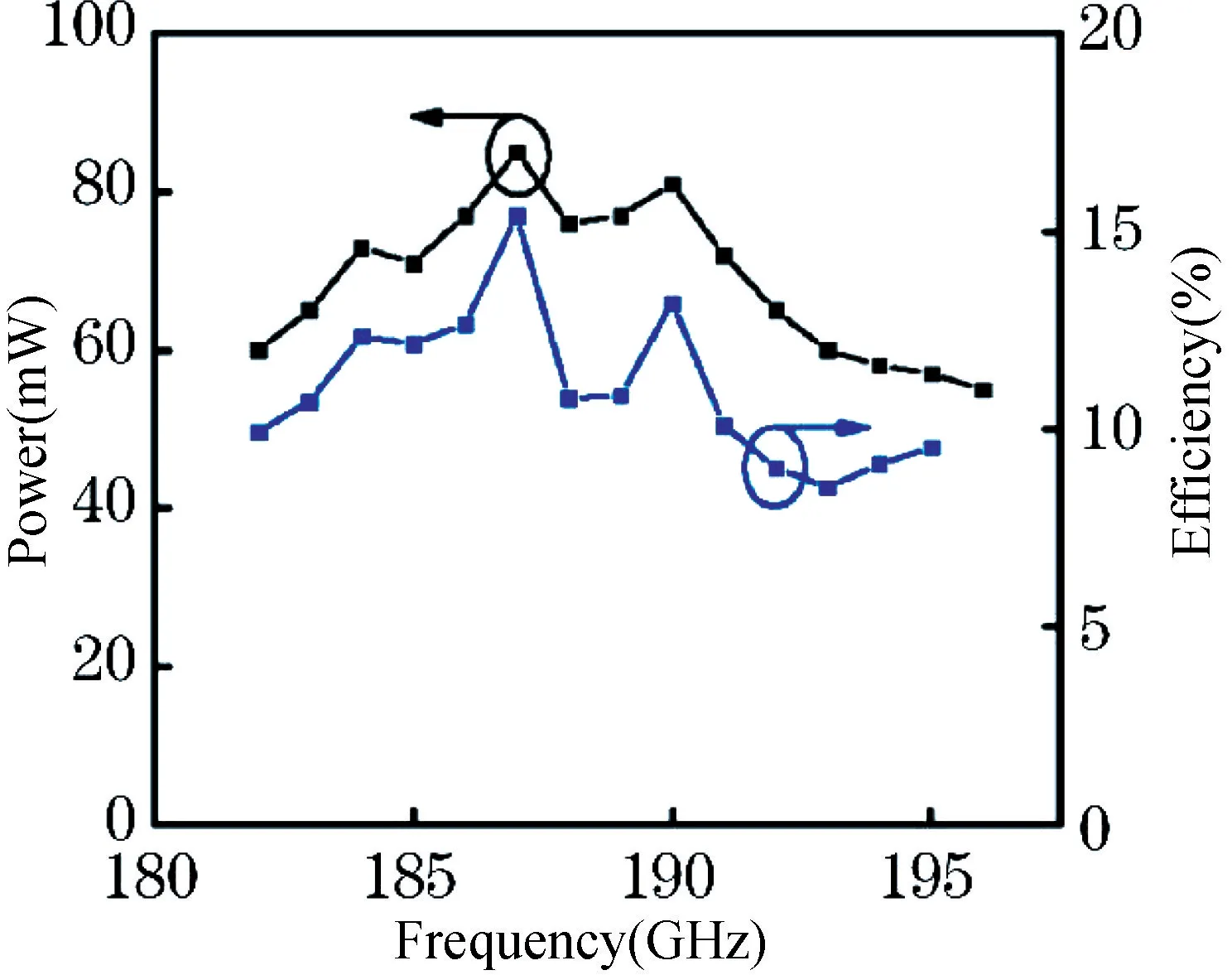

传统意义上,二倍频器电路按照肖特基二极管能否抵消奇次谐波分量可分为两个大类:平衡结构与非平衡结构。早在20 世纪90 年代,Porterfield 等[6]就提出了平衡式二次倍频电路结构。调研了国内外大量二倍频器的实用设计,列出了二倍频器常用的两种平衡电路结构如图2 所示。第一种结构如图2(a),基波信号从波导输入,直接通过调整减高波导的长度和二极管的位置对输入阻抗进行匹配,核心器件采用n对反向串联的二极管,奇次谐波分量被管对抵消,输出匹配电路能够最大化地提取管对产生的二次谐波信号,最后从波导过渡结构输出所需二次谐波信号,直流偏置从二极管序列的中点位置加载,偏置低通滤波器有效地阻止了二次谐波信号在直流馈电端口的泄露。这种加馈电端口和输入匹配的设计大大简化了电路结构,便于加工。在两种平衡结构中,目前第一种应用最广泛。徐鹏等[7]采用此结构设计了一款190 GHz 大功率二倍频器,测试结果如图3 所示。该倍频器在输出频点187 GHz 时,倍频效率达到15.4%,输出功率达到

图2 (a)二倍频器第一种常用平衡电路结构;(b)二倍频器第二种常用平衡电路结构Fig.2 (a) The first commonly used balanced circuit structure of frequency doubler;(b) The second commonly used balanced circuit structure of frequency doubler

图3 190 GHz 二倍频器输出功率和效率测试结果[7]Fig.3 Measured output power and efficiency of 190 GHz frequency doubler[7]

85 mW。

第二种结构如图2(b)所示,不同于第一种结构的是,选择在二极管一侧低通滤波器前端的位置开口设置馈电电路。偏置滤波器的作用是防止输入信号进入馈电端。采用这种结构,馈电端离输入波导距离较近,相比于第一种结构会带来微组装的困难。Liang 等[8]采用这种结构设计了一款180 GHz 二倍频器。该倍频器核心器件采用以SiC 作为基底的GaN 二极管,二极管的反向击穿电压为15.4 V,并且该二极管本征截止频率达到了459 GHz。将二极管倒扣在石英玻璃电路上,构成平衡二倍频器。实测性能显示输入功率为2 W 时,在177~183 GHz 频段,二倍频器的输出功率高于200 mW,倍频效率为9.5%~11.8%。由于GaN 肖特基二极管模型不够精确和二极管串联电阻过大,限制了该二倍频器的输出功率和倍频效率。

2.2 肖特基二极管三倍频器

传统意义上,三倍频器电路按照肖特基二极管(多管)能否抵消偶次谐波分量可分为两个大类:平衡结构与非平衡结构。也可先按照电路是否加馈电端,再结合肖特基二极管功能,可将三倍频电路结构细分为四类,即平衡加馈电、平衡不加馈电、非平衡加馈电、非平衡不加馈电。

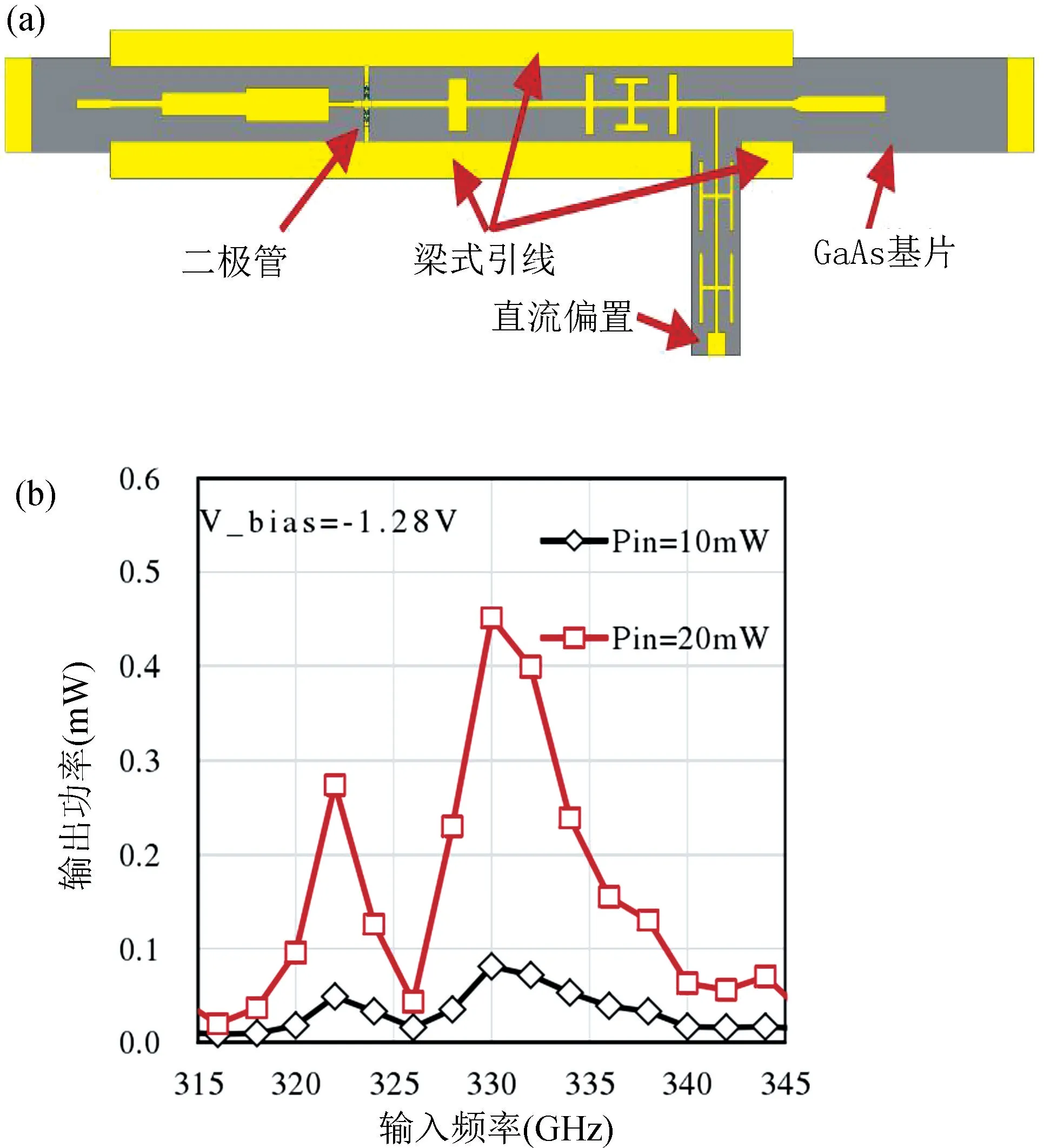

调研国内外大量文献后,本文列出了三种常用的加馈电的三次倍频电路结构如图4 所示。三种加馈电的结构在容性倍频和阻性倍频中均有应用,即通过给二极管加载偏置电压,获得更高输出功率,从而提升倍频效率;这三种形式馈电端所加位置各不相同。当采用反向并联的二极管对以串联形式接入电路时,二极管两端不存在接地情况。采用这种管对接入方式与二极管两端接地的情况相比,散热效果会变差。第一种结构如图4(a)所示,在输入过渡结构和低通滤波器之间的传输线上开口,加偏置电路。这种方式在二极管序列的中点位置施加激励,加工和微组装工艺不存在太大问题,国内外都能实现,功率分配均等,散热效果较好。电子科技大学的吕肖林采用这种结构设计了一款单片集成式三倍频器[9],三倍频器电路如图5(a)所示,图5(b)展示了该倍频器的实测数据。采用图4(a)和图2(b)这两种结构会出现两个问题:一是若偏置电路采用独立基片,需要通过金丝键合将其与二极管电路连接,会引入不确定性;二是若二极管电路基片较薄,悬置微带线下方是空气,很容易将基片压裂,这种情况在高频倍频下较为常见。可以从悬置微带线的开槽口将基片伸出一个枝节来搭载直流偏置滤波电路,即将整个电路基片做成异形,能够避免底部悬空的基片在金丝键合过程中带来的风险。

图4 (a)第一种加馈电三倍频结构;(b)第二种加馈电三倍频结构;(c)第三种加馈电三倍频结构Fig.4 (a) The first type of feeding triple frequency structure;(b) The second type of feeding frequency triple frequency structure;(c) The third type of feeding triple frequency structure

图5 (a)单片集成三倍频器单片电路;(b)单片集成三倍频器输出功率测试结果[9]Fig.5 (a) Monolithic integrated frequency tripler monolithic circuit;(b)Measured output power of monolithic integrated frequency tripler[9]

第二种结构如图4(b)所示,在二极管一侧附近的传输线开口位置加载偏置电压,为了隔离接地和馈电端,需要加旁路电容。这种方式会引起对称二极管之间幅度和相位的不平衡,同时提升了对加工工艺和微组装工艺的要求。这种方案在国外较为成熟,但对国内的加工和组装工艺来说具有一定的难度。Tang 等[10]和Thome 等[11]采用在二极管两侧的开口位置均施加偏置电压的方法,消除了二极管之间引入的不平衡效应,改善了倍频电路的性能。Tang 等对比了在二极管一侧开口位置加偏压和在二极管两侧开口位置加偏压的两种情况,并根据两种情况设计了两款840 GHz 三倍频器,如图6 所示。仿真结果表明,根据后一种情况设计出的三倍频器较前一种情况,其倍频转换效率和输出功率均得到了提高。

图6 两款840 GHz 三倍频器单片电路[10]Fig.6 Two 840 GHz frequency tripler monolithic circuits[10]

电子科技大学的高欣[12]采用了如图4(c)和图4(a)所示的倍频结构,并分别设计了两款110 GHz 三倍频器,这两款倍频器分别命名为A1 和A2。固定相同输入功率下,对两款倍频器施加偏压,实测结果显示在同等偏压下,A2 的倍频效率明显优于A1 的倍频效率。图4(c)所示第三种结构较图4(a)电路结构更容易实现,馈电电路加在基波输入电路另一端,两块电路共用同一块基板,省去了金丝键合,减小了键合工艺的不确定性。根据实测结果,相比于A2 倍频器,A1 倍频器电路结构会增加馈电端与二极管之间的距离,直流信号的损耗会增加,输出功率和倍频效率会受到一定程度的影响。

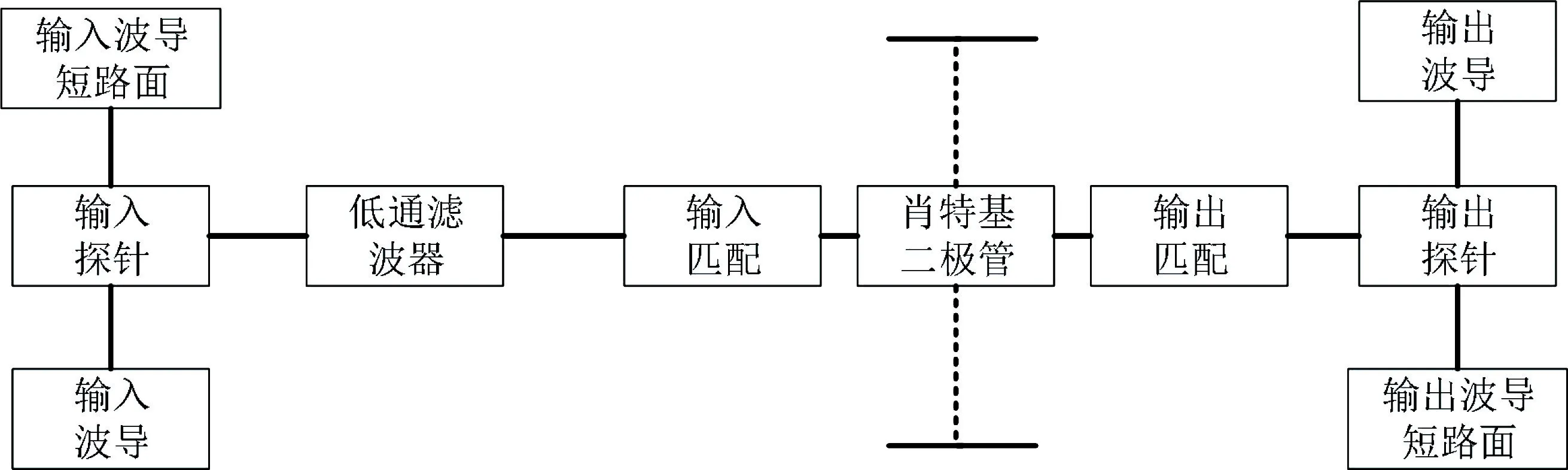

不加馈电的平衡与非平衡结构在阻性倍频和容性倍频中均有应用。调研国内外大量文献可知,不加馈电的三次倍频结构如图7 所示,输入基波信号经过渡结构和匹配滤波后以较低的损耗进入二极管,用匹配过渡结构最大化地提取三次谐波分量,整体电路结构简单,制作在同一基片上便于加工。中国工程物理研究院李理等[13]采用这种结构设计了一款宽带三倍频器,该三倍频器的输出带宽达到了100 GHz。输入信号功率10 mW 时,在410~510 GHz 频段内输出功率大于50 μW,最大输出功率105 μW;王俊龙等[14]采用这种结构并结合单片集成工艺设计了一款430 GHz单片集成三倍频器,在基波输入功率5 mW 的条件下,测试结果如图8 所示。该结果显示在430 GHz 处测得输出功率为215.7 μW,这款单片集成倍频器的性能在国内处于领先水平。

图7 不加馈电的平衡与非平衡结构Fig.7 Balance and non-balance structure without feed

图8 430 GHz 单片集成三倍频器实测结果[14]Fig.8 Measurement results of 430 GHz monolithic integrated frequency tripler[14]

3 低谐次倍频电路设计难点

三倍频器平衡电路相较于非平衡电路,由于要回收利用二次谐波,基片长度往往会增加。低频段电路往往采用混合集成形式,在基片有一定厚度的情况下,基片的长短问题不够突出,但在单片集成形式倍频电路中这一问题要引起足够的重视,基片过长会影响其切割成品率,还会在实际电路中引起额外的损耗,更容易造成折断和损坏,应将电路长度限制在一定范围内。

高频段单片集成电路的装配也成为不可忽视的问题,用导电胶固定基片会引入较大误差。采用梁氏引线和热压金属键合相结合的办法,即利用无银胶电路封装工艺可以大大降低单片电路装配的困难度和误差。此外,高频段倍频器电路传输线选择并不单一,除应用最广泛的微带线外,电子科技大学的纪东峰[15]采用共面线设计了一款三倍频器,通过仿真软件查看两种传输线的场分布,发现当二极管横向放入共面波导时会有更多功率馈入管芯内部。在这种设计场景中,虽然共面波导单位传输损耗比悬置微带线稍大,但是采用共面波导能够提高管芯利用率。

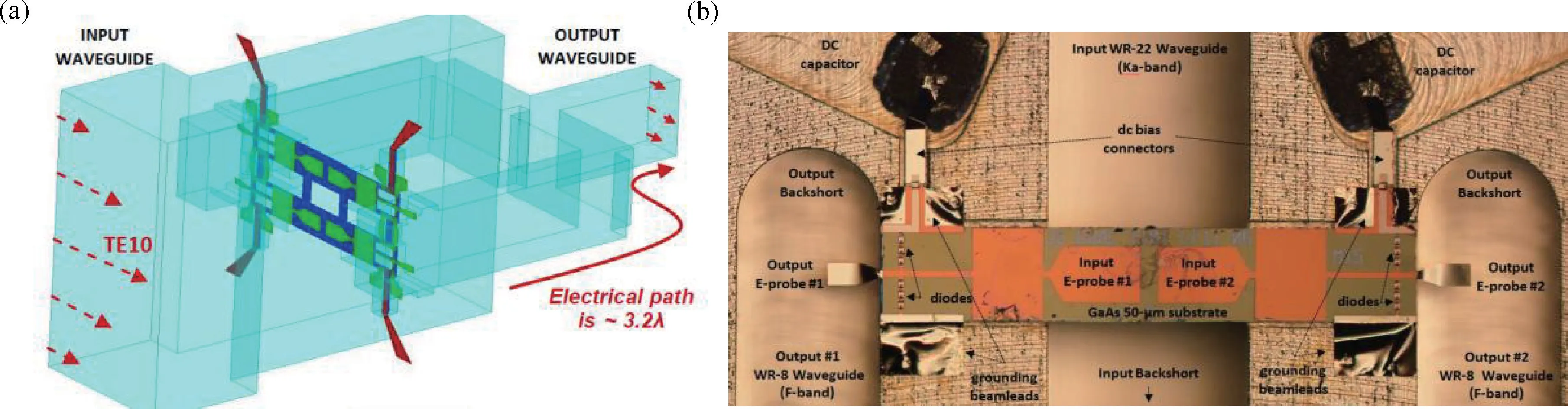

一旦选定或研制出倍频管,设计出合理的电路拓扑结构使二极管工作在最佳状态是决定倍频器性能好坏的最后一道保障。基于肖特基二极管的电路结构不应该局限于上述几种常用倍频结构,而趋于灵活多变。如图9 所示,Viegas 等[16]展示了双“Y”型功率组合倍频电路结构,通过两个E 平面到H 平面的波导过渡将单个倍频芯片输出处的电场旋转90°,最后利用H平面组合器来实现功率倍增。该倍频器输入1 W 功率时,在180 GHz 能提供200 mW 以上的功率。图9 所示的功率合并技术中,需要使用波导功率合并技术合并不同的芯片,这样会增加信号的电气路径和额外衰减。Siles 等[17]提出了一款单“Y”型功率组合倍频器,该倍频器的整体电路结构如图10 所示,输入波导的两个或四个探针同相均分输入功率,经多个二极管产生的输出功率在输出端重新组合,采用MMIC 光刻技术将主体电路制作在一张芯片上并且整个电路的对称性较好。该设计可避免图9 所示的功率合并技术中存在的额外损耗。

图9 多芯片功率组合倍频器的组装示意图。(a)上半部分;(b)下半部分[16]Fig.9 Assembly diagram of multichip power combination frequency multiplier.(a) The upper half;(b)The lower half[16]

图10 (a)单芯片功率组合倍频电路结构;(b)功率组合倍频电路内部单片[17]Fig.10 (a) Single chip power combination frequency doubling circuit structure;(b) Single chip inside the power combination frequency doubling circuit[17]

4 肖特基二极管倍频器的应用

肖特基二极管倍频器作为实现稳定太赫兹波源的重要手段,是太赫兹系统的重要组成部分。Siles 等[17]提出的肖特基二极管倍频器,能够用来构建新一代紧凑阵列接收机,完成天体物理学和行星科学任务。为提高天气预报准确性,监测极端天气现象,需要设计太赫兹频段被动遥感仪器,大功率源是该仪器接收前端研制的基础。孟进等[18]基于功率合成技术研制了一款166 GHz 大功率源,该功率源可正常驱动遥感仪器,完成探测冰云粒子尺寸和形状分布的任务。倍频器不仅可用于星间探索和大气探测,还可以有效应用于太赫兹辐射计成像系统,该系统能够探测到微小目标和隐身目标,具有重要的工程应用价值。倍频器常与谐波混频器、功率放大器等其他器件配合使用,在太赫兹通信、军事等各相关领域发挥着重要作用。

5 结论与展望

低频段二倍频器和三倍频器的设计在国内外日趋成熟,如何设计出适用于更高频段和能够输出更高功率的倍频器成为研究人员关心的问题。随着半导体工艺和集成电路技术的不断成熟,需要关注肖特基二极管和电路拓扑结构。探究二极管制作的新材料和新工艺,提高二极管工作性能是目前研究的热点。针对电路结构设计中功率损耗大、加工和装配难、输出功率低等问题,本文归纳了几种解决方案。探究新的电路拓扑结构,实现倍频器更高性能是未来的研究重点。

肖特基二极管倍频器的研究正迈向一个新的高度,虽然在低频段内已有许多研究,但高频段倍频管的研制和电路拓扑结构的设计仍是亟待解决的问题。提高肖特基二极管倍频器的性能和功率处理能力是未来太赫兹固态源的发展方向。