一种100 G EPON系统RS编码器设计与实现

2021-04-19杜慧敏张英杰张丽果

杜慧敏,张英杰,张丽果

(西安邮电大学 电子工程学院,陕西 西安 710121)

以太网无源光网络(Ethernet Passive Optical Network,EPON)在物理层采用无源光网络(Passive Optical Network,PON)技术,在链路层使用以太网协议,利用PON的拓扑结构实现了以太网的接入,具有低成本、高带宽、扩展性强、灵活快速地服务重组、与现有以太网兼容以及管理方便等特点,成为宽带接入网一种有效的通信方法。

受4K/8K超高清视频、虚拟现实和智慧家庭等市场应用的强烈驱动,用户带宽以每年50%的速率增长[1],当前主流的10 G EPON技术越来越无法满足市场需求,高带宽、高稳定性的100 G EPON技术将成为未来全球超带宽产业中的主要光接入网技术[2]。

为了检测和纠正通信过程中信息发生的错误,在通信系统中常用前向纠错码(Forward Error Correct,FEC)技术来保证通信的质量。在FEC的码类中,里德-所罗门(Reed-Solomon,RS)编码是一种纠错能力较强的线性分组码[3]。RS编码是基于有限域伽罗华域(Galois Field,GF)的码组,其所有的校验码符号均取自伽罗华域,编码中所有运算都在伽罗华域中进行。RS码由于其编码相对简单、编码结构稳定性强,纠错能力强等特点[4],被广泛应用于高速数字通信系统中,以满足数据通信可靠性的要求[5]。

通常使用RS(n,k)表示不同纠错能力的RS码,其中n代表码长符号的数目,k代表待编码数据单元(Code Word,CW)符号的数目,n、k之间的差值越大,纠错能力就越强。电气与电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)802.3-2015版标准使用RS (255,223)作为10 G EPON的纠错码标准。而对于100 G EPON系统,IEEE并没有规定需要采用的FEC纠错码类,通常采用RS码或者低密度奇偶校验(Low Density Parity Check Code,LDPC)码。

从100 G EPON系统实现上来看,目前主流的方法是采用4个25 G EPON子系统来构建100 G EPON系统。在国际标准中尚没有明确规定25 G EPON系统纠错码标准,文献[6]建议在25 G EPON系统中依旧采用RS编码作为纠错码,通过分析不同n、k值的RS码在25 G EPON系统中的性能,从编码效率、冗余度、码长和连续纠错能力等4个方面综合考虑,发现选用RS(1 023,847)码作为25 G EPON系统的前向纠错码时,可以在不影响系统传输速率的情况下达到最优的编码增益。

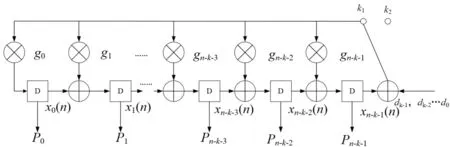

在RS编码算法和编码器设计上,线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)可以直接实现串行编码,但是,这种做法采用串行处理的做法,需要将待编码的数据符号依次串行移入编码电路,处理周期较长、计算效率低,不能满足高速通信系统的要求[7]。针对这一问题,采用并行方式实现RS编码器是主流的方法,2013年,文献[8]借鉴文献[9]提出的高速循环冗余校验码(Cyclic Redundancy Check,CRC)并行编码方法,将该方法用于并行RS编码,实现了灵活性更强、可用于并行编码计算的RS(255,223)编码器,满足了10 G EPON的系统要求。2015年,文献[10]实现了一种编码利用率更高的RS(624,k)编码器(615 从目前的研究看,还没有一种通用的RS编码器并行设计及实现方法。另外,在现场可编程逻辑门阵列(Field Programmable Gate Grray,FPGA)中实现100 G EPON RS编码依然面临巨大的挑战,即单通道编码器最高工作频率要达到390.625 MHz,以保证最高数据吞吐率达到25 Gbit/s。 拟提出一种100 G EPON系统RS编码器设计与实现方法。由4路数据传输速率为25 Gbit/s的通信子系统构成100 G EPON通信系统。选用适用于25 G EPON通信系统并且性能更好的RS码组作为子系统编码器的码型。通过分析RS编码器的n、k等参数以及待编码数据的特性,求出编码电路的并行系数,计算RS编码器的并行度。合理选择RS编码器的并行度并利用多路切换技术、数据并行化计算等方法,设计一种可用于100 G EPON通信系统的RS编码器。 RS码为定义在有限域GF(2m)上的线性分组码[13],其中m为该码组的符号宽度,其对应的生成多项式为 其中,ai为对应伽罗华域中的第i个元素,2t为n与k的差值。 待编码数据的信息多项式为 d(x)=dk-1xk-1+…+d1x+d0 其中,dk-1,…,d1、d0表示k个符号的待编码数据。 不同码型的RS码组其生成多项式也不同[14]。用生成多项式g(x)除x2td(x),商式记为Q(x),余式记为r(x)。计算过程可表示为[15] 余式r(x)即为RS(n,k)编码的校验多项式,余式r(x)可以表示为 r(x)=rn-k-1xn-k-1+…+r1x1+r0 其中,rn-k-1、…、r1、r0表示生成的n-k个符号的校验码。 待编码信息多项式与RS编码校验多项式共同构成码组多项式[16]c(x),其表达式为 c(x)=x2td(x)+r(x)=dk-1xn-1+…+ 经典RS编码器[17]通常采用除法方式实现编码过程,其编码器主要采用一组线性反馈移位寄存器(Linear Feedback Shift Register,LFSR)。经典RS(n,k)串行编码器的电路结构示意图如图1所示。其中,g0、g1、…、gn-k-1为生成多项式g(x)的系数,dk-1、…、d1、d0为编码器的输入数据符号,x0(n)、x1(n)、…、xn-k-1(n)为n时刻各个寄存器的状态值,P0、P1、…、Pn-k-1为该编码电路计算k个周期后编码的结果,即n-k个校验符号。 图1 经典RS串行编码器结构 RS串行编码器电路包括3个工作过程。首先,开关调至k1,将k个数据符号dk-1、…、d1、d0串行移入电路中。一旦所有的数据符号全部移入电路中,寄存器n-k个状态值x0(n)、x1(n)、…、xn-k-1(n)就构成了RS校验码。其次,将开关调至k2,以关闭反馈连接。最后,移出n-k个校验符号到信道中。这n-k个校验符号与之前的k个数据符号共同构成了一个完整的码字。 可以看出,该串行编码器每次只能处理1个输入符号,编码时延为k个周期。该串行编码每个时钟周期处理的符号数有限,制约了编码器的计算效率,不符合高速系统的性能要求[18]。采用串行方式实现的RS编码器,由于其编码效率低、编码周期长等缺点,限制了其应用范围[19]。 文献[20]最早使用状态空间的方法处理并行CRC编码的问题,之后有大量文献使用了相同的方法研究不同使用情况下的CRC并行编码问题。CRC码与RS码都属于循环码,编码原理相同,都可以使用LFSR进行编码,这就决定了也可以使用状态空间这一方法来解决RS码的并行化编码问题[21]。 采用状态空间的方法重新描述上述LFSR的工作原理,串行RS编码电路时刻n寄存器的状态可以表述为 (1) 其中:x0(n)、x1(n)、…、xn-k-1(n)表示时刻n每个寄存器的状态,在下一时刻n+1,寄存器的状态按照式(1)更新;m(n)表示n时刻移入电路的数据符号,所有寄存器的初始值均为0,时刻0时进入寄存器序列的消息符号为m(0),时刻0结束时寄存器的状态为x(1),以此类推,时刻1移入编码电路的数据符号为m(1),时刻n-k-1移入编码电路的最后一个数据符号为m(n-k-1),该时刻结束时寄存器序列里的值即为校验码数据。 若将其生成多项式系数组成的矩阵记为G,生成多项式系数与常量组成的方阵记为F,那么式(1)可以表示为 x(n+1)=Fx(n)+m(n)G (2) 为了得出并行编码的算法,只需要对式(2)进行超前递推即可,递推的层数决定了并行编码的符号宽度。根据式(2),可以推导出q个数据符号并行RS编码的计算表达式为 x(n+q)=Fqx(n)+m(n)Fq-1G+ (3) 由于g0、…、gn-k-1等系数可以预先计算出来,意味着式(1)中F与G就是确定的,可以在RS编码计算前提前计算出来。式(3)可以同时处理并行q个数据符号,于是就实现了并行编码处理。 针对不同的应用场景,用RS并行编码电路的并行度来衡量其编码效率[22]。将编码器理论上需要同时处理的数据符号数定义为编码电路并行系数,实际上需要处理的数据符号的个数定义为编码电路的并行度。并行系数理论上可以是任意正数,但并行度一定是正整数。 设RS(n,k)编码器的数据符号位宽为m,编码器的输入数据位宽为Bw,CW的更新周期为Tcw个时钟周期,则Tcw与m、n以及Bw之间的关系可以表述为 (4) 为了在Tcw个周期内处理完k个数据符号,需要计算出每个时钟周期电路需要处理的符号数,即电路的并行系数,其计算表达式为 (5) 电路并行系数θ可以是任意的正数,但是在电路实现的时候,并行度只能是整数,因此,将并行系数θ向上取整,得出编码电路并行度β的取值范围为 (6) 虽然并行度越大,编码电路可同时处理的数据符号就越多,越有利于提高编码电路的计算效率[23],但是,由于β只是对并行系数θ向上取整,并不等于并行系数,采用β作为电路并行度的编码电路,需要计算出实际的编码计算周期,编码计算周期的计算表达式为 (7) 与使用Tcw相比,采用Tencode作为编码周期会造成不同程度的周期浪费,并且β的值越大,浪费的周期数越多。在实际的操作过程中,β的上界受输入数据的时序关系或编码电路可用资源数的制约,往往存在有一个界限。 由式(6)可得编码电路最小并行度为 (8) 更大的并行度意味着更大的电路面积,因此,在资源受限的情况下,选择最小并行度βmin作为RS编码电路的最优并行度,可以使电路占用最小的硬件资源。另外,电路选择最小并行度βmin进行并行化编码计算,以满足输入数据的时序要求,最大程度地减少编码计算浪费的周期数,提高编码效率。 由4个数据吞吐率为25 Gbit/s的通信子系统构成100 G EPON通信系统。100 G EPON通信系统的结构示意图如图2所示,光线路终端(Optical Line Terminal,OLT)设备承载4个OLT子通信系统,每个OLT子系统通过光分配网(Optical Distribution Network,ODN)与光网络单元(Optical Network Unit,ONU)设备相连,构成4个25 G EPON子通信系统,从而组成100 G EPON通信系统。 图2 100 G EPON通信系统结构 根据电气与电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)802.3-2015等相关协议,在Intel Stratix 10系列的1SG280LN2F43 FPGA芯片上实现4×25 G EPON系统对RS编码器的处理能力有着如下的要求。 1)在数据接口宽度为65 bit的条件下,编码器的工作频率需大于390.625 MHz,以满足子系统25 Gbit/s的数据吞吐率要求。 2)在CW的更新周期为158个时钟周期的条件下,编码器需要具备高速数据的处理能力。 3)FPGA芯片需要承载4个EPON系统,分配给单路编码器的芯片硬件资源有限,经计算,单路编码器硬件资源占用最大值为板级资源的3%,因此,需要在有限的资源上实现该编码器。 实现的25 G EPON子通信系统中RS编码器的输入是65 bit位宽的数据,码组类型为RS(1 023,847),数据符号位宽m为10 bit。利用式(4)和式(5),得到CW的更新周期Tcw为158个时钟周期,并行度系数θ为5.36,因此,选择的最优并行度βmin为6,即编码器可在一个时钟周期内并行处理6个数据符号。由于电路并行度βmin只是接近并行度系数θ的最小整数,并且根据式(7)可以计算出,编码器实际的计算周期为142个时钟周期,与Tcw(158个时钟周期)相比较,存在16个时钟周期的浪费。 在确定电路并行度βmin后,根据式(3)可得出6倍并行编码电路的推导公式为 x(n+6)=F6x(n)+m(n)F5G+ (9) 根据上一部分的并行算法设计RS(1 023,847)并行编码器电路架构。编码器电路由数据输入与输出电路和编码电路核心计算模块组成。编码器整体架构示意图如图3所示。 图3 并行编码电路架构 2.3.1 数据输入与输出电路 编码器需要适用于25 G EPON通信系统,需要满足系统的高数据吞吐率的要求,为此,编码器电路架构采用多路切换技术的采用乒乓电路结构。与不采用乒乓结构的电路相比,在相同电路时钟频率的条件下可以达到2倍的数据吞吐率。其电路内部包括2套相同的子编码电路,输入数据以CW为单元,缓存单元为异步先进先出存储器(First in First Out,FIFO),经过乒乓电路中的输入仲裁写入两个缓存单元“fifo_in”,其不但要满足跨时钟域条件下数据的存储,保证数据不丢失,而且还要满足最大程度上节省电路资源的要求,为此,经过实验发现,将输入缓存深度设为128最为合适。 数据从缓存单元分别进入两个子编码电路进行编码计算,编码完毕后,写入缓存深度也为设置为128的缓存单元“fifo_out”,深度的选取与输入缓存的深度选取原则一致,数据在乒乓电路的输出仲裁下,分别从缓存中相互切换的输出。 编码电路的外部输入数据的写时钟为系统时钟,其频率为390.625 MHz。由于编码器采用乒乓操作,则编码电路内部只需采用工作频率为195.312 5 MHz的时钟即可满足系统需求,实现了低速模块处理高速数据流的功能。 2.3.2 核心计算模块 编码电路核心计算模块主要包括位宽转换模块、编码计算模块等。 位宽转换模块对输入数据进行并行化处理。本文设计采用RS(1 023,847)码组,一个CW中有效数据周期持续130 个时钟周期,数据位宽为66 bit。该模块首先将66 bit有效数据的最低位去掉,形成130个时钟周期位宽为65 bit的待校验数据,由于每个CW中实际待校验数据为8 450 bit,因此,在其之后添加20 bit的“0”,构成8 470 bit即847 个数据符号的待校验数据。之后,将数据进行6路并行化处理,每路一个10 bit符号的数据输出。 编码计算模块的设计基于式(9),核心计算模块架构示意图如图4所示。 图4 核心计算模块架构 该模块由编码模块“encoding”以及位宽转换模块“RsTransform_66”模块组成。编码模块根据选择的最优并行度βmin设计,“encoding”模块中电路主要负责并行度为6的编码计算,即按照每个时钟输入6个数据符号进行计算,其中状态寄存器主要计算每个周期更新的状态x(n)。在进行编码计算时,每个周期内,并行输入的6个数据符号分别与乘法运算模块F5G、F4G、F3G、F2G、FG和G进行伽罗华域乘法运算并相加,记为结果1,另外,将乘数F6与当前时刻状态寄存器中的状态值x(n)进行伽罗华域乘法运算,其结果记为2。将结果1与结果2相加,并将和反馈给状态寄存器x(n),作为下个计算周期的初始状态值。如此,即实现了并行6 路编码计算。该计算过程总共需要142 个计算周期,计算结束时,所获得的176 个状态即为校验码字,由状态寄存器输出,完成编码计算过程。 计算出的RS校验码为176 个校验符号的数据格式,每个符号位宽为10 bit,与编码器外部的数据位宽66 bit不匹配,为此,将数据输入至编码位宽转换模块“RsTransform_66”,经过添加同步头数据和补零操作,将其转换为每个时钟周期66 bit的数据格式输出。 使用Matlab 2012b软件仿真编码算法,利用Modelsim软件仿真电路软件,采用Quartus Prime Standard Edition 18.1软件与Intel 1SG280LN2F43 FPGA 芯片实现电路。 为了验证编码器的功能正确性,可对比算法仿真结果与硬件电路仿真结果的差异。 为了方便对比二者的结果,在待编码的CW中构造全“1”的CW,即该CW由8 450 bit全“1”构成。 由于采用的是RS(1 023,847)码组,在算法仿真与硬件仿真中的CW为8 470 bit,因此,需要在事先提供的8 450 bit数据后添加20 bit的全“0”数据,构成8 470bit的待编码信息。 在进行Matlab编程时,首先输入RS(1 023,847)码组的生成多项式,之后输入由8 450bit全“1”数据以及20 bit全“0”数据构成的CW,得出经Matlab计算的编码结果如图5所示,其中校验码符号以十进制数来表示,高符号位数据处于每一行的左侧。在进行硬件仿真时,利用Verilog语言,基于Modelsim仿真软件,CW的构造也由8 450 bit全“1”数据以及20 bit全“0”数据构成,硬件仿真的部分结果如图6所示,由于校验码符号过多,因此只显示了部分低符号位的校验码符号与第174至175符号位的校验码符号。 对比算法仿真与硬件仿真的结果可以看出,两者的RS(1 023,847)编码结果相同,表明硬件电路的逻辑功能正确。 图5 Matlab编码仿真结果 图6 Modelsim编码仿真结果 利用基于Stratix10芯片的逻辑综合工具对设计的编码电路进行综合,得出该编码电路最高时钟频率已经达到390.625 MHz,表明该电路可以满足25 G EPON子通信系统对编码器在时钟频率上的要求。 另外,对本编码电路的资源消耗数进行分析。由于本电路基于的FPGA芯片的基本单元库为可编程逻辑单元(Adaptive Logic Module,ALM),每个ALM包括1组查找表、2个寄存器、2个加法器和一些其他布线。编码模块的逻辑资源消耗以ALM为单位来表示。根据编码模块综合结果可以得出,编码模块的总资源占用为17 884个ALM。而Stratix10芯片可用的ALM数为933 120个ALM,25 G EPON子通信系统给RS编码器分配的资源占用率为3%,所提设计电路的资源占用率为1.91%,符合25 G EPON子通信系统的要求,也符合100 G EPON通信系统的要求。 将所提设计的RS(1 023,847)编码电路与10 G EPON通信系统中所采用的RS(255,223)编码电路的性能进行对比,对比结果如表1所示。 表1 两种RS编码器的性能对比 从上述对比结果可知,所提设计的编码电路具有更大的数据吞吐率,可应用于更高速的通信系统,纠错能力更强,几乎是RS(255,223)编码器纠错能力的7倍,在相同的误帧率情况下,设计的编码电路可以带来更高的编码增益,并且,编码电路的最大时钟频率也大于RS(255,223)编码器的最大时钟频率。设计的编码电路在性能方面具有非常明显的优势,在资源占用方面,仅仅为RS(255,223)编码器的10倍,相对而言,设计的编码电路具有更加良好的性能。 在FPGA的实际测试中,设计了RS(1 023,847)码的性能测试平台,测试平台结构示意图如图7所示。 图7 性能测试平台结构 测试平台由数据测试仪和光衰减器,以及包含EPON电路的OLT芯片与ONU芯片等设备构成。1个OLT设备与4个ONU设备同时通信。测试过程中利用数据测试仪生成待编码数据并发送到OLT设备中,数据经过OLT设备后,进行RS(1 023,847)编码运算后输出,输出后的数据通过光纤传输至光衰减器,再从光衰减器到1号与4号ONU设备,每个ONU设备对编码数据进行译码,最终把译码纠错后的数据输出到数据测试仪,数据测试仪将接收到的数据与发送的数据进行比对,分析每个25 G EPON通信子系统的误码情况。若RS编译码器具有良好的数据纠错能力,达到系统要求的编码增益,则表明本编码器具有正确的逻辑功能,并且符合高速EPON系统的要求。 具体的测试方法为,利用数据测试仪向OLT发送固定帧长为64的数据,OLT将数据传输至每个ONU,ONU将数据返回数据测试仪来分析误码情况。光衰减器用来调节光功率,可以改变OLT至ONU传输过程中的误码率。整个测试过程分为两步。第一步,关闭带有FEC纠错功能的RS编译码器进行数据测试,测试从10-8到10-2等不同数量级的误帧率(Frame Error Rate)水平情况下信噪比数值。第二步,开启带有FEC纠错功能的RS编译码器进行数据测试,测试过程与第一步一致。 对用上述测试方法测试的数据进行整理,得出4个25 G EPON通信子系统接收的光功率-误帧率结果,如图8所示。其中,FEC1、FEC2、FEC3、FEC4等4条折线分别表示在开启FEC功能的情况下,OLT与第1、第2、第3和第4号ONU同时进行通信时,信道在不同误帧率情况下的信噪比数值;NO FEC1、NO FEC2、NO FEC3、NO FEC4等4条折线分别表示在关闭FEC的情况下,信道在不同误帧率情况下的信噪比数值。 图8 实际测试的信噪比-误帧率结果 从图8可以看出,对于4条子通信线路,在相同误帧率的情况下,开启FEC能带来明显的编码增益,所设计的RS(1 023,847)编译码器可以明显地改善4条通信线路的信号传输质量,在误帧率达到1×10-7时,开启FEC可以带来平均8.0 dB的编码增益,能够满足100 G EPON系统对纠错能力需求。 提出了一种适合于100 G EPON系统的通用RS编码器的设计方法。由4路25 G子系统构成100 G 通信系统。综合考虑码型性能和纠错能力,选用RS(1 023,847)作为编码器的码组。提出了一种通用的编码电路并行度计算方法,根据编码器参数与输入数据的特点,通过计算电路并行系数进而计算编码电路的并行度。通过选择合适的并行度,提出了适合于25 G EPON子系统的RS(1 023,847)的高速编码器设计方案,4路编码器同时工作,利用多路切换技术、数据并行化等技术,实现了一种由4路25 G EPON子系统构成的100 G EPON通信系统的高速RS编码器。实际测试结果表明,设计编译码器的数据吞吐率和纠错能力满足100 G EPON系统要求。1 RS码的原理与性质

1.1 RS串行编码原理

d1xn-k+1+d0xn-k+rn-k-1xn-k-1+…+r1x1+r01.2 基于LFSR的串行RS编码方法

1.3 并行RS编码方法

m(n+1)Fq-2G+…+m(n+q-2)FG+

m(n+q-1)G1.4 RS编码的并行度计算

2 并行编码器的实现

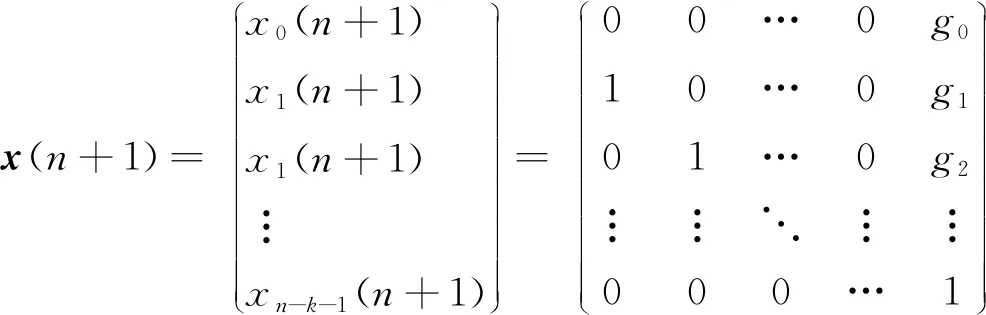

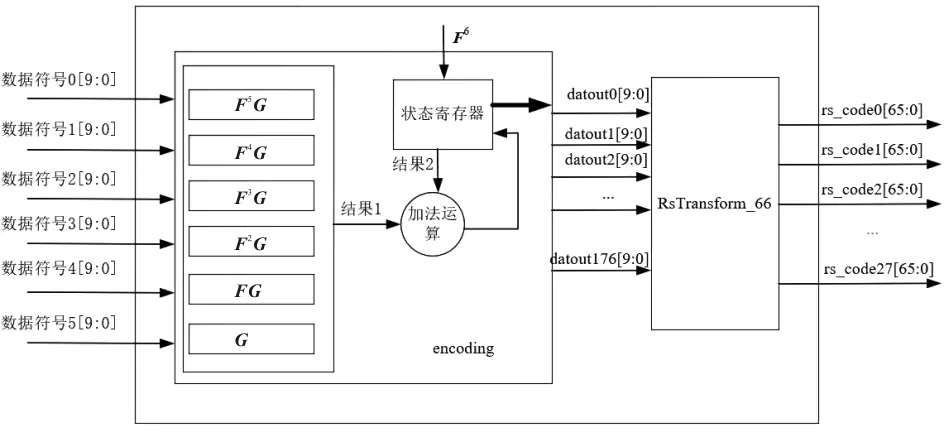

2.1 100 G EPON通信系统

2.2 RS编码器并行度的选择

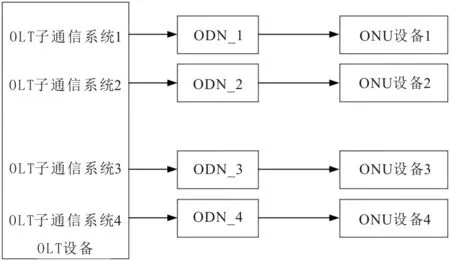

m(n+1)F4G+m(n+2)F3G+m(n+3)F2G+m(n+4)FG+m(n+5)G2.3 编码器整体架构设计

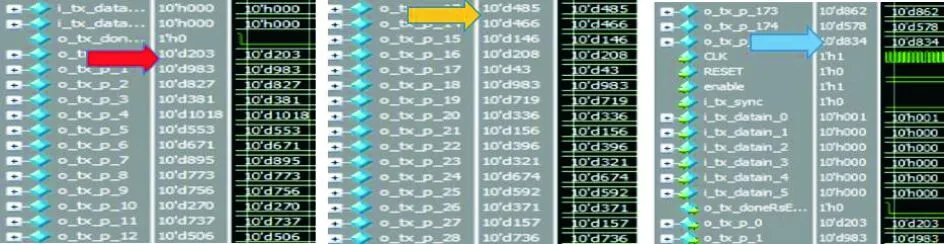

3 仿真结果及分析

3.1 算法与硬件仿真

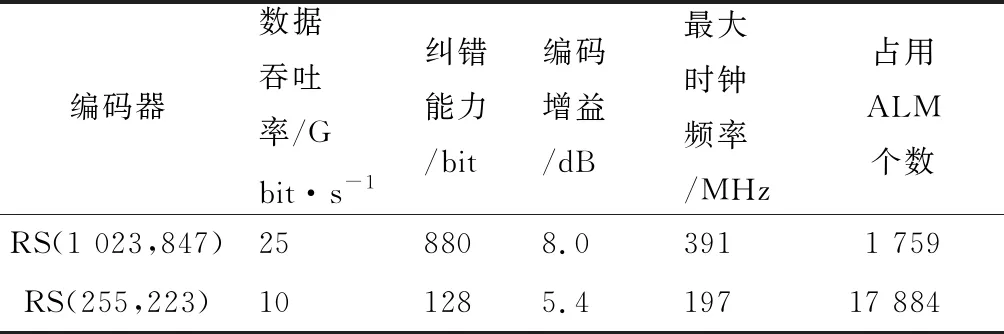

3.2 电路时序与资源分析

3.3 编码器的硬件测试

4 结语