一种星载大功率T/R组件的高密度组装技术 ①

2021-03-01王杨婧秦绪嵘冯小晶张成果谢拥军

王杨婧,秦绪嵘,冯小晶,张成果,谢拥军

(1.中国空间技术研究院西安分院,西安 710000;2.北京航空航天大学,北京 100191)

0 引言

应用于星载相控阵天线中的T/R组件,正如其在地面和机载平台应用一样,经历了基于混合微波集成电路的组件和单片微波集成电路组件两大阶段,伴随着第一代硅(Si)、第二代砷化镓(GaAs)器件的成熟应用,高密度集成的多芯片组件(mulitichip module,MCM)封装模块,已成为现阶段有源相控阵的主流技术方案[1-3]。然而,高轨通信卫星、高轨遥控/遥测卫星、高轨SAR卫星等应用[4-6],对核心器件的高功率、高效率、小型化和高击穿电压特性提出了新的需求[7-8],已成熟使用的GaAs器件无法满足数倍增长的功率密度需求。随着第三代半导体材料氮化镓(GaN)技术逐步趋于成熟,其在高能量带隙、高击穿场强、高射频密度、宽带、高偏压、高热导性等方面的优势逐步明显,可提供的功率密度比GaAs器件高十倍。因此,采用GaN器件的T/R组件将实现更大的输出功率、更高的效率和宽带性能优势,已在有源相控阵的T/R组件中获得应用[9-11],并且在星载相控阵系统的应用极具优势。

本文通过实验,介绍了一款4通道X波段50 W T/R组件(简称50 W T/R组件)的高密度组装工艺,该组件以多级GaN芯片作为核心放大器芯片、辅助GaAs芯片、Si芯片等控制、驱动或场效应管芯片的微波MCM技术[12-13],可实现高功率、高集成度与高可靠性的卫星载荷需求。

1 组件设计

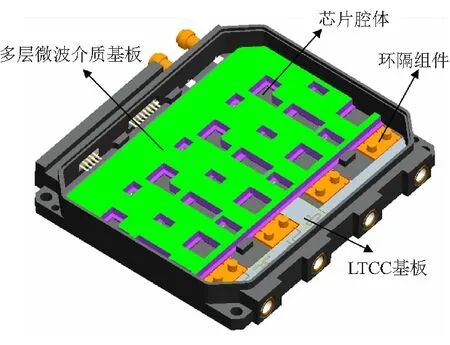

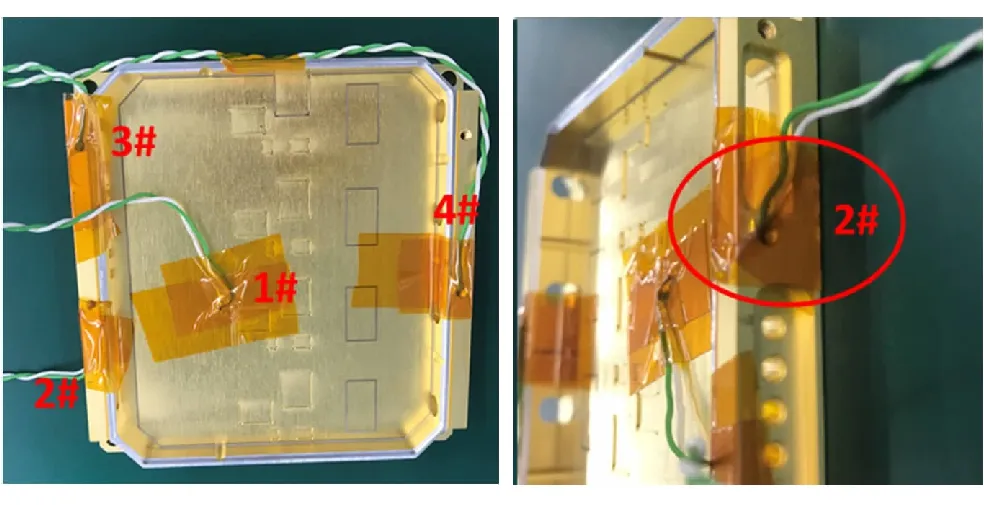

50 W T/R组件具有收发放大、幅相控制、耦合定标、电源脉冲调制和幅相控制等功能,每个T/R组件内部包含四个通道,封装在统一的硅铝管壳内,结构形式如图1所示,组件内部的有源部分通过裸芯片实现,主要器件包括Si基环隔组件、GaN功放芯片、GaN驱放芯片、GaAs限幅器芯片、GaAs低噪放芯片、GaAs幅相控制多功能芯片、GaAs延时器芯片、Si基电源驱动芯片、Si基PMOS管芯片、阻容元件等;无源部分通过低温共烧陶瓷(low temperature co-fired ceramic,LTCC)基板和多层微波介质基板实现,且主要射频和低频控制走线均在多层微波介质基板中实现。

图1 50 W T/R组件结构形式

由于该50 W T/R组件中采用了多级放大器芯片,单通道峰值输出功率高达57 W,平均热耗65 W,且受相控阵系统的空间尺寸限制,需在单面开腔中实现高密度的射频与低频布局。结合结构、工艺、组装能力等因素,多层微波介质基板采用了开腔设计,将各级GaN放大器芯片进行嵌入式装配与管壳接触,提高散热能力;环隔组件与SMP端口采用LTCC基板,实现高隔离度的射频信号耦合器输出和耦合信号的合路。

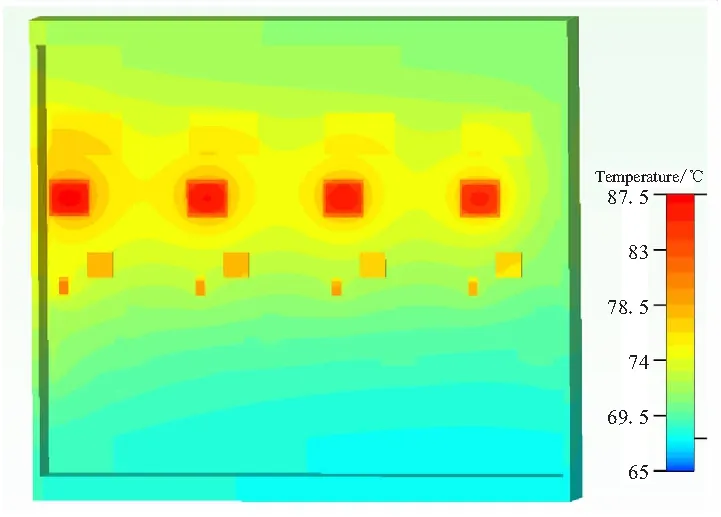

其中,功耗最大的为末级GaN功放芯片和前级GaN驱放芯片,为了保证大功率GaN芯片可以实现良好的热传导,对两种GaN芯片按照全焊接的方案进行了热仿真。经过仿真计算,组件四个通道单只GaN功放芯片峰值热耗60 W、结温101.9 ℃,GaN驱放芯片结温89.7 ℃。另外,对其他功耗较大的芯片也进行了热仿真,GaAs限幅器芯片和后端的Si基环隔组件,按照导电胶粘接的预案进行了热仿真,结温分别为71.5 ℃和97.2 ℃,仿真结果如图2所示。根据仿真结果,GaN芯片一级降额温度为165 ℃,GaAs芯片一级降额温度为110 ℃,满足设计要求。

图2 50 W T/R组件热仿真结果

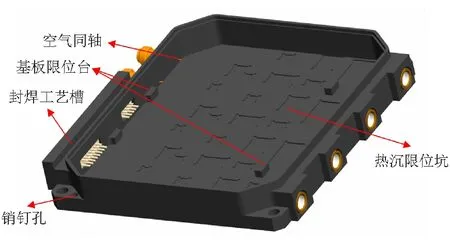

另外,由于该50 W T/R组件中包含了大量未封装裸芯片,为了提高产品的长期可靠性,采用了气密封装管壳结构;并且为了保证组装精度,管壳内部进行了限位结构设计,如图3所示。

图3 50 W T/R组件管壳的结构设计

考虑到实际组装过程中可能引入的各种不确定性因素,需要兼顾可实现性、可操作性与高可靠性来进行产品的工艺方案设计。

2 工艺设计与实现

2.1 工艺方案设计

2.1.1 工艺路线

根据热仿真结果,该50 W T/R组件中GaN功放芯片、GaN驱放芯片和环隔组件的功耗大,工作时结温较高,因此均需采用低热阻的焊接方式进行组装来实现良好的散热,保证两级GaN放大器芯片和环隔组件能正常工作,避免热积累导致芯片烧毁;而其它GaAs芯片、Si芯片、介质基板、LTCC基板等,由于对散热没有严格的要求,既可采用粘接的方式,也可采用焊接的方式进行组装。

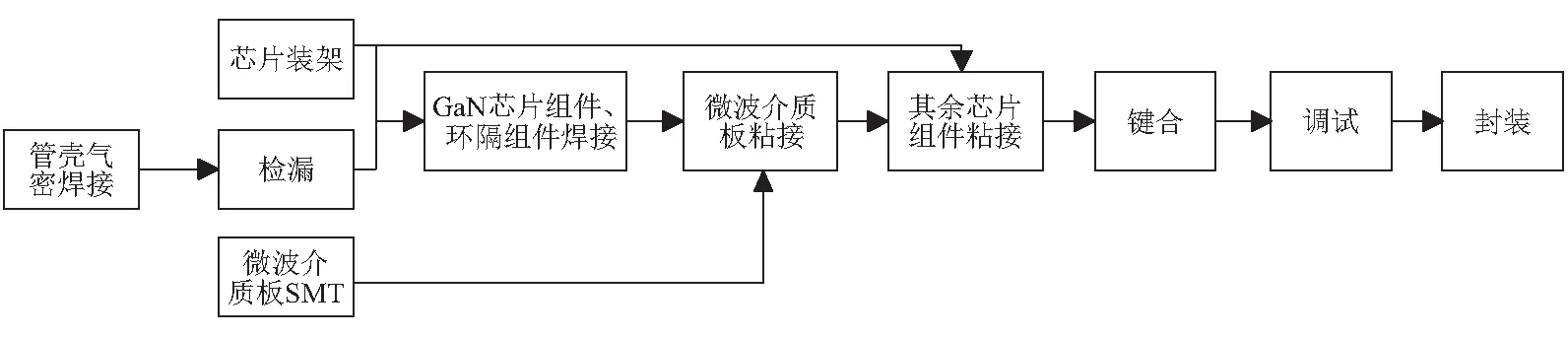

根据产品的结构与布局特点,多层微波介质基板和LTCC基板的组装具备两种实施方案:一是采用导电胶粘接的方式,二是采用焊接的方式进行组装。两种方案的共同要求均为低空洞,且两级GaN放大器芯片的空洞要求更为严苛(空洞率≤3%),以此来保证各通道热性能的均匀性。两种方案的基本流程如图4所示,方案一:先焊接GaN芯片和环隔组件,然后再进行介质基板和LTCC基板的粘接,但由于基板面积较大且为开窗结构,存在胶液涂覆操作效率低、芯片焊接后的保护难度大的问题,组装效率低;方案二:先焊接基板、GaN芯片和环隔组,然后再粘接其它GaAs芯片、Si芯片等,但由于对空洞率要求极高,焊接过程控制是其关键,该方案组装效率较高。

(a) 方案一基本工艺流程

从工艺流程的角度考虑,方案二比方案一的流程少,多层微波介质板SMT及其相关的清洗、检验、返修等工序均可以合并至一体化焊接工序,且大面积焊接比大面积粘接的可操作性更强;另一方面,该50 W T/R组件产品功率较大,基板采用焊接的方式能更好保证大功率芯片的热传导。因此本50 W T/R组件产品按照方案二来制定详细工艺方案。

2.1.2 工艺设计

由于该50 W T/R组件较为复杂,且功率密度大,体积小,组装量大。主要分为4个部分:

1)管壳焊接。该50 W T/R组件的管壳材料为Si50Al50,表面镀薄金(厚度≤0.5 μm),采用金锡(Au80Sn20)焊料将外部连接器、SSMA、SMP进行气密焊接。所选用材料与工艺均已在航天MCM产品中成熟应用。

2)芯片装架。该50 W T/R组件采用的多级放大器芯片,需要通过控制焊接空洞率来保证良好的散热。因此采用金锡焊料将芯片共晶焊接至钨铜热沉上,同时需要严格控制功放芯片与驱放芯片热源区的空洞率≤3%。所选用材料与工艺均已在航天MCM产品中成熟应用。

3)射频与低频部分组装。射频与低频电路集成在多层微波介质板中,射频微波信号的良好传输对基板的大面积接地有一定要求,且不能影响管壳已焊接部分的气密性,因此采用铅锡(Sn63Pb37)焊料将基板、阻容元件进行真空回流焊接,保证基板焊接空洞率≤25%。射频部分除基板外,还需将装架后的芯片组件与管壳进行组装,为保证功放芯片、驱放芯片与环隔组件的有效散热,这三种芯片采用铅锡焊料进行真空回流焊接,且需要保证焊接空洞率≤10%;其余组件均采用导电胶粘接的方式进行组装,各装入件之间的电气互联通过金丝或金带键合实现。

4)气密封装。采用激光封焊的方式进行气密封装,该工艺方法已在航天MCM产品中成熟应用。

2.2 关键工艺控制与实现

该50 W T/R组件的的关键工艺过程为基板与芯片组件焊接,关键点为焊接空洞的控制,因此投产验证样件进行了验证试验,以此来确定细节的实施方案与焊接曲线。基板及其上阻容、功放芯片组件、驱放芯片组件、环隔组件均采用铅锡(Sn63Pb37)焊料进行焊接,且需要在保证管壳已焊接部分可靠性的同时,完成芯片组件和基板焊接的低空洞率和高质量的焊接。因此采取了以下措施进行过程控制:

1)对管壳上各焊接区域进行激光刻线[14],保证回流焊接时各部分的焊锡不粘连,避免焊料堆积造成短路;

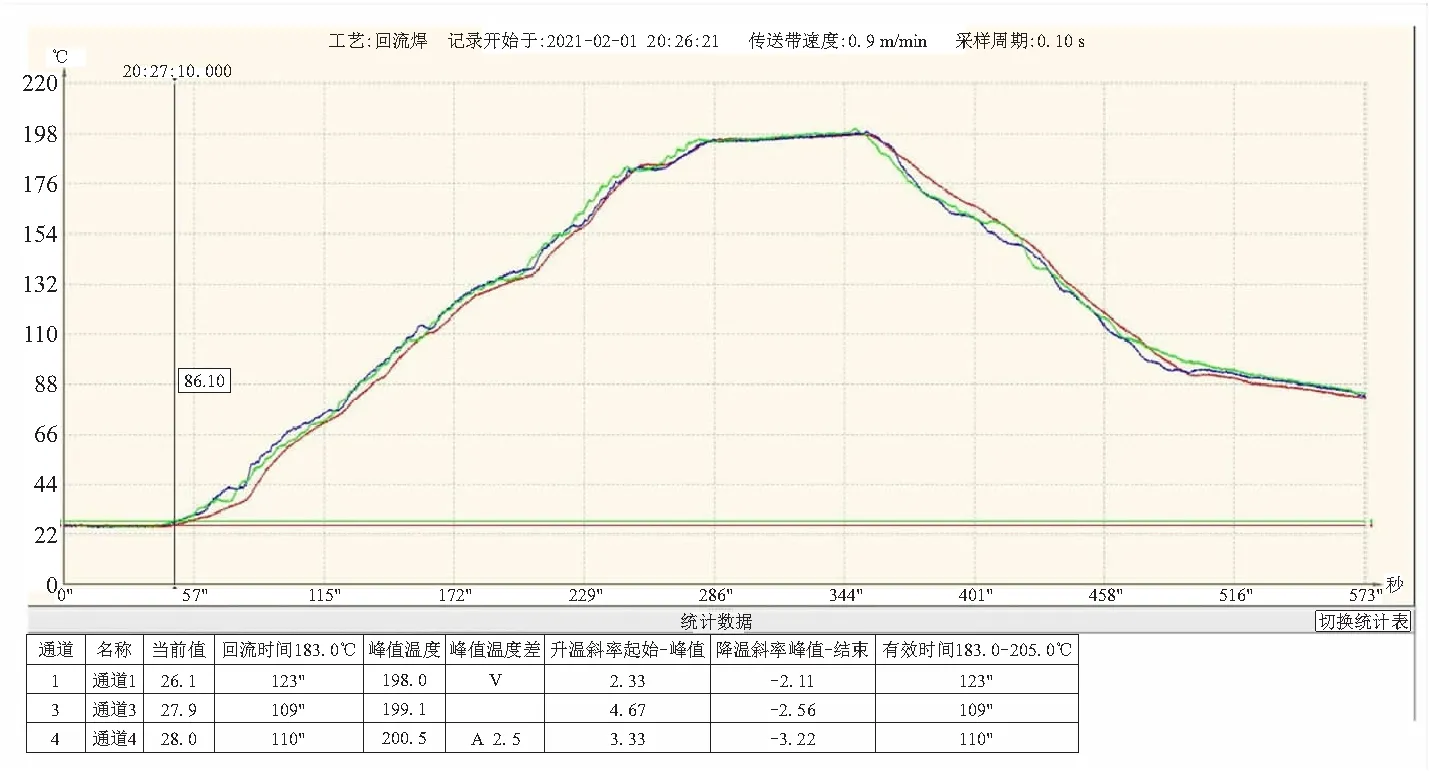

2)结合焊料特性[15]、产品结构特点以及元器件耐热情况,采用多点测温的方式来进行回流焊接的温度参数设置,如图5所示。

图5 50 W T/R试验样件点温测试

经过多次回流焊接温度实测,最终确定了基板的焊接工艺参数,焊接曲线如图6所示。

图6 50 W T/R试验样件焊接曲线

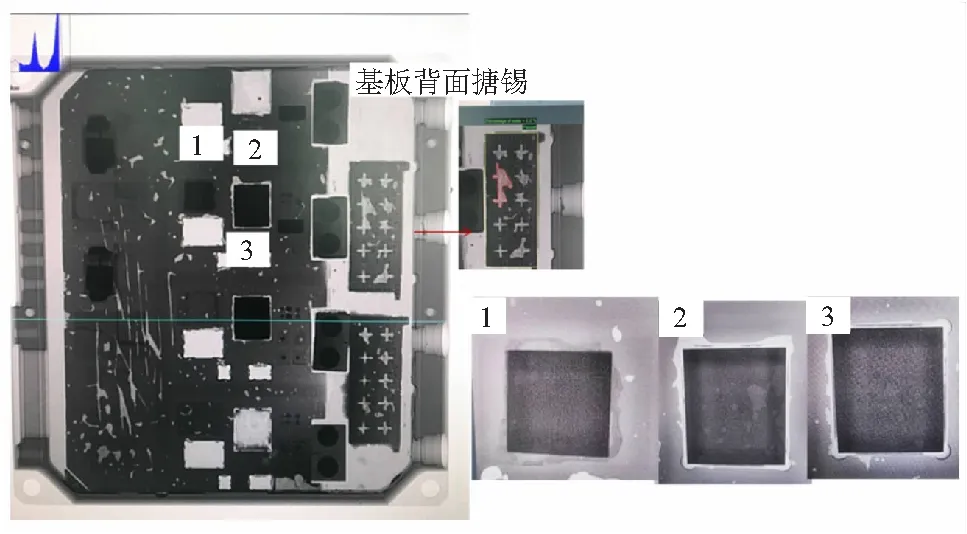

对焊接后的样件进行了X光检测,如图7所示,各组件焊接空洞率均满足要求。

3)焊接完成后的清洗,采用多次雾化清洗结合高温烘烤的方式,保证助焊剂完全清洗彻底,避免助焊剂残留影响裸芯片的可靠性。

图7 50 W T/R试验样件焊接结果

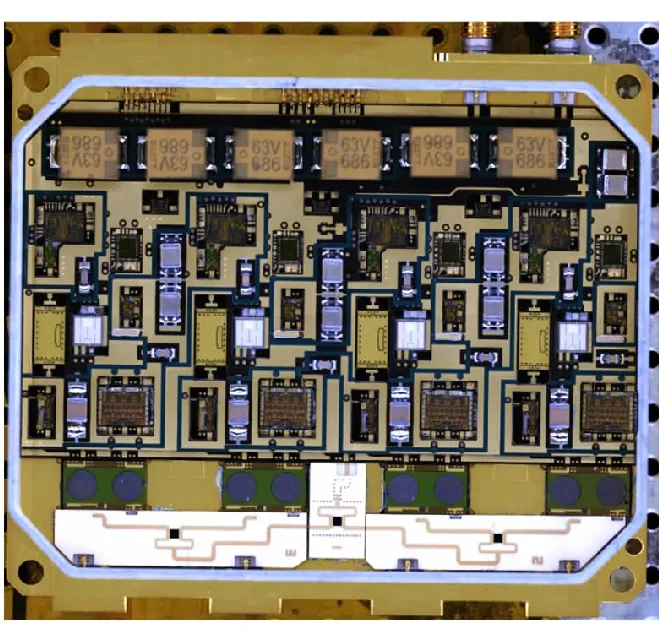

3 实物及测试

按照以上工艺方案对50 W T/R组件产品进行了组装,实物图如图8所示,尺寸74.3 mm × 76.9 mm × 11 mm,重量约130 g。

图8 50 W T/R组件实物图

经测试,50 W T/R组件单通道发射功率大于50 W,接收增益大于25 dB,噪声系数小于3.5 dB,测试结果满足设计指标要求。

4 结论

本文介绍了一款星载4通道X波段50 W T/R组件的高密度组装技术,重点介绍了关键工序控制与实现途径,实现了4通道大功率芯片、基板、与其它元器件的低空洞率一体化焊接,不仅满足产品的性能要求,也保证了高密度组装过程的可操作性和产品的高可靠性。组装后的产品测试结果表明,该50 W T/R组件的性能满足总体技术指标要求。本文所述的组装工艺技术对同类高密度混合封装产品的设计和工艺实现具有一定的参考价值。