基于快行FIR 滤波器的数字下变频设计及FPGA 实现①

2021-02-23孙宝华

孙 星,李 刚,姜 童,孙宝华

(中国空间技术研究院西安分院,西安 710000)

0 引言

现代战争对战场态势的即时性要求越来越高,合成孔径雷达可以获得地面二维高分辨率的图像,不惧各种恶劣天气,具有全天候、全天时工作优势,并且作用距离大,可以大大提高雷达的信息获取能力,已成为对战场侦察的重要手段[1]。

雷达信号处理中往往需要对接收的回波信号进行下变频处理,由于雷达系统的分辨率要求越来越高,发射信号带宽往往高达1 GHz。 受限于AD 芯片和FPGA 芯片的处理速率,传统的雷达接收系统采用模拟正交解调技术,不可避免地存在各种形式的误差,包括相参信号I、Q 的幅相不一致性和正交性误差,通道间频率特性失配等。 随着高速集成电路技术的快速发展,高速ADC 和高性能FPGA 芯片不断出现,使得中频数字采样成为可能。 中频采样具有数字系统固有的许多优点,其正交性和一致性要远远好于传统模拟方法得到的正交I/Q 信号。 中频采样后利用数字下变频(digital down converter,DDC)技术将高频数据流信号变成易于后端数字信号处理器实时处理的低频数据流信号,这样可减少系统的复杂性,提高微波遥感数据处理器的数字化程度和性能[2]。

目前,在FPGA 中实现FIR 滤波常用的有乘累加串行结构和并行结构两种方法。 串行滤波器所占硬件资源较少,但对N阶滤波器完成一次滤波需要进行N次乘累加运算,速度较慢,仅适用于低速中频采样后滤波处理。 并行滤波器采用多个乘法器和并行加法器按流水结构工作,能够达到较快的速度,提高滤波器的吞吐量,并降低功耗,可以用于高速中频采样后滤波处理。 但随着并行度的增加,其硬件资源消耗也呈线性增加,这种硬件消耗在很多情况下往往是不允许的。 从Winograd 的著作中可以知道,两个N-1 次的多项式相乘,可以只用2N-1 次乘法运算,降低的乘法运算次数,被额外的加法运算代替[3]。 由于加法器比乘法器具有更快的运算时间和更小的硬件消耗,通过这种算法优化可以达到滤波运算速度和硬件消耗的平衡。

文献[2]和文献[4]中采样率均低于100 MHz,采用串行结构方法实现FIR 滤波。 文献[5]和文献[6]中采用并行结构方法实现FIR 滤波,并行度分别为4 路和8 路,提高了数据的吞吐率,分别高达1 Gbps 和2 Gbps,但没有对并行滤波器结构进行优化,消耗较多硬件资源。 文献[3]研究了优化并行滤波结构的快行FIR 算法理论,但没有给出并行度为8 的快行滤波器实现结构。 文献[7]在FPGA 中采用并行度为2 的快行滤波器实现结构,将数据吞吐率提高到320 Mbps 以上,同时节省了硬件开销。文章高速AD 采样率达2 Gbps,首先从理论上得出8路并行滤波器和优化后8 路快行滤波器的实现结构,然后在FPGA 中编程实现,并对两种实现结构消耗的硬件资源进行了比较,最后结合工程项目给出了数字下变频模块的实验验证结果。

1 系统硬件组成

文章介绍的雷达系统数据处理部分包含信号处理单元、固存单元和数传处理单元三块单板,集成于一台单机内,实现线性调频信号的产生、雷达回波采集处理、数据存储和下传。 其中信号处理单元硬件框架如图1 所示。

图1 信号处理单元硬件框图Fig.1 Signal processing unit hardware block diagram

图1 中系统时钟为2 GHz,通过时钟管理芯片产生2 GHz 时钟信号给高速ADC 和DAC,AD 和DA 采样位数均为10 bit。 两片 DDR 芯片用于 SAR 数据 BAQ 压缩处理时的高速乒乓缓存,FPGA 芯片选用XILINX 公司 Virtex-5 系列 1 300 万门器件 XQ5VFX130T-1EF1738I,作为信号处理单元主控制器。

2 数字下变频(DDC)原理

DDC 的基本功能就是将速率较高的数字中频信号下变频为数字基带信号,并降低信号的采样速率。 DDC 一般由数控振荡器(numerical control oscillator,NCO)、混频器、低通滤波器和抽取器组成[4]。典型的DDC 基本原理框图如图2 所示。

图2 典型的数字下变频原理框图Fig.2 Typical block diagram of digital down conversion

直接中频采样对采样频率有一定要求,需遵循带通采样定理[8]。 设信号的中心频率为f0,采样频率为fs,信号带宽B,根据带通采样定理:f0和fs之间的关系需满足fs=4f0/(2m-1),m取能满足fs≥2B的正整数。

文中SAR 系统中雷达回波信号的中心频率f0=1.5 GHz,信号脉宽15 μs,信号带宽B= 400 MHz,采样频率fs=2 GHz,即fs=4f0/3,满足带通采样定理,则有:

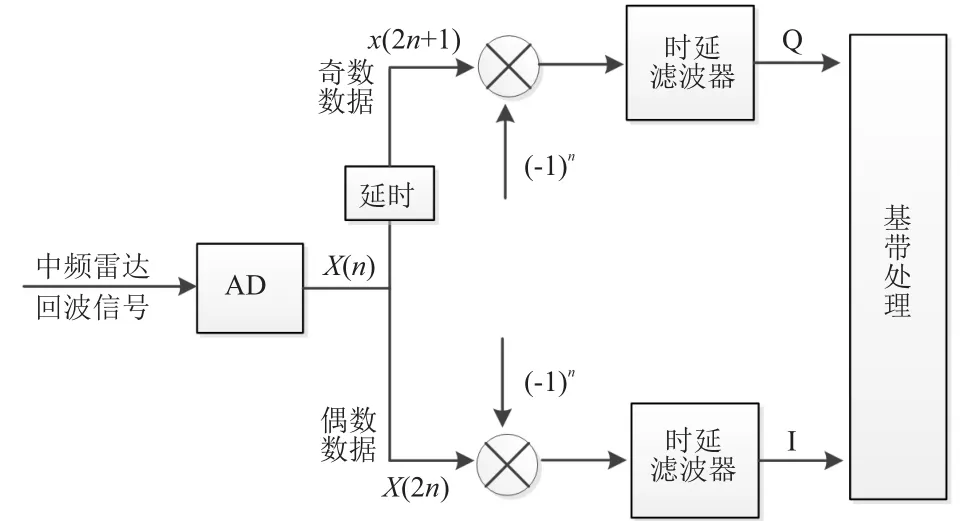

将式(1)和式(2)与图2 中AD 采集的数据相乘后,I 路只剩下偶数数据,奇数数据相乘后为0,Q 路只剩下奇数数据,偶数数据相乘后为0。 将图2 中抽取步骤提前,将AD 输入的偶数数据传给I 路,奇数数据传给Q 路,则图2 中I 路的低通滤波器只剩下偶数部分,Q 路的低通滤波器只剩下奇数部分。DDC 原理图可简化为图3 所示结构。

图3 简化的数字下变频原理图Fig.3 Simplified block diagram of digital down conversion

本设计中频雷达回波信号经采样率2 Gbps 的AD 芯片采样后,转换为4 路500 Mbps 的高速差分数字信号 DI、DQ、DId 和 DQd 传输给 FPGA,其中 DI 和DId 为采样点的偶数部分,DQ 和DQd 为采样点的奇数部分。 为了降低FPGA 内部的时钟速率,减小后续SAR 数据处理时序紧张风险,FPGA 中使用ISERDES核将4 路高速数据降速为16 路125 Mbps 速率的数据,其中偶数部分和奇数部分各8 路。 由于偶数部分和奇数部分相差半个采样点,需要通过时延滤波器加以校正,两个时延滤波器系数都是从原低通滤波器抽取出来的,保证在幅度上具有较好的一致性。 偶数部分数据进入I 路时延滤波器,滤波器系数取原低通滤波器偶数部分,奇数部分数据进入Q 路时延滤波器,滤波器系数取原低通滤波器奇数部分。

3 并行和快行FIR 滤波器

设一个 FIR 滤波器的输入为x(n),系数为h(n),输出为y(n),则在时域上有如式(3)关系[9]:

变换到频域上有如式(4)关系:

把X(z)按2 并行滤波器多项式分解为偶数和奇数两部分,有如式(5)关系:

其中X0(z2)和X1(z2)分别为x(2k)和x(2k+1),0≤k<∞的频域变换。 同理可以将H(z)分解为:

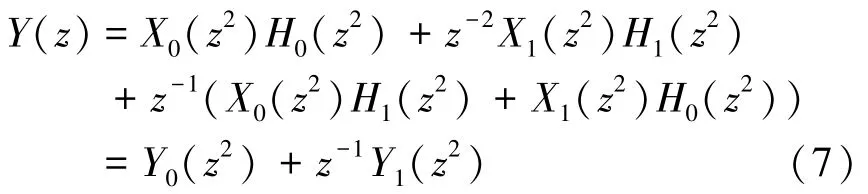

将式(5)和式(6)代入式(4)可得:

其中Y0(z2)和Y1(z2)分别为y(2k)和y(2k+1),0≤k<∞的频域变换。

把Y(z)按2 并行滤波器多项式分解为,可表示为如式(8)、式(9)两种形式[10]:

其中X0,X1和H0,H1分别为输入偶数和奇数的数据及系数Z变换。 式(3)和式(4)分别是并行度为2 的并行滤波器和快行滤波器的实现结构。

同理,把Y(z)按8 并行滤波器多项式分解,为简化表达式定义Xa+b=Xa+Xb,Ha+b=Ha+Hb。 则8 路并行滤波器结构可表示为如式(10)形式:

8 路快行滤波器结构可表示为如式(11)形式:

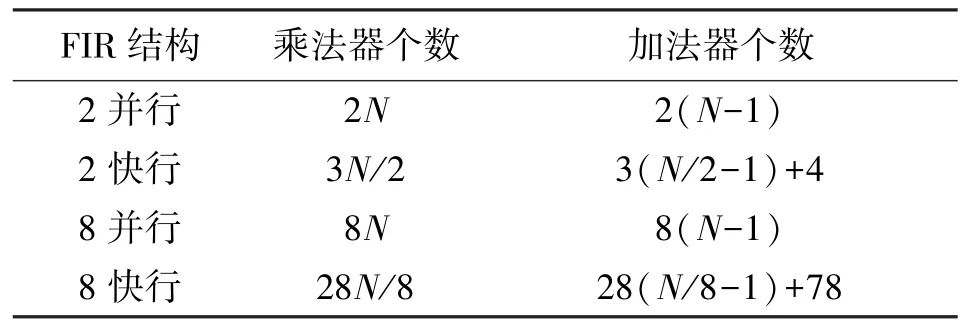

假设原始滤波器的阶数为N,2 项分解后两个子滤波器H0、H1阶数均为N/2,8 项分解后8 个子滤波器H0-H7阶数均为N/8。 从式(8) ~式(11)可以得出并行滤波器和快行滤波器消耗的乘法器和加法器资源[3]如表1 所列。

表1 并行滤波器和快行滤波器比较Tab.1 Parallel filter and fast filter comparison

从表1 可以看出:并行度为2 的快行滤波器比并行滤波器大约节省25%的乘法器个数,并行度为8 的快行滤波器比并行滤波器大约节省56%的乘法器个数。

4 FPGA 实现结果

使用Matlab 工具设计阶数为48 的原始低通滤波器,参数设置如图4 所示。

图4 低通滤波器参数设置Fig.4 Low-pass filter parameter setting

将原始低通滤波器48 个系数拆分成偶数部分和奇数部分,其中偶数部分为I 路时延滤波器系数,奇数部分为Q 路时延滤波器系数。 两路滤波器实现结构完全相同,差别在于滤波器系数选取不一样。以I 路时延滤波器为例,设滤波器系数h=h0,h1,…,h23,则8 路并行滤波器系统函数分别为:H0=[h,0,h8,h16],H1=[h1,h9,h17],…,H7=[h7,h15,h23],按照式(11)中8 路快行滤波器实现结构,得出28 个独立的阶数为3 的子滤波器系数和滤波器输入,然后对28 个子滤波器输出结果再按照式(11)进行合并,最终输出8 路125 MHz 时钟速率并行滤波后结果Y0,Y1,…,Y7。

根据式(10)和式(11)实现结构,在FPGA 中分别编程实现,占用的硬件资源如表2 所列。

从表2 可以看出:优化后的快行滤波器与并行滤波器实现结构硬件消耗相比较,在DSP48 资源消耗上改善效果显著,大约节省40%,在寄存器资源消耗上改善也较为明显,大约节省25%。

表2 并行滤波器和快行滤波器硬件资源比较(并行度为8)Tab.2 Parallel filter and fast filter hardware resource comparison(parallelism=8)

中频信号经高速AD 采集后,偶数和奇数部分在FPGA 中,分别经过8 路快行滤波数字下变频模块处理后的结果如图5 ~图7 所示:

图5 为数字下变频后的时域波形,可以看出中频信号被成功的下变频为正交的基带信号且两路信号幅度一致性较好。

图5 数字下变频后时域波形Fig.5 Time domain waveform after digital down conversion

图6 为数字下变频后频谱图,可以看出下变频后信号带宽仍为400 MHz,频谱图上无明显杂散点,数字滤波器效果较好。

图6 数字下变频后频谱Fig.6 Spectrum after digital down conversion

图7 为数字下变频后脉冲压缩结果,可以看出脉压效果优异,满足雷达系统指标要求。

图7 数字下变频后脉压结果Fig.5 Pulse compression result after digital down conversion

5 结论

文章采用8 路快行滤波器结构的数字下变频方法,降低了FPGA 内部数据处理的时钟速率,同时通过优化并行滤波器的实现结构,硬件资源的消耗改善效果显著,平衡了处理速率和硬件资源消耗的矛盾,实验结果表明该方法在2 Gbps 高速采样率下性能优异,占用硬件资源较少,具有较高的工程可行性和实用性。