电子纸的2W2D工艺改善研究

2020-05-11王凤涛曹洪韬刘艳葵耿红帅张鹏曲

佟 月,佟 硕,王凤涛,曹洪韬,刘艳葵,耿红帅,李 森, 张鹏曲,卢 凯,孙 亮,张 磊,陈 思,王 威

(北京京东方光电科技有限公司,北京 100176)

1 引 言

借鉴成熟的薄膜晶体管液晶显示(TFT-LCD)技术,新兴的电子纸行业也开始了飞速发展[1-4],电子纸的TFT基板设计越来越注重精简工艺,以实现生产成本的降低。其中,最有效的精简方式是减少掩膜数量,于是发展了半色调掩膜工艺[5-7],实现了由5次光刻减少为4次光刻工艺。半色调掩膜工艺是通过将5次光刻产品的有源半导体层和源漏极层光刻合二为一,通过一次曝光,形成有源半导体层和源漏极层两层的图形,除正常的完全曝光外,在TFT沟道处需进行部分曝光,留有部分光刻胶,以实现TFT沟道处n+a-Si的刻蚀。由于同时涉及金属层和非金属层的刻蚀,因此半色调掩膜后同时需要湿刻和干刻两道工序。

传统的半色调掩膜后的刻蚀工艺采用的是一次湿刻一次干刻(1W1D)工艺,其中干刻过程包括刻蚀a-Si形成a-Si图形[8-11],灰化沟道处的光刻胶暴露沟道,刻蚀沟道处金属Mo和n+a-Si层。由于干刻过程刻蚀膜层多,刻蚀时间长,因此刻蚀均一性差,导致玻璃四周的沟道厚度过薄,影响TFT特性,损失良率。此外,采用1W1D的刻蚀方法对半色调掩膜光刻胶的厚度和均一性都有较高的要求,管控难度大,生产过程中经常出现未达管控标准返工重新进行曝光的情况,严重浪费了产能。

为了改善1W1D带来的问题,我们参考了非电子纸产品的两次湿刻两次干刻(2W2D)的工艺方法。然而非电子纸的2W2D工艺会产生较长的a-Si拖尾,导致较大的寄生电容,对像素电压造成扰动,产生良率损失;此外,a-Si残留和沟道特性问题也阻碍了电子纸良率的进一步提升。

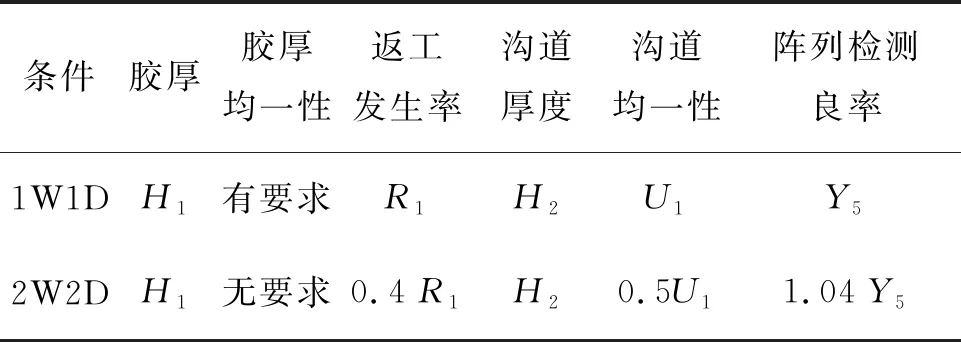

因此,本文对非电子纸产品的2W2D工艺进行了改善,开发适合电子纸产品的2W2D工艺。通过降低两次湿刻时间,改善灰化条件,减小a-Si拖尾现象;建立a-Si处理工序,消除a-Si残留;调整a-Si成膜条件和钝化层成膜前处理条件,改善沟道特性,使其可以完全满足电子纸的特性要求。相比于1W1D方法,改善后的2W2D方法得到的沟道厚度均一性提升了50%,阵列检测良率提升了4%~10%;同时无需管控半色调掩膜光刻胶的均一性,仅满足光刻胶厚度的管控要求即可,使曝光返工比例降低60%,有效地改善了电子纸产品的沟道特性与刻蚀均一性,提升了产品良率,减少了产能浪费,降低了成本,对4次光刻电子纸产品具有重要指导意义。

2 实验方法

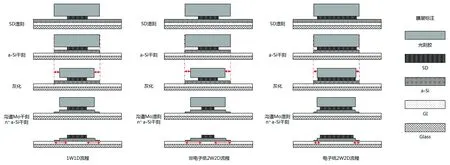

图1为传统的1W1D、非电子纸2W2D和本文提出的电子纸2W2D工序流程图。图中自下而上的膜层分别为玻璃基板,栅极金属层,栅绝缘层,a-Si有源层,n+a-Si层和源漏极金属层。传统的1W1D工艺流程为:在半色调掩膜曝光显影后,首先通过湿刻法刻蚀源漏极走线图案;再通过干刻法刻蚀a-Si形成a-Si图形,灰化沟道处的半色调掩膜光刻胶暴露沟道,刻蚀沟道处金属Mo和n+a-Si层。非电子纸2W2D工艺流程为:首先通过第一次湿刻形成源漏极层走线图形;再通过第一次干刻进行a-Si层刻蚀,并灰化沟道处的光刻胶;然后通过第二次湿刻去除沟道处的金属;最后通过第二次干刻完成沟道处n+a-Si的刻蚀。本文提出的电子纸2W2D工艺流程相比非电子纸2W2D工艺,主要变更在第一次干刻过程,增加a-Si处理步骤,改善a-Si残留问题。此外,参数方面降低了两次湿刻时间,变更灰化工艺条件,共同改善a-Si拖尾现象;调整了a-Si膜层的沉积条件和钝化层沉积前处理条件,改善沟道特性。

图1 1W1D、非电子纸2W2D和电子纸2W2D刻蚀工序流程图。Fig.1 Flowcharts of 1W1D, 2W2D for non-electronic paper and 2W2D for electronic paper.

3 电子纸2W2D工艺改善验证

3.1 a-Si拖尾现象改善

3.1.1 a-Si拖尾现象不良原因

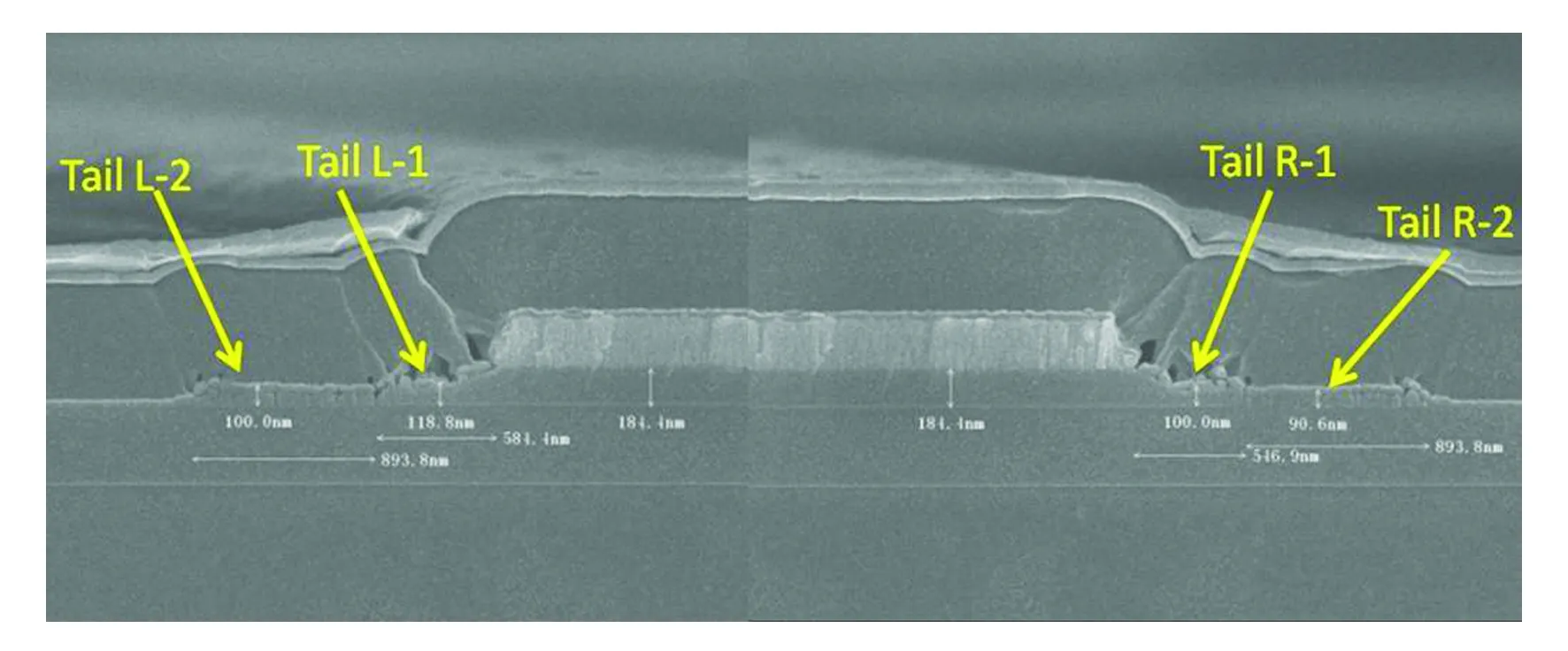

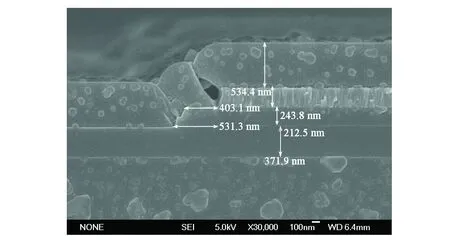

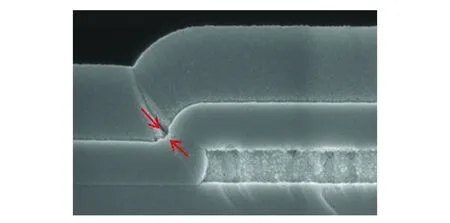

在电子纸产品开发过程中,采用传统1W1D工艺的a-Si拖尾距离较长,长度约1.5 μm,SEM图如图2所示。而直接参考非电子纸2W2D方法,得到的图形a-Si拖尾比1W1D更大,长度约1.8 μm。

图2 1W1D的a-Si拖尾现象SEM图Fig.2 SEM image of a-Si tail by 1W1D

由于a-Si拖尾区域下方无金属遮挡,当有光照时,该区域也会存在微弱的电荷传输,产生的作用等同于源漏极走线变宽,这时源漏极走线与像素之间的横向距离d减小,根据公式(1),源漏极走线与像素之间的寄生电容Cpd增大。

(1)

根据公式(2),寄生电容增加会导致像素电压Vp降低,对像素电压造成扰动,产生产品良率损失。

(2)

3.1.2 a-Si拖尾现象改善方法

为改善a-Si拖尾现象,我们在保证源漏极金属无残留的情况下,降低两次湿刻时间,并改善灰化工艺条件,来减小a-Si拖尾长度。图3为1W1D、非电子纸2W2D和本文提出的电子纸2W2D工艺a-Si拖尾现象形成机理图。

在1W1D工艺中,由于湿刻具有同向性,源漏极走线单边会较光刻胶内缩1.5 μm左右,而a-Si干刻具有异向性,因此a-Si与光刻胶的边缘相齐。经过灰化后,光刻胶的横向和纵向均有内缩,此时会露出部分a-Si边缘,经过沟道Mo和n+a-Si的干刻,露出的a-Si边缘上层部分被刻蚀,但底部仍有残余,而a-Si层较源漏极走线宽出的区域均为a-Si拖尾部分。非电子纸工艺之所以比1W1D的a-Si拖尾长度更长,是因为第二次湿刻过程源漏极走线进一步内缩。本文提出的改善措施主要有两方面,一是保证无金属残留情况下,尽可能降低两次湿刻时间,减小源漏极走线边缘内缩程度;另一方面是变更灰化工艺参数,配合光刻胶涂胶厚度趋势,提高胶厚处灰化速率,降低胶薄处灰化速率,减小光刻胶的横向内缩程度。

图3 1W1D、非电子纸的2W2D和电子纸的2W2D刻蚀工序的a-Si拖尾现象形成机理图。Fig.3 Mechanism diagrams of a-Si tail by 1W1D, 2W2D for non-electronic paper and 2W2D for electronic paper.

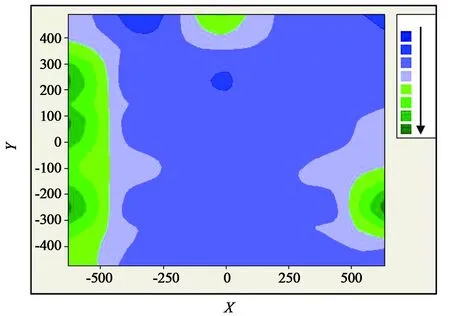

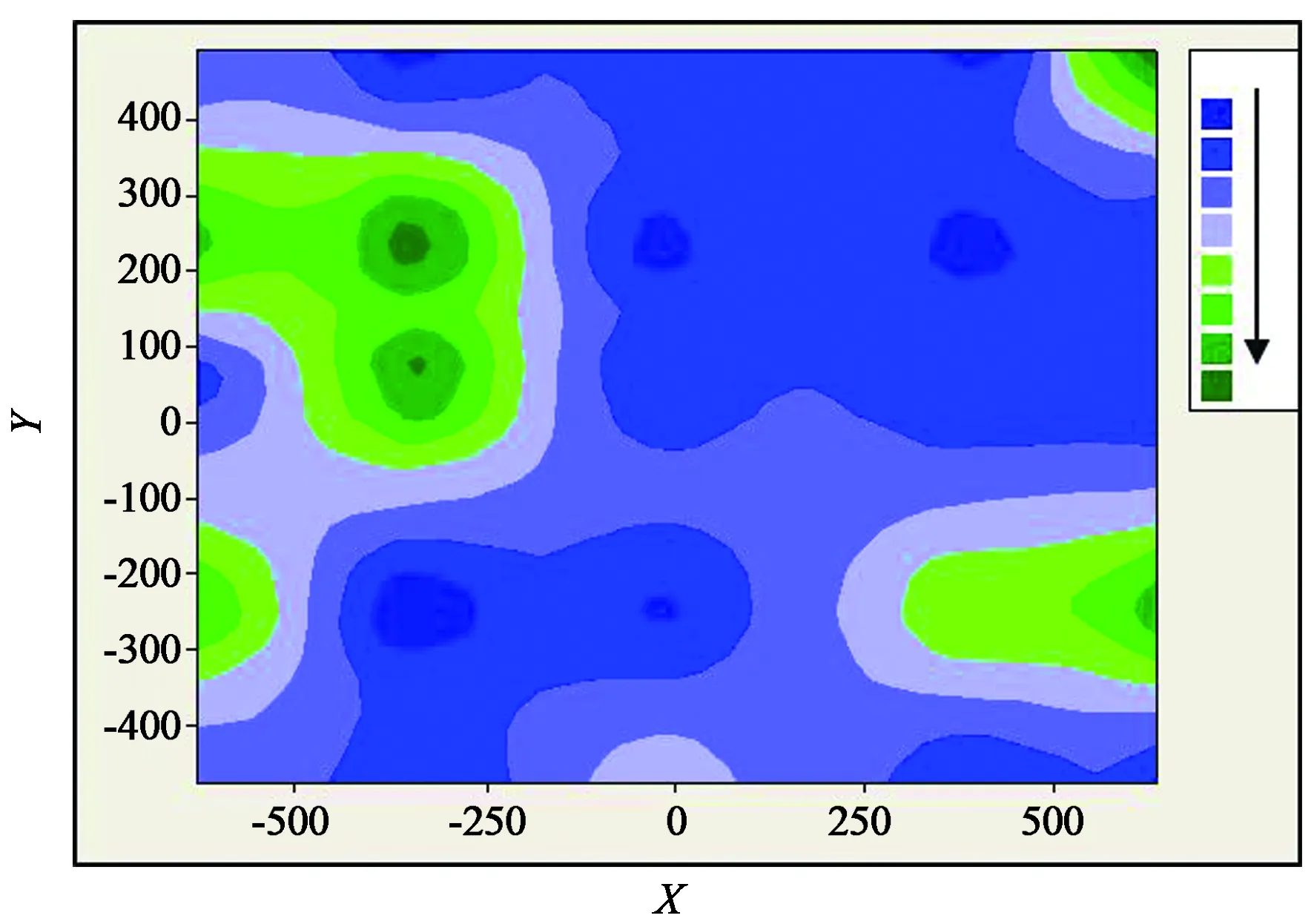

根据测试结果,光刻胶的厚度等值线分布如图4所示,边缘的光刻胶偏厚,中心的光刻胶偏薄。

图4 光刻胶的厚度等值线分布图Fig.4 Thickness contour map of photoresist

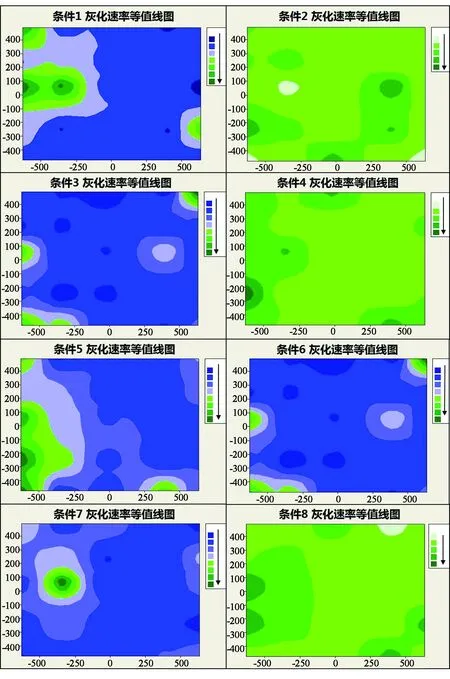

常规的灰化条件、灰化速率等值线分布如图5所示,灰化速率最快的位置靠近玻璃内部,导致玻璃内部的光刻胶横向内缩严重,a-Si拖尾偏长。

图5 常规灰化条件灰化速率等值线分布图Fig.5 Ashing rate contour map of traditional ashing condition

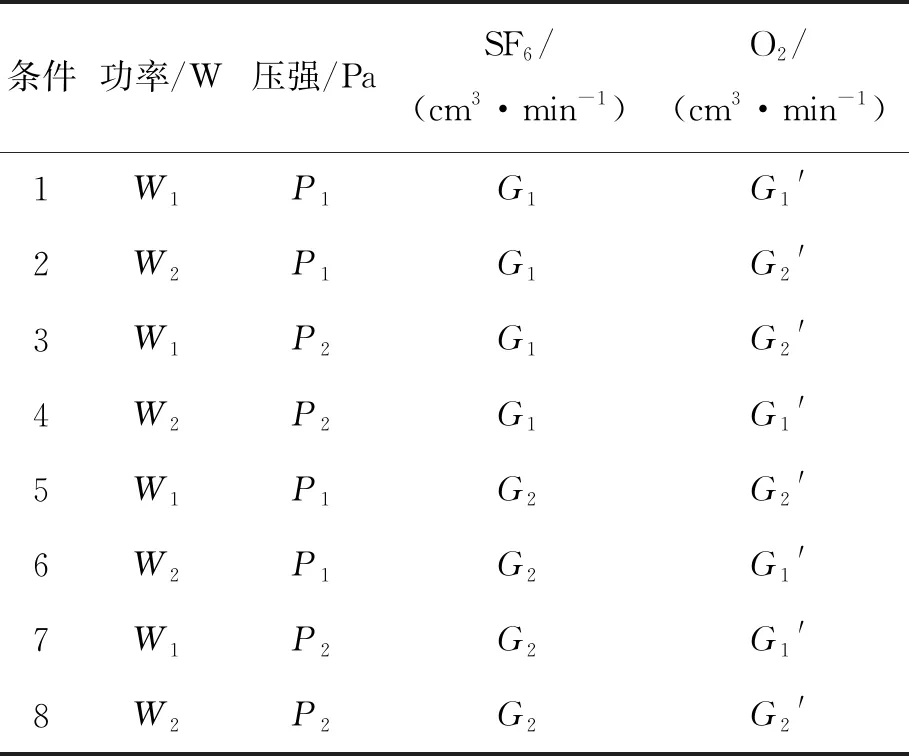

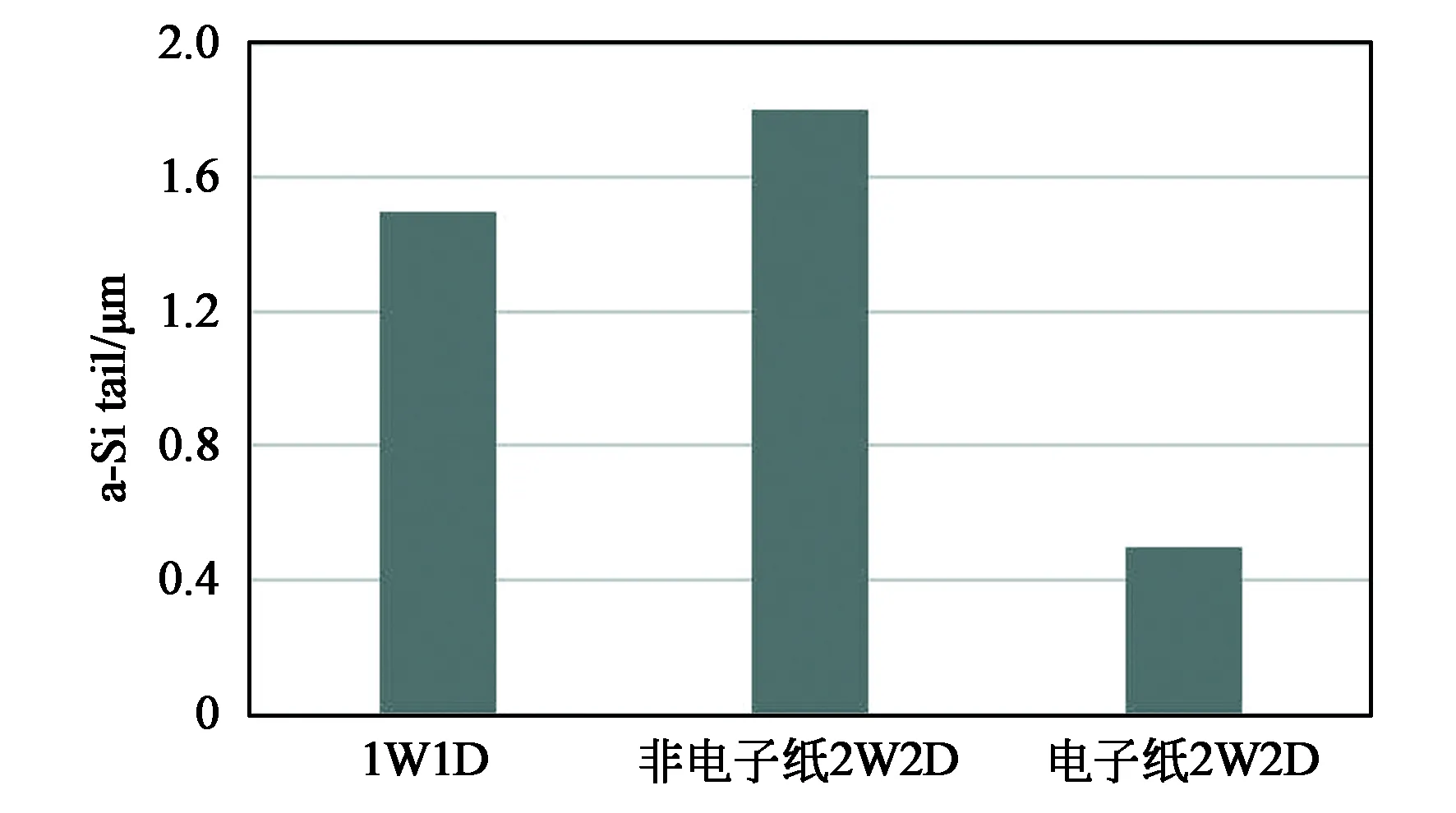

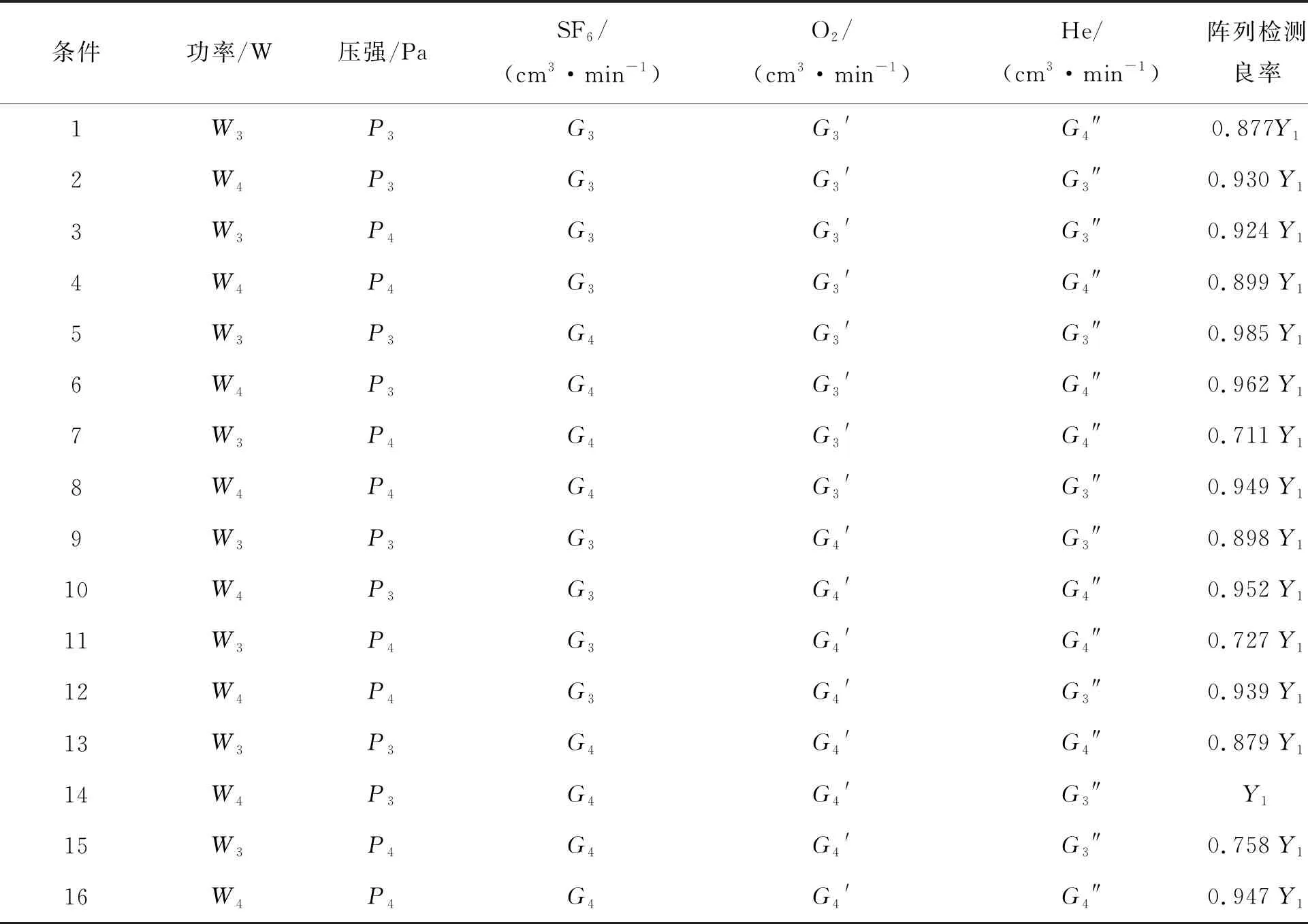

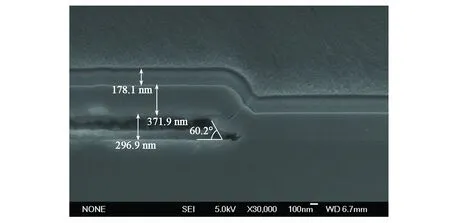

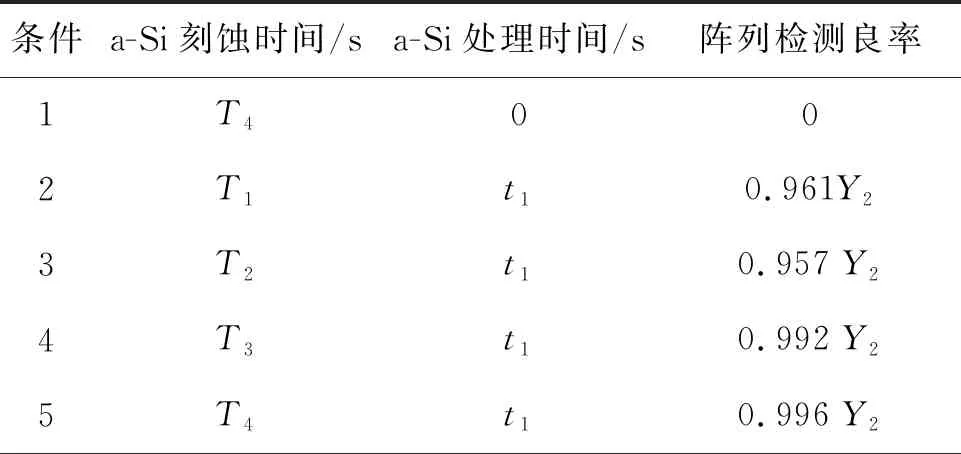

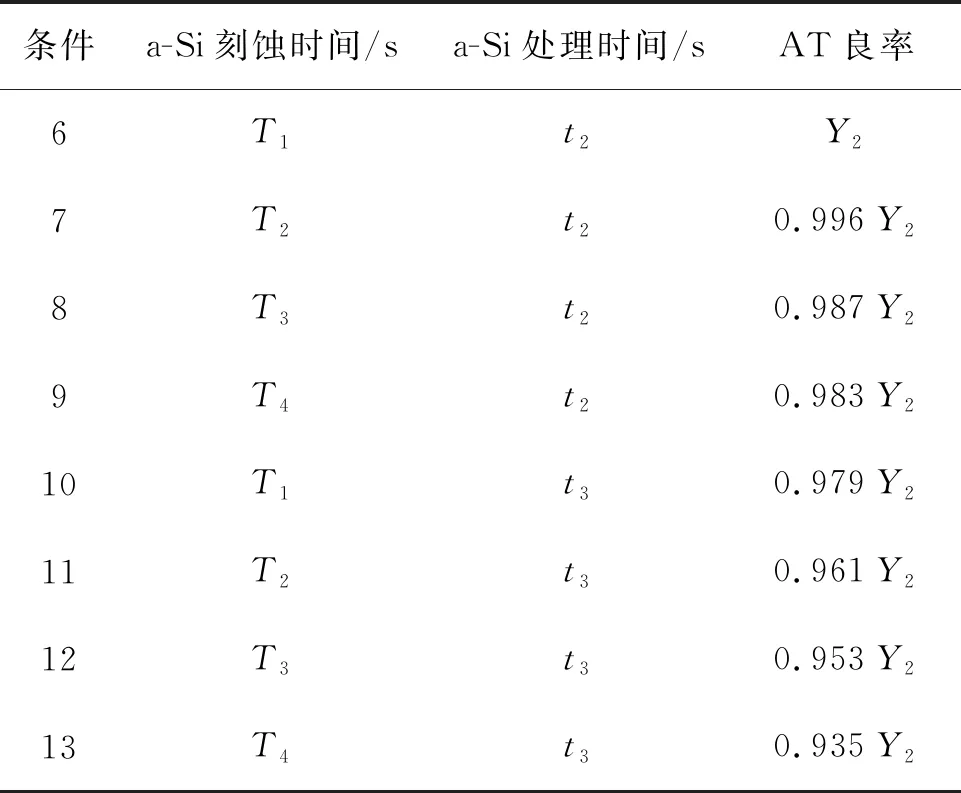

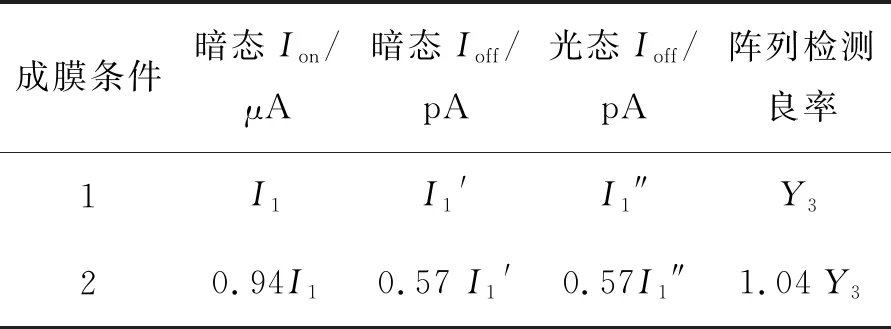

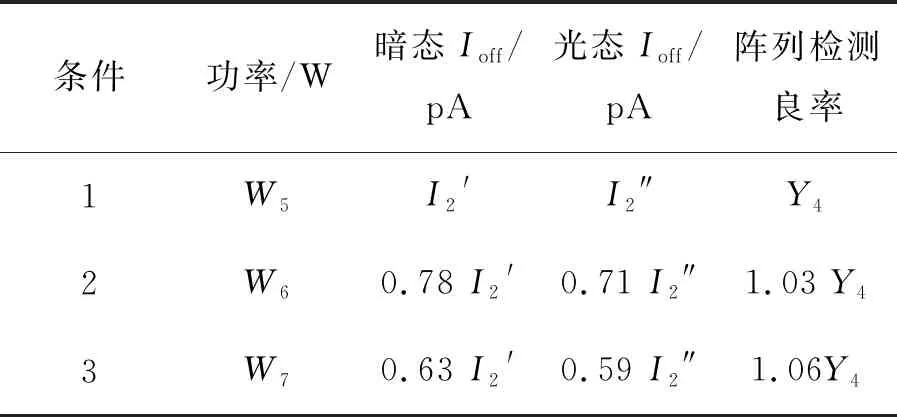

因此,我们对灰化工序的功率、压强、SF6、O2气体流量开展了4因子2水平的实验设计,其中W1 表1 灰化条件实验设计Tab.1 Experiment design of ashing condition 结果表明,增加功率和压强,降低SF6和O2气体流量,灰化速率呈现边缘快内部慢的趋势,即条件4的灰化速率分布情况与光刻胶厚度分布情况最为接近,因此我们选用条件4(功率W2、压强P2、SF6流量G1、O2流量G1′)为电子纸2W2D的灰化条件。 图6 实验设计灰化速率等值线图Fig.6 Ashing rate contour map of experimental design 综合降低两次刻蚀时间和变更灰化条件改善方法,进行了a-Si拖尾长度的测试,电子纸2W2D工艺可使a-Si拖尾长度降低至0.5 μm左右,SEM图如图7所示。 图7 电子纸2W2D的a-Si tail SEM图Fig.7 SEM image of 2W2D for electronic paper 3种工艺的a-Si拖尾长度测试结果如图8,采用电子纸2W2D工艺的a-Si拖尾长度较1W1D和非电子纸2W2D分别减少67%和72%,因此,电子纸的2W2D工艺对a-Si拖尾现象改善明显。 图8 不同工艺a-Si拖尾长度测试结果Fig.8 Results of a-Si tail length for different processes 3.2.1 a-Si处理工序建立 尽管降低两次湿刻时间、变更灰化条件改善了a-Si拖尾现象,但是TFT基板沟道特性仍然存在问题,漏电流(Ioff)异常偏大,严重损害产品良率。无论是采用传统的1W1D工艺方法,还是采用改善a-Si拖尾现象后的2W2D方法,这种电子纸产品的Ioff都无法满足正常标准。 这主要是由于与常规LCD显示产品相比,电子纸产品的源漏极金属面积较大,在半色调掩膜曝光后,源漏极金属图形上方均覆盖有光刻胶,因此光刻胶的面积较大,在干刻刻蚀a-Si图形时,刻蚀环境同时具有刻蚀光刻胶的能力,因此光刻胶会分散a-Si刻蚀能力,导致栅极金属边缘出现a-Si残留,SEM图如图9,造成漏电流偏大,无法维持正常像素电压。尽管增加a-Si刻蚀时间,a-Si残留问题有部分改善,但仍然无法彻底解决a-Si残留问题。 图9 a-Si残留SEM图Fig.9 SEM image of a-Si residue 因此,在a-Si刻蚀后我们增加了对残留a-Si的处理工序,并对该工序的功率、压强、SF6、O2、He气体流量开展了5因子2水平的实验设计,其中W3 表2 a-Si处理实验测试结果Tab.2 Results of a-Si experimental treatment 根据实验结果,功率增加,压强降低,SF6流量增加,O2流量增加,He流量降低时,残留a-Si的处理能力更好,阵列检测良率更高。因此,我们采用功率W4、压强P3、SF6流量G4、O2流量G4′、He流量G3″,即条件14,作为电子纸的2W2D工艺a-Si处理条件。经SEM测试证明,该条件刻蚀后无a-Si残留,SEM结果如图10所示。与a-Si刻蚀条件相比,残留a-Si处理条件增加了压强,提升了SF6和O2气体流量,说明增加压强,提升SF6和O2的流量对残留a-Si处理能力更强。 图10 采用残留a-Si处理工序的SEM图Fig.10 SEM image using residual a-Si treatment 3.2.2 a-Si刻蚀与残留a-Si处理时间优化 由于a-Si刻蚀与残留a-Si处理工序均是对a-Si层的刻蚀,如果刻蚀时间较短,会导致a-Si残留无法完全消除;而刻蚀时间较长,则会导致一定程度的栅绝缘层过刻,影响良率。因此,我们对a-Si刻蚀与残留a-Si处理时间进行了不同组合的实验验证,其中T1 表3 不同a-Si刻蚀时间的测试结果Tab.3 Results of different etch time of a-Si 续 表 当无残留a-Si处理过程时,即使a-Si刻蚀时间在可选范围内已达到最高,也存在a-Si残留,良率为0。当增加a-Si处理过程后,随着a-Si处理时间的加长,阵列检测良率均呈现先增加后减小的趋势,a-Si处理工序时间过长会导致栅绝缘层过刻,影响良率。实验结果显示,当a-Si刻蚀时间为T1,残留a-Si处理时间为t2,即条件6,阵列检测良率最高。因此选用条件6为电子纸的2W2D刻蚀条件。 为了进一步提升电子纸的良率,我们对产品的TFT特性进行了改善,即提升Ion,降低Ioff。TFT特性主要与a-Si膜层的膜质和背沟道的界面有关,因此,我们分别对a-Si成膜条件和钝化层前处理条件进行了改善与优化。 3.3.1 a-Si成膜条件改善 不同的a-Si成膜条件会影响膜层的致密程度与缺陷程度,产生不同的电子迁移率,对沟道特性有着至关重要的影响。因此,本实验选用不同的a-Si成膜条件(条件1和条件2)进行验证,采用相同的刻蚀条件,测试TFT特性和阵列检测良率,结果如表4所示。两种成膜条件的工作电流Ion水平接近,但条件2较条件1相比,暗态和光态的漏电流(Ioff)均降低43%,阵列检测良率提升4%。这主要是由于条件2的a-Si膜层较条件1的膜层相对疏松,更有利于消除a-Si残留,降低暗态和光照条件下的Ioff特性,实现良率的进一步提升。 表4 不同成膜条件的测试结果Tab.4 Results of different film conditions 3.3.2 钝化层成膜前处理条件改善 产生漏电流(Ioff)的一个重要因素是TFT器件的背沟道效应,背沟道形成于a-Si和钝化层接触的界面,因此在钝化层成膜前需要对沟道的a-Si表面进行化学处理,以降低背沟道的导电能力,从而降低Ioff,提升良率。其中,钝化层前处理的功率是影响特性的主要参数,因此,本实验对钝化层成膜前处理的功率进行了实验验证(W5 表5 不同钝化层成膜前处理功率的测试结果 Tab.5 Results of different power before passivation deposition 条件功率/W 暗态Ioff/pA 光态Ioff/pA 阵列检测良率1W5I2'I2″Y42W60.78 I2'0.71 I2″1.03 Y43W70.63 I2'0.59 I2″1.06Y4 增大钝化层前处理功率,暗态和光照条件下的Ioff均有降低,其中W7条件最佳,暗态和光照条件下的Ioff分别降低37%和41%,阵列检测良率提升6%。 我们选用最佳a-Si成膜条件2;电子纸2W2D刻蚀条件,即降低两次湿刻时间并搭配灰化条件4,a-Si处理条件14,a-Si刻蚀时间条件6;钝化层成膜前处理条件3,对刻蚀后沟道厚度的均一性进行了验证,与增加了残留a-Si处理工艺的1W1D工艺对比,测试结果如表6所示。电子纸的2W2D工艺在无需管控半色调掩膜胶厚均一性的条件下,刻蚀后沟道均一性较传统1W1D提升50%,使曝光工序的返工发生率降低60%,减少了产能浪费,四周沟道过刻现象彻底改善,阵列检测良率得到了4%的提升。 表6 刻蚀均一性测试结果Tab.6 Results of etching uniformity 我们选用最佳a-Si成膜条件2;电子纸2W2D刻蚀条件,即降低两次湿刻时间并搭配灰化条件4,a-Si处理条件14,a-Si刻蚀时间条件6;钝化层成膜前处理条件3,对3款4次光刻电子纸产品进行了改善验证,与增加残留a-Si处理工艺的1W1D刻蚀及其配套成膜条件的TFT特性与阵列检测良率进行对比,结果如表7所示。两种刻蚀工艺相比,电子纸的2W2D工艺对Ion特性略有提升,对Ioff特性降低明显,使电子纸TFT特性得到了显著提升;同时由于2W2D工艺对a-Si拖尾现象和刻蚀均一性改善明显,使得阵列检测良率提升了4%~10%,这也进一步表明本文提出的电子纸2W2D工艺对4次光刻电子纸产品具有普适性,且较单纯增加a-Si处理条件的1W1D方法均有明显的改善效果。 表7 1W1D与2W2D工艺结果对比Tab.7 Comparisons of 1W1D and 2W2D results 本文通过对非电子纸产品的2W2D工艺进行改善,开发了适合电子纸产品的2W2D工艺。通过降低两次湿刻时间,改善灰化条件,使a-Si拖尾长度降低至0.3 μm;建立a-Si处理条件,消除a-Si残留;调整a-Si成膜条件和钝化层成膜前处理条件,改善TFT特性,最终得出电子纸的最佳2W2D工艺。相比于1W1D方法,改善后的2W2D方法得到的沟道厚度均一性提升了50%,阵列检测良率提升了4%~10%;同时无需管控半色调掩膜光刻胶的均一性,仅满足光刻胶厚度的管控要求即可,使曝光返工比例降低60%,有效地改善了电子纸产品的沟道特性与刻蚀均一性,提升了产品良率,减少了产能浪费,降低了成本,对4次光刻电子纸产品具有重要指导意义。

3.2 a-Si残留改善

3.3 TFT特性改善

3.4 均一性改善验证

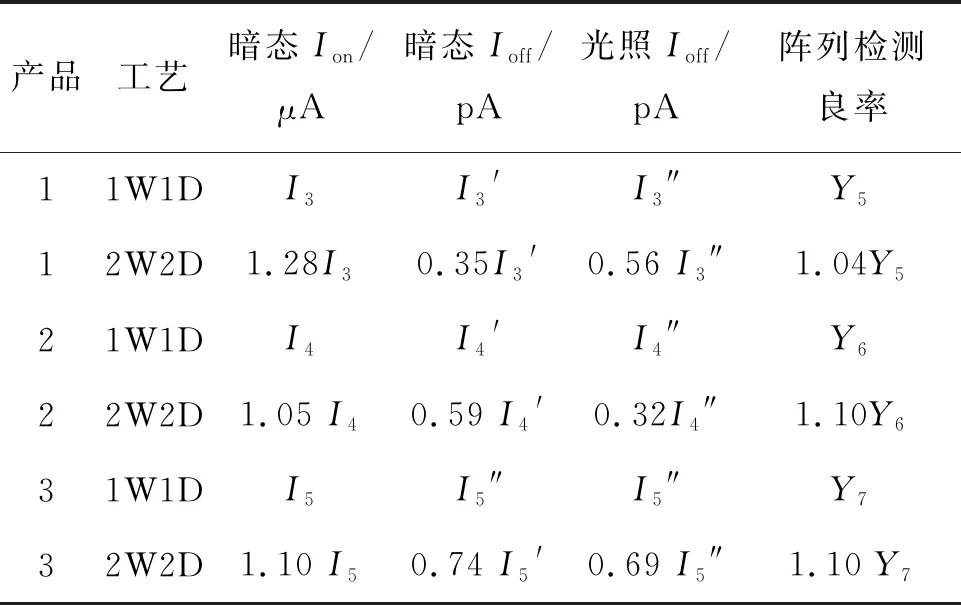

3.5 不同型号产品改善效果验证

4 结 论