薄膜晶体管液晶显示器的点对点传输协议

2020-05-11周明忠张裕桦王念茂徐枫程王拂依肖剑锋

赵 斌,周明忠,张裕桦,王 照,王念茂,徐枫程,王拂依*,肖剑锋

(1. 华南理工大学 电子与信息学院,广东 广州 510640; 2. 深圳市华星光电技术有限公司,广东 深圳 518107)

1 引 言

在平板显示技术中,薄膜晶体管液晶显示器TFT-LCD(Thin Film Transistor-Liquid Crystal Display)技术以其低工作电压、低功耗、长寿命、无辐射和低成本而占据平板显示器市场的主导地位[1-3]。TFT-LCD面板的驱动系统由栅极驱动器GD(Gate Driver)、源极驱动器SD(Source Driver)和时序控制器T-CON(Timing Controller)组成。T-CON将从信号源接收到的同步控制信号和数据信号分别转换为GD和SD所需的输入信号,并通过接口协议将数据信号发送到每个SD。作为当今的主流显示技术,TFT-LCD正朝着大屏幕、高分辨率和高色深的方向发展,使得传输的数据量急剧增加。接口协议的性能直接关系到显示的品味。因此,对于TFT-LCD显示技术来说,接口协议是决定T-CON和SD之间数据信号能否正确传输的关键。

国内外许多公司对T-CON与SD之间的接口协议进行了深入研究。为响应市场需求,接口协议经历了三代发展。第一代接口协议使用TTL或CMOS电平并行传输数据。该协议仅适用于低分辨率、小尺寸TFT-LCD。当数据传输量大且数据传输速率高时,第一代接口协议通常会引起诸如信号串扰、系统功耗和噪声干扰之类的问题。第二代接口协议采用低摆幅差分信号和串行传输的多点总线结构。例如,美国国家半导体公司(NS)和德州仪器公司(TI)分别提出的低摆幅差分信号RSDS( Reduced Swing Differential Signaling)[4]和mini-LVDS(mini- Low Voltage Differential Signaling)[5-6]。一方面,利用信号上升沿和下降沿的双向传输模式,大大提升了信号的时钟频率并减小了信号的总线宽度;另一方面,通过降低信号幅度和传输线数量来降低EMI和功耗[7]。然而,当应用于高级产品时,这种多点总线架构受到严峻挑战。因为屏幕尺寸的增加导致信号的传输线延长,高分辨率导致数据传输速率提升,使负载和寄生效应对信号传输路径的影响更加明显,从而导致信号传输系统的不稳定和传输信号质量的恶化[8-9]。与第二代不同,第三代接口协议使用点对点架构,其中T-CON和每个SD由单独的差分数据对传输。除了保留第二代接口协议的优点之外,点对点结构还大幅减少了传输线的数量,并且信号线阻抗不受SD负载的影响。这些优点确保了基于点对点接口协议的数据传输稳定可靠,可支持大尺寸,高速率,高分辨率,高色深的TFT-LCD[10-11]。以NS基于点对点架构的接口协议提出的PPDS(Point-to-point Differential Signaling)以及三星发布的USI-T(Unified Standard Interface)为代表的传输方式逐步成为高阶TFT-LCD的主流传输方式。随后点对点接口蓬勃发展,包括群创的CMPI(Clock eMbedded Point-to-point Interface)、LG的EPI(Embedded Clock Point-to-point Interface)、BOE的CEDS(Clock Embedded Differential Signal)等,其中USI-T、EPI和CMPI是无编码算法。假若T-CON与SD之间需要传输的是8 bit RGB数据,采用USI-T和CEDS协议传输则每一封包的数据量是10 bit,EPI和CMPI对应的每一封包数据分别为28 bit和27 bit。一个封包的无效数据数量会直接影响操作频率,相同数据量时,无效数据比例越高,需提高操作频率来完成数据传输;此外,也存在传输信道浪费的问题。

基于上述讨论,本文提出了一种新型高速点对点接口协议,称为中国标准点对点接口CSPI(China Standard Point-to-Point Interface)协议,可有效地利用封包格式达到最佳传输速度,并且可有效地使用传输信道。通过实验论证,证实此传输协议可以解决高阶显示面板的频率带宽和信号传输质量问题。

2 CSPI协议架构及其通信原理

2.1 CSPI协议架构

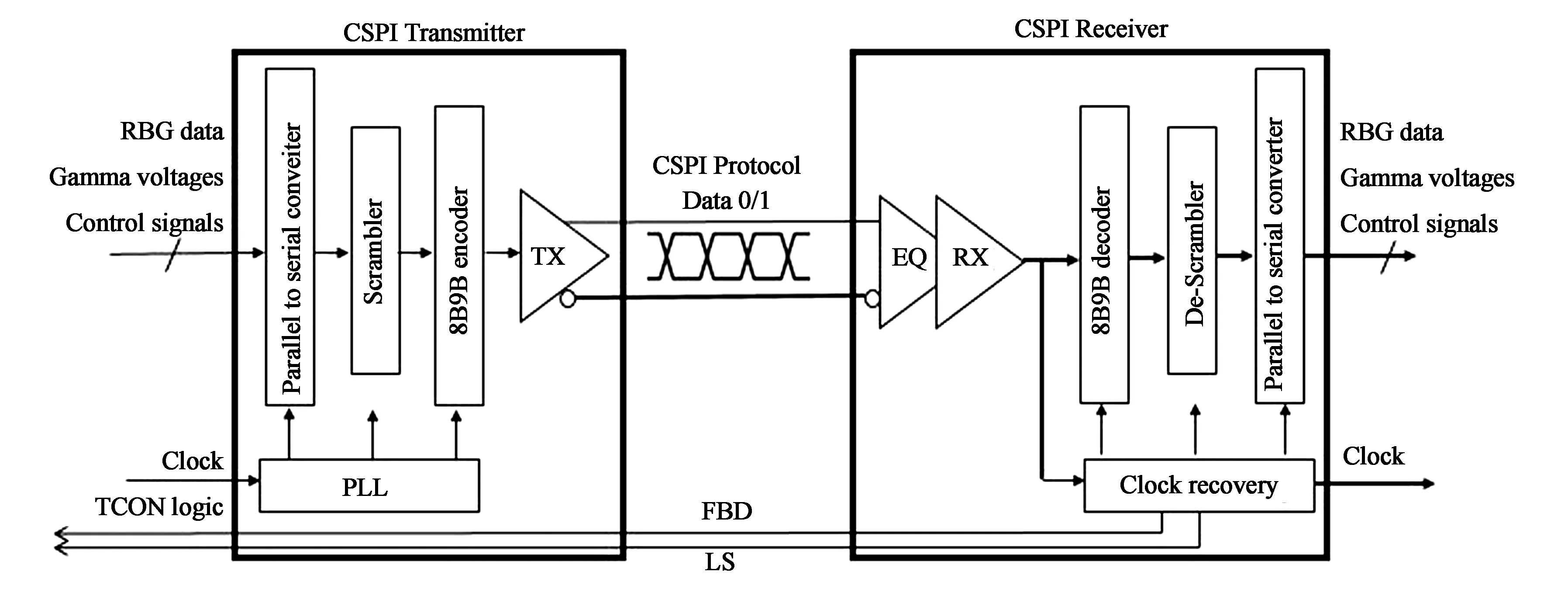

CSPI协议是T-CON和SD之间的高速接口技术,适用于LCD面板显示模块。如图1所示,CSPI协议采用8 B/9 B编码技术实现嵌入式时钟方案,规定了发送器和接收器的基本功能。由于时钟数据恢复CDR( Clock Data Recovery)接收器的兼容性,CSPI协议的加扰器/解扰器技术通常被称为扩频技术,是一种有效的降噪方法。 输入数据首先在CSPI发送器TX(Transmitter)和输出数据流中实现加扰和编码。CSPI接收器RX( Receiver)接收数据并实现解扰和解码。

图1 中国标准点对点接口框图Fig.1 CSPI block diagram

2.2 CSPI协议通信原理

点对点连接是指两个节点之间用于数据传输的通信连接。CSPI规定了8位/9位接口协议的基本功能:发送端TX发送功能;接收端RX接收功能。CSPI接口传输协议定义 时钟通道被嵌入到数据通道中,系统架构如图2所示。

在指定的应用中,数据通道的数目是可选的,决定数据通道数目的因素如下:视频流带宽;每个数据通道的最大带宽;指定应用中每个源极驱动芯片的最大带宽。

在规定的接口传输协议中,不同的应用,可分别采用一个通道(T-CON和SD之间仅有一对差分信号)和两个通道(T-CON和SD之间有两对差分信号)的方案。

指令通道LS(Link Status)是一条单端信号线,LS由外部拉高,当所有的源极驱动芯片接收状态为锁定时钟频率,源极驱动芯片会呈现高输入阻抗,当所有的源极驱动芯片都锁定后,LS将被外部电路拉高,让T-CON可以进入下一个状态。当源极驱动芯片接收状态失锁,源极驱动芯片内部会拉低,所以只要有任何一颗源极驱动芯片拉低,LS的脚位状态就会呈现为低,T-CON会持续送时钟校准指令。回传数据FBD(Feedback Data)是一条单端信号线,FBD 由外部拉高,当源极驱动芯片传输数据会将FBD拉低,再进行数据传输。

在本部分中规定的接口传输协议中,在物理层通道中串行传输编码数据。编码之后,每字节(8位)数据转换为9位。在T-CON和每一颗源极驱动芯片SD之间的物理层通道定义为端口(Port)。如果在T-CON与源极驱动芯片之间有一组差分信号线,这个端口定义为1-Port;如果在T-CON与源极驱动芯片之间有两组差分信号线,这个端口定义为2-Port。

接口传输协议中,遵从低位优先原则,例如最低位的字节(0位)首先传输,在每一个字节中,最低有效位LSB(Least Significant Bit )首先传输,最高有效位MSB(Most Significant Bit)最后传输。这一规则同时适用于数据传输和控制指令传输。

3 CSPI协议设计

3.1 CSPI发送协议设计

图3描述了发送端协议层、物理层的架构。

图3 发送端架构Fig.3 TX function module diagram

发送端共有5个工作状态:关机状态、上电后等待状态、时钟校准状态、特定对位封包对位状态和显示输出状态,如图4所示。

(1) 在上电后,TX进入系统稳定与TX配置阶段。在该阶段中,应等待TX初始化配置完成,例如加载配置信息,TX 锁相环PLL锁定等。

(2) CDR校准,即TX、RX时钟校准状态,CDR校准完成后,LS信号输出高电平给T-CON,通知发送端可以传输下一阶段的数据。

(3) 若CDR 校准失败,会处于失锁状态,LS信号输出低电平给T-CON,再重新做CDR校准。

图4 发送端流程Fig.4 TX working model conversion relationship

3.2 CSPI接收协议设计

图5描述了接收端协议层、物理层的架构。

图5 接收端架构Fig.5 RX function module diagram

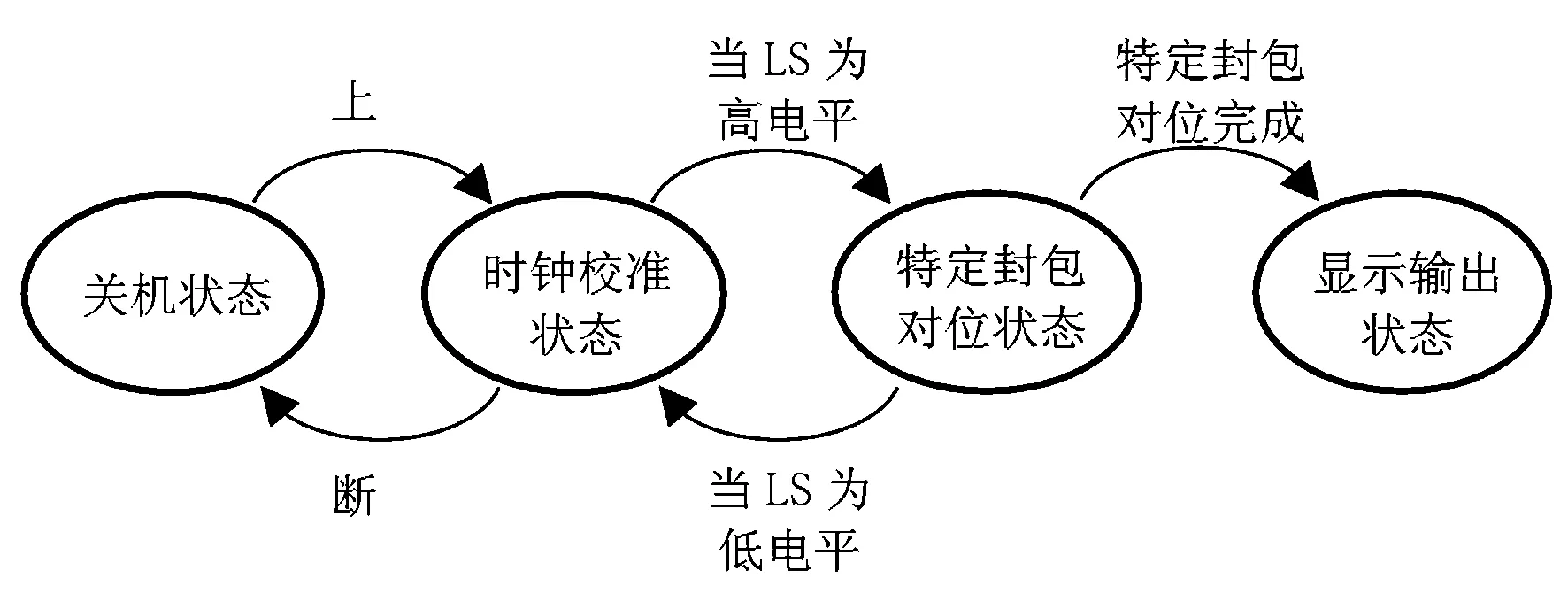

接收端共有4个工作状态:关机状态、时钟校准状态、特定对位封包对位状态和显示输出状态,如图6所示。

(1)在上电后,接收端进行时钟校准,时钟校准完成后,接收端输出LS信号高电平给发送端,通知发送端可以传输下一阶段的数据。

(2)若时钟校准失败,接收端会将LS信号拉低,输出LS低电平给发送端,发送端重新发送时钟校准。

(3)特定封包对位状态,可由数据中的标头指令封包或标尾指令封包进行数据对齐,对位完成后,接收端就可正常输出画面。

图6 接收端流程Fig.6 RX working model conversion relationship

3.3 CSPI编码和解码设计

3.3.1 设计概述

显示系统主要参数包括源极驱动芯片数量、每个端口的通道数、发送端和接收端之间的传输速率等。这些参数符合如下关系:

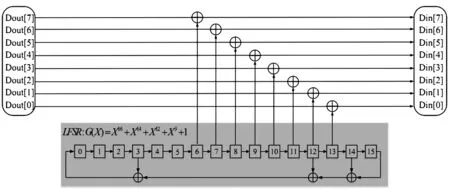

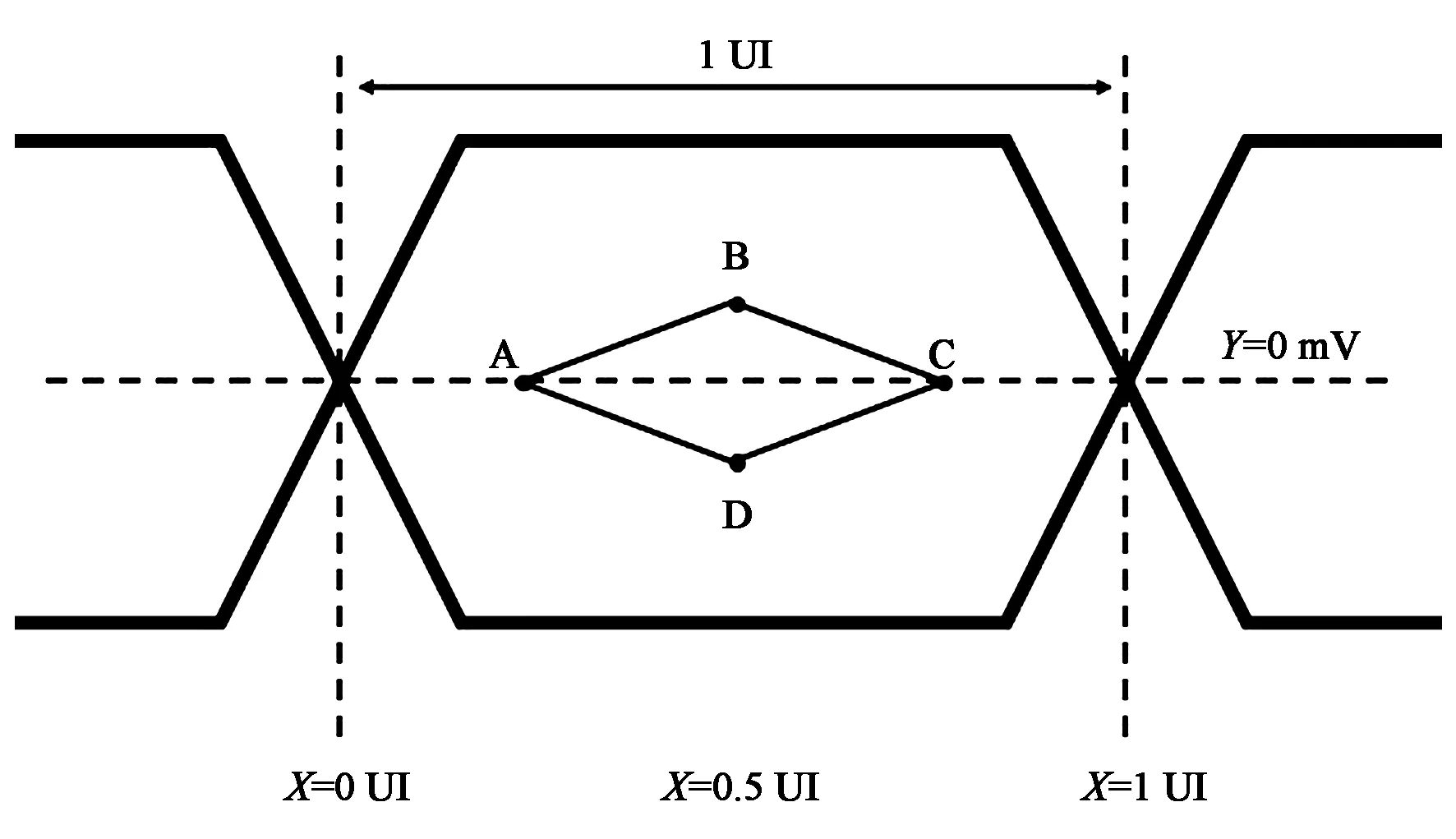

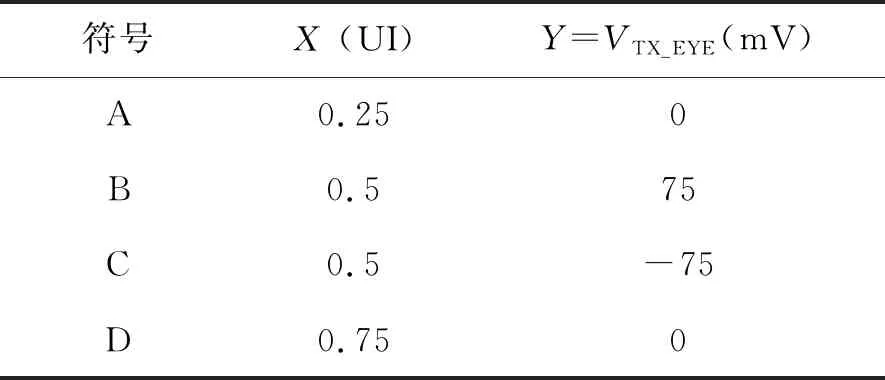

BPP×FP×1.125 (1) 其中:BPP表示每像素包含数据比特数,FP表示像素时钟频率,LC表示每端口差分线数量,LS表示传输速率,SDC表示源极驱动芯片数量,0.95表示用于补偿展频功能带来的临时性的带宽损耗,1.125表示8位/9位带来的带宽损耗。 所有高于703.8 Mb/s的连接速率都可使用。考虑到高速传输的成本影响及功率损耗,选择接近最低速率的参数。 3.3.2 CSPI编码设计 CSPI协议采用8 B/9 B编码技术实现时钟嵌入功能。首先对原始数据进行质量判断,然后根据编码算法将原始的8位数据编码为9位,使数据中连续0或1的长度控制在5以内,最终保证信号质量。8位/9位编码流程如图7所示。 图7 编码流程图Fig.7 Flowchart of encoding algorithm 其中:bm[0~7] 表示原始数据的第0位至第7位,bn[0~8] 表示编码数据第0位至第8位,NAND表示逻辑运算与非,OR表示逻辑运算或,~表示逻辑运算非,=表示赋值。 3.3.3 CSPI解码设计 解码是编码的逆过程。主要通过判断及逻辑运算再忽略标志位来实现9位转换为8位目的,最后恢复得到原始数据。8位/9位解码流程如图8所示。 图8解码流程图Fig.8 Flowchart of decoding algorithm TX端执行8 B/9 B编码之前,对原始信号进行加扰。数据加扰可以将信号频率点打散,即将能量分散,达到降低EMI的目的。在数据加扰功能开启时,T-CON发送加扰数据给SD,SD必须解扰码才能获取真实的视频显示数据。CSPI扰码多项式设计方法如图9、10所示。 其中,S[1]~S[15]是扰码密钥,Din[0]~Din[7]是扰码数据,Dout[0]~Dout[7]是解扰码数据。 S[5] XOR Din[7]=Dout[7] S[6] XOR Din[6]=Dout[6] S[7] XOR Din[5]=Dout[5] S[8] XOR Din[4]=Dout[4] S[9] XOR Din[3]=Dout[3] S[10] XOR Din[2]=Dout[2] S[11] XOR Din[1]=Dout[1] S[12] XOR Din[0]=Dout[0] XOR表示逻辑运算异或。 图9 加扰多项式设计Fig.9 Scrambler key generator 图10 解扰多项式设计Fig.10 Descrambler key generator 图11 CSPI验证平台Fig.11 Experimental platform of the CSPI protocol 基于1 383 mm(55 in)超高清LCD面板的实验平台,验证CSPI高速传输协议性能和质量。硬件平台搭建如图11所示。 眼图是评估信号质量的最有效和最直接的方法,眼睛“开口”的幅度和宽度是衡量基带传输系统性能的指标[12]。眼睛张得越大且眼图越端正,表示码间串扰越小,信号质量优;反之表示码间串扰越大,信号严重失真。眼图模板Mask是判断眼图测量结果的主要依据,Mask规定了串行信号“1”电平的容限,“0”电平的容限,上升时间、下降时间的容限。CSPI信号眼图Mask规格标准设定如图12所示。 符号X (UI)Y=VTX_EYE (mV)A0.250B0.575C0.5-75D0.750 图12 CSPI眼图规格 图13 实验平台实测的眼图Fig.13 Eye diagram measured on the experimental platform 图13展示了传输速率约为1.4 Gb/s时终端电阻输出端的实测眼图。眼图结果表明,眼睛“开口”的最小幅度和宽度分别约为312 mV和548 ps,符合规格要求的同时并保有足够余量。测量结果表明:即使数据传输速率高达1.4 GMb/s,CSPI协议仍可稳定地工作,且信号质量良好,抖动小。这主要得益于CSPI使用点对点架构,极大改善了信号完整性问题。 本文提出了一种名为CSPI的点对点高速传输协议。通过测量的1 383 mm(55 in)超高清(UHD)LCD面板眼图,眼图中眼睛“开口”的最小幅度和宽度分别约为312 mV和548 ps,符合规格要求并保有余量。测量结果表明,CSPI协议具有高传输速率,低EMI性能和较少信号线数量的突出特性,特别适用于高级TFT-LCD。这对于TFT-LCD在各种特殊领域的广泛应用具有深远意义。

3.4 CSPI扰码设计

4 实验数据与结果

Fig.12 Eye diagram specification of CSPI

5 结 论