多通道NAND Flash存储芯片控制器的设计与实现

2018-08-23陈万培

陶 莉,陈万培

(扬州大学 信息工程学院,江苏 扬州 225000)

0 引言

随着信息产业的飞速发展,各个行业对数据存储的要求越来越高,基于闪存技术的NAND Flash存储芯片由于价格低、体积小以及效率高的优势,广泛应用于现代数码产品以及固态硬盘等媒体设备。作为高密度静态可扩展存储器,NAND Flash存储芯片在大容量高速数据存储系统中占据主流地位[1-2]。

采用NAND Flash存储芯片作为存储介质的固态盘,比传统的存储设备更能承受温度的变化、机械的振动和冲击,同时具有耗电少、存储密度提升快、可靠性更高的优点,易于实现高速度大容量的存储[3-8]。NAND Flash存储芯片结构每比特成本低,具有更高的性能,并且能像磁盘一样可以通过接口轻松升级[9-13]。另外,NAND Flash存储芯片的封装尺寸在不断减少,而存储容量每年会提高3~4倍[14-17]。由于NAND Flash存储芯片复杂的接口操作,设计了一种与其时序相吻合的NAND Flash存储芯片控制器。为了提高数据存储容量和存取速度,文献[18-20]采用的是多个控制器来操作多片NAND Flash存储芯片,这样设计方案在多个控制器之间同步问题比较明显,接口复杂性也较高。基于此,本文提出了以单个控制器为基础,进行数据总线扩展,从而并行地控制多片NAND Flash存储芯片。同时加入了流水线技术和乒乓操作,进一步提高数据存取速度。

1 NAND Flash控制器结构

基于FPGA可扩展的NAND Flash存储芯片控制器的设计与测试系统结构如图1所示。

图1 NANDFlash控制器结构

整个测试系统由主机控制模块和NAND Flash存储芯片控制器模块组成。NAND Flash存储芯片控制器作为设计的核心包括1个逻辑控制模块、2个数据缓冲区以及寄存器组。主机控制模块相当于用户端,用来发送命令给NAND Flash存储芯片控制器。NAND Flash存储芯片控制器主要产生与NAND Flash存储芯片相吻合的时序并且直接控制NAND Flash存储芯片。为了能够并行操作4组NAND Flash存储芯片,将NAND Flash存储芯片控制器与外设NAND Flash存储芯片之间的控制信号及状态信号均扩展为4组,数据线扩展为32 bit。将测试系统下载到FPGA里,通过板卡上的高速接口与NAND Flash存储芯片连接,即可方便地进行复位、读ID、擦除、写和读的基本操作。

2 NAND Flash控制器总体设计

NANDFlash存储芯片控制器主要采用状态机并且利用Verilog HDL语言设计完成的。逻辑控制模块是控制器的关键,用于产生符合要求的操作时序以及状态间的转换,2个数据缓冲区模块用于数据的缓存以及实现乒乓操作,寄存器组用于存放NAND Flash存储芯片的内设命令、状态、地址和配置参数。

2.1 主状态机设计

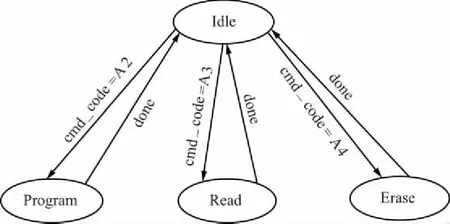

主状态机主要由6个状态组成,如图2所示,分别是空闲状态、复位状态、读ID状态、擦除状态、编程状态和读状态。

图2 主状态转移

在系统完成复位状态之后,主状态将进入空闲状态,等待使能信号的到来从而进入下一个状态。当接收到使能信号后,状态具体的转移是由命令码的值(cmd_code)决定的。如果命令码cmd_code=A2,那么状态跳转到编程状态并且执行相应的子状态,在该状态完成之后发出完成标志done信号给主状态,这时主状态会进入空闲状态并且等待下一个使能信号的到来。如果命令码cmd_code=A3或者A4,流程和命令码cmd_code=A2执行过程类似。

2.2 擦除状态的设计

NANDFlash存储芯片控制器的块擦除状态转移图如图3所示。对于NAND Flash存储芯片来说,在写入数据之前必须进行块擦除操作。

首先,NAND Flash存储芯片控制器接收到主机发送的命令字60H,表示开始对NAND Flash存储芯片进行块擦除操作。主机发出3 Byte地址来决定具体待擦除的块,之后NAND Flash存储芯片控制器内部发出命令字D0H,即真正的擦除操作开始,随后状态信号R/B#变为低电平,表明块擦除操作正在进行中,当状态信号R/B#变为高电平,说明擦除操作完成。

2.3 页编程状态的设计

NANDFlash存储芯片控制器的页编程状态转移图如图4所示。

图4 页编程状态转移

首先切换一个待编程的缓冲区,用来做数据的缓存,主机发送一页数据8 KB给数据缓冲区,随后发出命令80H给NAND Flash存储芯片控制器表示开始页编程操作,由于NAND Flash存储芯片读写的最小单位是页,所以只要发送3 Byte地址来表示需要编程的页地址,NAND Flash存储芯片控制器接收到地址和命令后,把数据缓冲区里的数据写到NAND Flash存储芯片的寄存器里。在NAND Flash存储芯片控制器发出命令字10H后,NAND Flash存储芯片将会自动编程,状态信号R/B#将进入低电平并且在这个过程中R/B#信号一直保持低电平。在编程操作完成后,状态信号R/B#进入高电平。通过状态寄存器的值来检测整个操作是否成功完成。

2.4 页读状态的设计

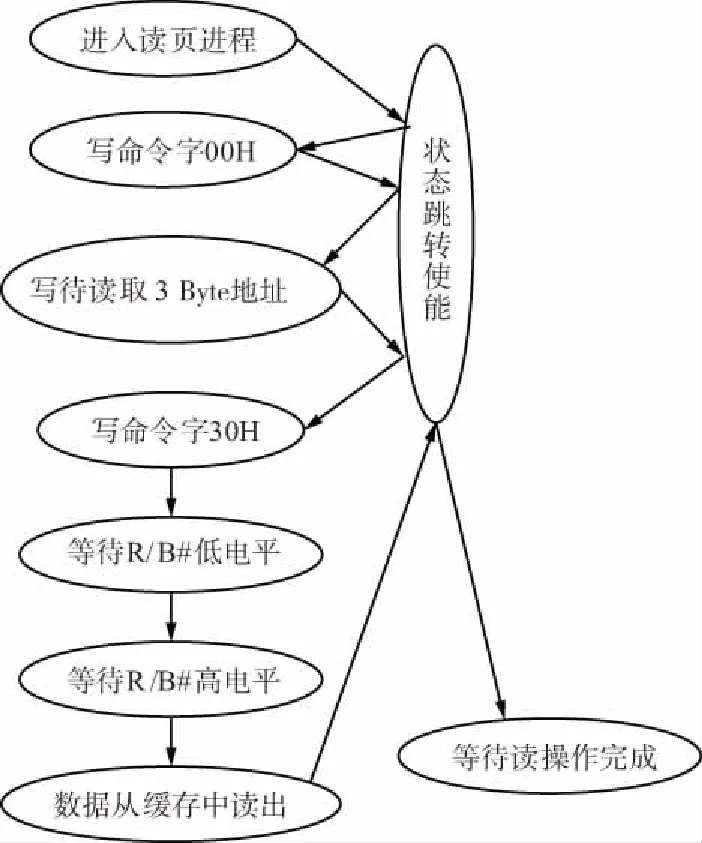

NANDFlash存储芯片控制器的读页状态转移如图5所示。

图5 页读状态转移

主机发送命令字00H给NAND Flash存储芯片控制器开始读页操作,同时向NAND Flash存储芯片控制器发出3 Byte页地址,在NAND Flash存储芯片控制器发送命令字30H后,NAND Flash存储芯片进行内部处理,此时状态信号R/B#变为低电平,在此过程中NAND Flash存储芯片控制器从NAND Flash存储芯片中将一页数据加载到数据缓冲区里,一旦状态信号R/B#变为高电平之后,表明控制器已经将整页数据全部读进数据缓冲区里,此时缓存区里的数据可以被主机取走,等待所有数据被主机读完,操作完成。

2.5 乒乓操作

NANDFlash控制器内部采用了2个单端口的RAM作为双数据缓冲区,来实现乒乓操作,这样节省了用户的等待时间,有效地提高了数据的访问速度。本次设计中,每个缓冲区大小为8 KB,数据线I/O口大小为32 bit。例如,在写操作时,对地址为0xFF8的寄存器的最低位设置为“0”,表示选择缓冲区A,主机向其写入8 KB后交给NAND Flash存储芯片控制器操作,这时控制器对NAND Flash芯片进行写操作,同时控制器将地址为0xFF8的寄存器的最低位设置为“1”,表示选中缓冲区B,主机向其写入8 KB,等待上一周期的写操作完成,一旦写操作完成后,主机将缓冲区B交给控制器,控制器将缓冲区A交给主机,即进行缓冲区交换,这时控制器再次进入写操作,需要将缓冲区B里的所有数据写入NAND Flash芯片,此时主机向缓冲区A写入8 KB,如此交替循环。

数据双缓冲技术实现了输入数据和输出数据都是连续不断地,因此非常适合对数据流进行流水线处理。

3 实验和结果分析

3.1 实验环境

本系统是基于Verilog HDL语言设计完成的,并且在FPGA开发板上进行了验证。开发板选用的是Cyclone V,系统时钟设定为50 MHz,NAND Flash芯片选用的型号是MT29F64G08。为了分析系统内部的实时数据,这里借助Signal Tap II逻辑分析仪来捕获信号波形,将Signal Tap II逻辑分析仪的采样时钟设置为50 MHz,和开发板系统时钟保持一致。整个实验对整个系统分别进行了功能验证和性能验证。

3.2 功能性验证

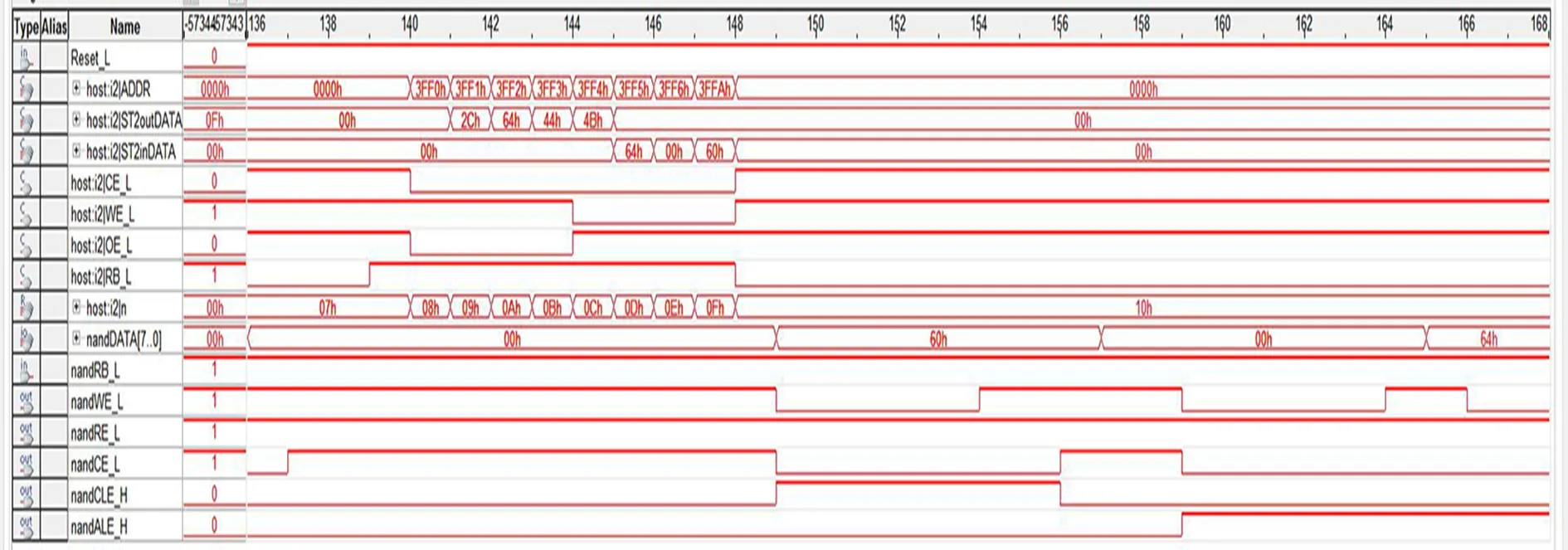

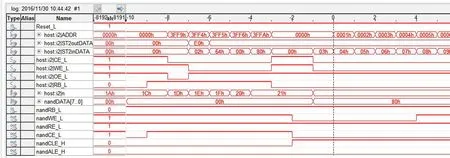

功能性验证是基于单片NAND Flash芯片完成的,对读、写和擦除状态进行了验证,实验结果如图6、图7和图8所示。通过对结果进行分析,所设计的NAND Flash控制器的读写和擦除操作的时序完全吻合NAND Flash芯片的时序,即控制器能够正确操作NAND Flash芯片,从而得出所设计的NAND Flash存储芯片控制器在功能上符合要求。

由图6可知,采样点从144~148,主机发出第64块的块地址,同时发出擦除命令60H给NAND Flash存储芯片控制器,经过若干个周期后,在采样点9处NAND Flash芯片接收到控制器发来的擦除命令,并且开始执行块擦除操作。

由图7可知,在采样点-8处,主机从地址为3FF9H的状态寄存器中读回状态值为E0H,表示NAND Flash芯片是准备就绪的,采样点-7~-3这4个时钟周期里,主机发送3 Byte地址值(第64块中的第2页的地址)以及写命令80H。当采样点在-1处时,主机向控制器中的数据缓冲区写入8 KB,在控制器发出命令10H后,NAND Flash芯片进入写操作。

由图8可知,在采样点-9处,主机从地址为3FF9H的状态寄存器中读回状态值为E0H,表示NAND Flash芯片是准备就绪的,采样点-8~-4这4个时钟周期里,主机发送3 Byte地址值(第64块中的第2页的地址)以及读命令00H。3个时钟周期后,控制器发送写命令30H给NAND Flash芯片,NAND Flash芯片接收到命令之后开始进行读操作,8 KB全部从缓冲区里正确读出,这表明所设计的控制器完全符合系统功能要求。

图6 擦除状态采样图

图7 写状态采样图

图8 读状态采样图

3.3 性能评估

在完成功能测试与验证之后,进一步地对NAND Flash存储芯片控制器进行性能测试。针对读写操作,表1和表2分别给出了单片NAND Flash芯片页写操作和页读操作所用的时间。

表1 页写时钟数

测试ID号时钟数平均时钟数133 743230 933333 762430 941530 989633 80132 361.5

从表1可以看出,在写操作时,不同的页需要的时间是不同的,因此时间平均值32 361.5作为衡量的指标参数,由于页的大小是8 KB,时钟频率是50 MHz,因此写操作的速度是12.7 MB/s。同样,从表2可以看出,读操作所用的时间平均值是2 617.8,速度是156.5 MB/s。对于多片NAND Flash芯片并行结构,写速度可以达到50.8 MB/s,读速度可以达到626 MB/s。

表2 页读时钟数

测试ID号时钟数平均时钟数12 54522 54032 65942 64652 66662 6512 617.8

4 结束语

本文针对NAND Flash存储芯片接口复杂、不适合直接对其进行数据的存储与读取的问题,提出了一种符合NAND Flash存储芯片时序的控制器来对其直接操作,该控制器是基于FPGA设计的,采用状态机思想实现。为了进一步加快数据存储与读取速度,并且加大数据的存储量,本文采用了多片NAND Flash并行结构将数据位扩展到32位,设计了2个数据缓冲区,实现了双数据缓冲。今后将针对提高NAND Flash存储芯片的读写速度方面展开更为深入的研究。