基于FPGA的1553B总线曼彻斯特编解码器设计与实

2018-06-19现潘亮司斌张从霞张鹏

现潘亮 司斌 张从霞 张鹏

摘要: 曼彻斯特码作为一种数字编码技术, 具有自带时钟、 无直流分量等优点, 在数字通信系统中具有广泛的应用。 本文在分析曼彻斯特编解码原理和1553B总线协议以及收发器HI-1573工作时序的基础上, 利用ISE14.7开发环境, 采用VHDL语言, 基于Xilinx公司Spartan6型FPGA实现通用型和可定制的曼彻斯特Ⅱ型编解码器设计, 并通过ISE Simulator和XST进行时序仿真和综合优化, 仿真结果验证了设计方案的逻辑功能。 最后搭建UART硬件测试平台, 验证了设计方案的硬件可实现性。

关键词: 曼彻斯特码; 编解码原理; 1553B总线; VHDL; FPGA

中图分类号: TJ760; TP336文献标识码: A文章編号: 1673-5048(2018)02-0083-06

0引言

曼彻斯特码是一种传统、 经典的数据编码技术, 也叫相位编码(Phase Encoding), 具有自带时钟的特性, 是一种同步时钟编码技术, 能够很好地解决数字通信系统中同步难题。 按照编码原理及实现算法[1]的不同, 曼彻斯特码可以分为三种: 曼彻斯特双相电平码、 曼彻斯特Ⅱ型双相电平码以及差分曼彻斯特双相电平码, 可简称为曼彻斯特Ⅰ型码、 曼彻斯特Ⅱ型码和差分曼彻斯特码。 曼彻斯特码是在NRZ码(NonReturn to Zero, 非归零码)的基础上发展起来, 采用具有无直流分量特性的编码技术, 在电信业、 工业现场控制、 车辆总线及石油勘测等领域具有广泛的应用。

MILSTD1553B是美国关于数据总线传输的军方标准。 总线协议规定, 采用曼彻斯特Ⅱ型码作为1553B总线的数字编码技术标准[2], 因此, 曼彻斯特编解码器性能的好坏将直接影响1553B总线的通信质量。

目前FPGA集成了丰富的可编程器件门电路和部分IP核, 具有精确的时序处理能力, 在高速信号处理中应用广泛。 1553B总线曼彻斯特编解码器工作在兆赫兹以上, 对时序的要求比较高, 因此, 本文采用FPGA设计曼彻斯特编解码器。 其设计输入的硬件描述语言 VHDL于1987年被IEEE确认为国际标准, 具有设计的灵活性和器件定义的严谨性以及强大的行为级抽象描述能力, 在数字系统设计领域具有广泛的应用, 因此本文采用VHDL实现FPGA开发的设计输入。

1曼彻斯特Ⅱ型码

1.1曼彻斯特码编码原理

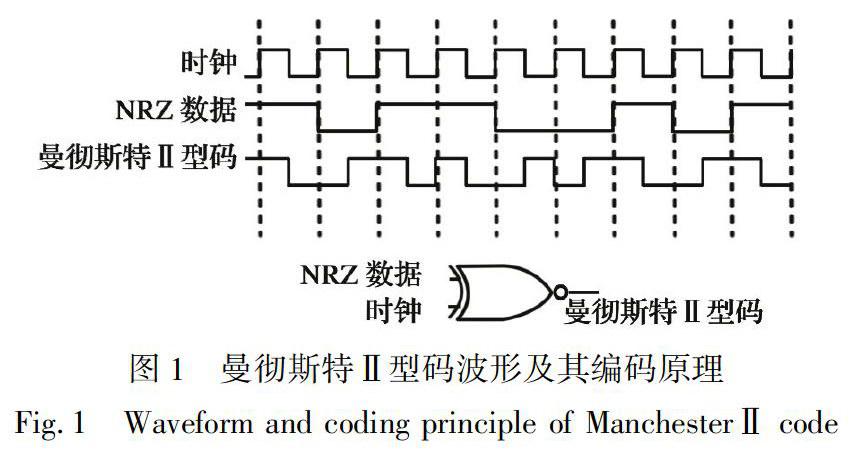

曼彻斯特码是用脉冲序列来表示数据“1”和“0”, 而脉宽是码元宽度的一半。 在曼彻斯特Ⅱ型码中, NRZ码元1对应于脉冲电平由高电平跳变到低电平; NRZ码元0对应于脉冲电平由低电平跳变到高电平, 在传输码元的中间时刻含有一个记录时钟信息的跳变, 因此说曼彻斯特码具有自带时

收稿日期: 2017-04-26

作者简介: 潘亮(1987-), 男, 河南洛阳人, 硕士研究生, 研究方向是嵌入式航空电子设备总线和嵌入式系统开发。

引用格式: 潘亮, 司斌, 张从霞, 等. 基于FPGA的1553B总线曼彻斯特编解码器设计与实现[ J]. 航空兵器, 2018( 2): 83-88.

Pan Liang, Si Bin, Zhang Congxia, et al. Design and Implementation of the 1553B Bus Manchester Code Based on FPGA[ J]. Aero Weaponry, 2018( 2): 83-88.( in Chinese)

钟的特征。 曼彻斯特Ⅱ型码的波形图如图1所示。

图1曼彻斯特Ⅱ型码波形及其编码原理

Fig.1Waveform and coding principle of ManchesterⅡ code

从图1的时序波形可以看出, 曼彻斯特Ⅱ型码是将NRZ码元与其编码时钟电平同或处理得到。 同或是指当两输入电平同为“1”或“0”时, 运算结果是逻辑1; 而输入电平不相同时, 运算结果是逻辑0。 由其逆向运算可知, 曼彻斯特Ⅱ型码的基本解码算法是将得到的曼彻斯特码与同步的编码时钟电平同或处理, 即可得到NRZ码元。

1.2曼彻斯特编解码器与1553B总线通讯

1553B总线规定[2], 协议字分为数据字、 命令字和状态字, 其位长是20, 包括同步头、 有效数据和奇校验三部分[3], 如图2所示。 其中, 同步头波形占据3个位宽, 有效数据为16位, 最后1位是前16位数据的校验码(协议规定采用奇校验)。 从图中看出, 数据字的同步头波形是先低后高, 而命令字和状态字的同步头是先高后低。

图21553B总线规定的3种协议字组成

Fig.2Three protocol words specified in the 1553B bus

曼彻斯特编解码器的功能是实现协议字和曼彻斯特码之间的相互转换。 曼彻斯特编码器将1553B协议终端的待发送数据, 经过编码后以曼彻斯特码的形式正确地发送给1553B总线专用收发器[4]HI-1573。 曼彻斯特解码器将对从收发器HI-1573接收到的数据进行解码, 提取出1553B总线协议规定的同步头和协议数据, 然后发送给1553B协议终端[2-5], 同时对可检测的错误进行必要的标记。

1.3曼彻斯特码在1553B总线中的波形

根据曼彻斯特Ⅱ型码的编码原理以及1553B总线协议[2], 传输线上不跳变电平的码元组合[6]有8种, 分别是“0000”, “1111”, “111”, “000”, “11”, “1”和“00”以及“0”。 1553B总线的位时钟为1 MHz, 曼彻斯特Ⅱ型码的一个码元宽度是0.5 μs。 因此, 传输线上曼彻斯特Ⅱ型码的电平脉宽为500 ns, 1 000 ns, 1 500 ns和2 000 ns。 其中脉宽1 500 ns出现在同步头电平中, 而脉宽2 000 ns出现在随后的数据位与同步头电平相一致的同步头电平中; 脉宽500 ns和1 000 ns出现在数据位电平中, 由正反向数据以及排列组合关系可知有8种组合。 同步头和数据位的脉宽类型如图3~4所示。

航空兵器2018年第2期潘亮, 等: 基于FPGA的1553B总线曼彻斯特编解码器设计与实现图3曼彻斯特Ⅱ型码同步头脉宽类型

Fig.3Pulse width types of synchronization head in

Manchester Ⅱ code

图4曼彻斯特Ⅱ型码数据位脉宽类型

Fig.4Pulse width types of data in Manchester Ⅱ code

2曼彻斯特编解码器

曼彻斯特Ⅱ型编解码器按功能可划分为编码时钟、 编码器控制器和解码时钟以及解码器控制器。 不同的1553B协议终端, 如总线监视器、 总线控制器、 总线终端, 其功能会有差别。 总线监视器不具有总线数据发送功能, 但另三种协议终端发送或接收数据均可通过曼彻斯特编解码器实现, 因而具有一定的共性特征, 如编解码器使能、 奇偶校验、 同步头和数据位等, 可据此进行通用化设计, 通用的编解码器应具有协议规定的字核实、 同步头收发、 数据位收发等功能。

2.1编解码时钟的设计

1553B协议允许的时间误差范围为150 ns, 因此最坏情况下, 曼彻斯特Ⅱ型码电平脉宽为500±150 ns, 1 000±150 ns, 1 500±150 ns和2 000±150 ns。 在采样时钟的选取中, 为了保证时钟沿的一致性和提高抗干扰性, 采样时钟常取位时钟的4, 8或10倍。 1553B协议规定, 数据传输的比特率是1 Mbps。 因此, 若采样时钟为8 MHz时, 脉宽计数器的计数值范围分别是2~5, 6~9, 10~13和14~17; 若选10 MHz, 脉宽计数器的取值分别是3~6, 8~11, 13~16和18~21; 若选16 MHz, 脉宽计数器的取值分别是5~10, 13~18, 21~26和29~34。 设计中若采用8 MHz的采样时钟, 计数器的计数误差可能会导致解码错误; 同时若采用更高倍如16 MHz的采样时钟, 虽然会降低计数误差导致的解码错误概率, 但由于计数器的计数范围大, 会浪费一部分寄存器资源。 综合各种因素, 采用10 MHz的编解码时钟。

2.2编码器设计

根据曼彻斯特Ⅱ型码的编码原理, NRZ码元1对应于脉冲电平由高电平跳变到低电平, NRZ码元0对应于脉冲电平由低电平跳变到高电平。 因此每一位NRZ数据的上半脉冲沿与NRZ数据的电平相同, 而下半脉冲沿与NRZ数据的电平相反, 即取非运算, 因此, 可考虑将待发送数据转化为脉冲数据的上半沿和下半沿。 这是设计曼彻斯特Ⅱ型码编码器的主体思想。

在设计编码器时, 考虑到编码器的通用性和可扩展性, 设计了消息帧长、 发送使能设置和FIFOs地址自增等功能, 同时分别实现同步头、 数据位发送及校验位的发送。 设计中采用2个16位串行移位寄存器分別实现正向数据和反向数据的串行发送。 基于以上考虑, 本文设计了有限状态机实现时序逻辑的转换。

编码器的有限状态机为IDLE, START, WAIT, SHIFT1, WAIT1, SHIFT2, WAIT2, CHECK和CHECK_WAIT以及STOP等10个状态, 其之间的状态转换如图5所示。

各个状态的功能如下:

(1) IDLE: 空闲态, 系统初始化处于该空闲态, 同时一个合法字发送完成以及一帧发送完成后, 都返回该态; 当检测到发送命令, 进入同步头发送的START态。

(2) START: 开始态, 根据发送字同步头准备待发送同步头数据, 完成后自动进入WAIT态。

(3) WAIT: 等待同步头发送态, 设计一个6位的移位寄存器, 逐位发送同步头; 当位计数到7时, 进入SHIFT1态。

图5编码器状态机转换图

Fig.5Transition diagram of state machine in encoder

(4) SHIFT1: 移位有效字的脉冲上半沿态, 设计一个16位的移位寄存器, 按照时序逻辑逐位移位, 准备脉冲上半沿; 完成后自动进入WAIT1。

(5) WAIT1: 等待脉冲上半沿发送态, 按照时序逻辑发送有效字的脉冲上半沿, 并逐位判断位计数是否到39。 若到了, 则进入CHECK态; 若未到, 则进入SHIFT2态。

(6) SHIFT2: 移位有效字的脉冲下半沿态, 设计一个16位的反相移位寄存器, 按照时序逻辑逐位移位, 准备脉冲下半沿; 完成后自动进入WAIT2。

(7) WAIT2: 等待脉冲下半沿发送态, 按照时序逻辑发送有效字的脉冲下半沿, 并逐位判断位计数是否到39。 若到了, 则进入CHECK态; 若未到, 则进入SHIFT1态, 即进行16位有效字的循环发送。

(8) CHECK: 校验态, 将SHIFT1态16位移位寄存器生成的奇校验准备成奇校验位的脉冲上下半沿, 完成后自动进入CHECK_WAIT态。

(9) CHECK_WAIT: 等待校验发送, 逐位发送校验的脉冲上下半沿, 并判断校验计数是否到1。 若等于1, 则进入STOP态; 若没有, 则进入CHECK态进行校验发送。

(10) STOP: 停止态, 初始化几个位计数, 有效字计数自加, 自动进入IDLE态。

2.3解码器设计

解码器的关键技术是实现同步头的识别。 1553B协议规定, 同步头位长为6, 时长为3 μs; 考虑到HI-1573专用收发器的工作机理[7](如图6所示), 若先检测到正向端高电平, 说明接收到命令字或状态字的同步头; 而先检测到反向端高电平, 说明接收到数据字同步头。 当采用10 MHz 的采样时钟进行脉宽检测时, 对同步头的采样计数范围是13~16或18~21, 数据位的采样计数范围是3~6或8~11。 这是解码器设计主体思想。

图6HI-1573输出电平的特性

Fig.6Characteristics of the HI1573 output level

在设计解码器时, 考虑到HI-1573数据电平抖动和延时现象, 设计采用接收端的正向或反向电平的上升沿终止前一个电平的采样计数, 即数字上实现了对HI-1573输出数据电平的调理。 在此基础上, 基于字核实功能, 设计了校验错误检查、 码元错误检查和字连续检查等逻辑接口功能。 最后采用有限状态机分层次实现时序逻辑的状态转换。

解码器的状态有IDLE, START1, START2, WAIT, SAMPLE1和SAMPLE2以及STOP等7个状态, 其之间的状态转换如图7所示。

各个状态的功能如下:

(1) IDLE: 空闲态, 初始化后处于该空闲态, 总线上没有数据传输时默认处于该态。 当检测到HI-1573正向数据的高电平时, 进入START1; 若检测到HI-1573反向数据位的高电平时, 进入START2。

(2) START1: 启动命令字或状态字同步头检测, 判断反向数据位。 若出现高电平, 采样计数器停止, 并判读计数; 若计数是7或6, 则进入WAIT; 若计数是3或4, 则进入START2; 否则, 进入IDLE, 并置Manchester码错误。

(3) START2: 启动数据字同步头检测, 判断正向数据位。 若出现高电平, 采样计数器停止, 并判读计数; 若计数是7或6, 则进入WAIT; 若计数是3或4, 则进入START1; 否则, 进入IDLE, 并置Manchester码错误。

图7解码器状态机转换图

Fig.7Transition diagram of state machine in decoder

(4) WAIT: 同步头配置态, 将同步头的6或7位数据位串行写入寄存器, 并设置同步头类型。 完成后, 判断正反向数据位电平, 若正向出现高电平, 则进入SAMPLE1; 若反向出现高电平, 则进入SAMPLE2。

(5) SAMPLE1: 采样正向数据高电平脉宽, 判断反向数据位。 若出现高电平, 则采样计数器停止, 并判读位计数以及采样计数; 若位计数到40, 则进入STOP, 并从寄存器中按次序取出17位数据位写入暂存寄存器, 其中前16位是有效数据位, 最后一位是其校验结果; 反之位计数不到40, 此时若采样计数是1或2, 则进入SAMPLE2, 同时将数据位串行写入寄存器, 否则进入IDLE, 并置Manchester码错误。

(6) SAMPLE2: 采样反向数据高电平脉宽, 判断正向数据位。 若出现高电平, 则采样计数器停止, 并判讀位计数以及采样计数; 若位计数到40, 则进入STOP, 并从寄存器中按次序取出17位数据位写入暂存寄存器, 其中前16位是有效数据位, 最后一位是其校验结果; 反之位计数不到40, 此时若采样计数是1或2, 则进入SAMPLE1, 同时将数据位串行写入寄存器, 否则进入IDLE, 并置Manchester码错误。

(7) STOP: 停止态, 初始化各个计数器, 判断16位有效数据位的奇校验与第17位的校验结果是否一致。 若一致, 则设置parity 和Manchester码正确, 并将暂存寄存器的17位数据写入输出端口, 同时进入IDLE; 若不一致, 则设置parity 和Manchester码错误, 并进入IDLE。

3仿真验证及硬件综合

3.1仿真验证

为了验证所设计编解码功能模块的正确性, 在ISE14.7软件开发环境[8], 采用Xilinx仿真工具ISE Simulator进行了时序仿真。 编写测试文件时, 考虑到协议字收发的连续性和便于仿真结果观察, 设计了帧长为3的协议字收发测试文件。 编解码器的仿真结果如图8~9所示。

图8编码器发送3个连续协议字的仿真时序图

Fig.8Simulation sequence diagram of three continuous

protocol words sent from encoder

图8中, 方框表示同步头正确发送。 从图看出编码器实现了协议字的无间隔连续发送。

图9解码器接收4个连续协议字的仿真时序

Fig.9Simulation sequence diagram of four continuous

protocol words accepted in decoder

图9中, 方框表示一个协议字的解析完成, 包括校验正确和码元正确等处理, 椭圆框表示同步头识别, 可以看出解码器收到1个命令字同步头和2个数据字同步头。

3.2硬件综合

为了验证编解码器具有硬件综合能力, 在Spartan6系列XC6SLX9-2TGQ144上进行综合优化, 利用ISE14.7软件自带的综合工具XST进行综合, 综合后编解码器的RTL模块结构如图10~11所示, 可以看出综合后的RTL结构符合设计的接口。

在此基础上, 进行UART闭环硬件测试, 具体方案是上位机发送数据→下位机UART接收并处理→编码器→解码器→下位机处理数据并经UART发送→上位机接收数据, 并通过上位机串口调试助手查看收发结果。 整个硬件测试的结构框图如图12所示, 串口助手收发结果如图13所示。 从图13可以看出数据收发一致, 说明编解码器收发功能正确。

图10编码器RTL结构图

Fig.10RTL structure diagram of encoder