基于Multisim的计数、译码与显示电路

2018-05-21汪明珠毛德梅李泽彬朱雪梅

汪明珠,毛德梅,李泽彬,朱雪梅

(皖西学院 皖创机器人创客实验室,安徽 六安 237012)

Multisim是美国国家仪器NI(National Instruments)有限公司推出的功能强大的虚拟仿真软件,它可以广泛地应用于模拟电路、数字电路、电工电路、射频电路等诸多领域[1]。集成计数器、译码器和数码管显示是电子技术实验中三个基本型实验项目,由于知识点相对零散,实验后知识掌握效果差。本文将三个基本型项目的内容进行整合,形成一个综合型实验项目,通过Multisim仿真软件进行设计、仿真与测试,探究方案的可行性,虚拟仿真成功后,再进行硬件实验,通过软硬结合,提高综合设计能力。

1 仿真主要器件

1.1 计数器

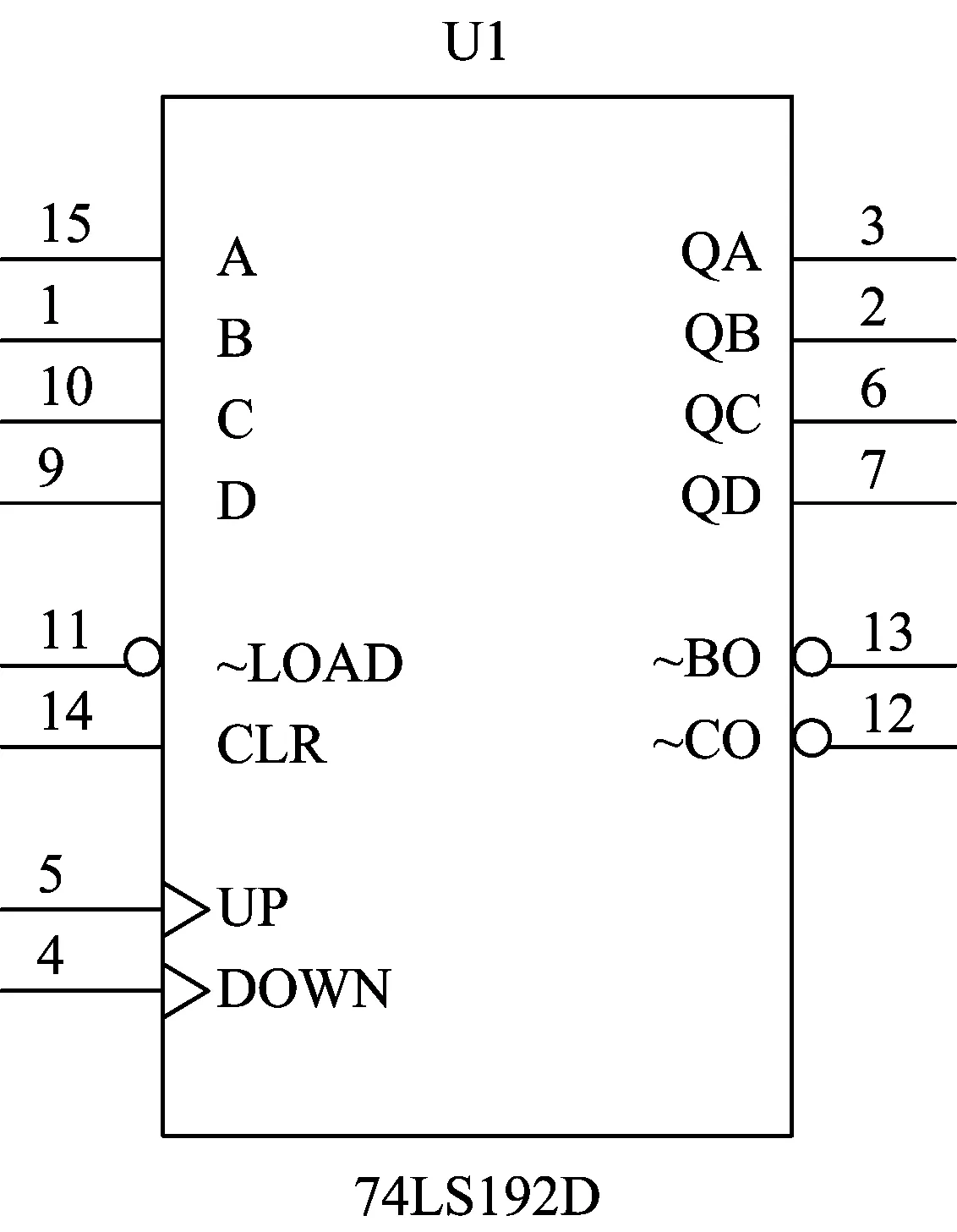

计数器是一个用以实现计数功能的时序逻辑部件,不但可实现计数、分频,还可以实现运算、定时、延时等控制功能。实验中采用74LS192十进制可逆计数器,具有清除、保持、置数和加减计数等功能,74LS192的引脚排列如图1所示。

引脚功能描述:(1)数据输入端为 (A~D), 数据输出端为(QA~QD);(2)异步清除端(CLR);(3)异步预置端(LOAD);(4)加计数/减计数脉冲输入(UP/DOWN);(5)进位输出端借位输出端 (CO/BO)。集成计数器74LS192有16个引脚,其工作状态及功能如表1所示[2-4]。

1.2 译码器

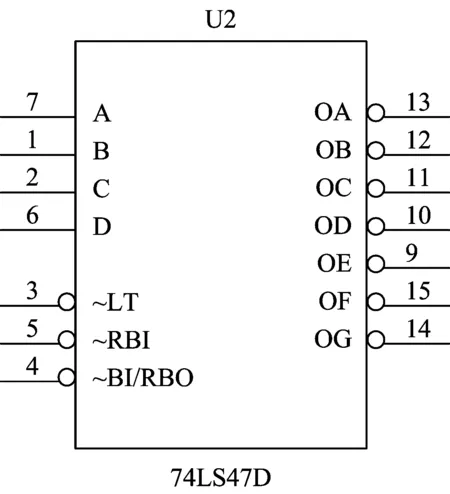

常用的译码器电路有二进制译码器、二—十进制译码器和显示译码器。本实验项目采用BCD七段译码器74LS47,通过它的解码,直接将数字转换成数码管的显示数字,其引脚排列如图2所示。

74LS47是输出低电平有效的七段字形译码器,集电极开路输出,使用时需要接上拉电阻,可用排阻R1代替,实验过程中需配合使用共阳极数码管,74LS47的真值表如表2所示,全面体现了74LS47与数码管之间的关系。

2 仿真测试过程

2.1 译码与显示电路设计与测试

从Multisim仿真软件器件库中选择芯片74LS47D(U1)、共阳级数码管(U2)、拨动开关DSWPK-4(J1)、电源(VCC)及地线(GND),设计如图3所示的译码器74LS47驱动共阳极数码管电路,通过拨动开关DSWPK-4(J1)的左偏或右偏来控制译码器输入端D、C、B、A逻辑电平为“0”或“1”,从而使输入的逻辑电平发生变化,同时观察显示器显示的字符与输入逻辑电平的对应关系。说明:在图3所示电路中,DCBA的接逻辑电平为0011,数码管动态显示十进制数字“3”,测试结果与真值表2相吻合。

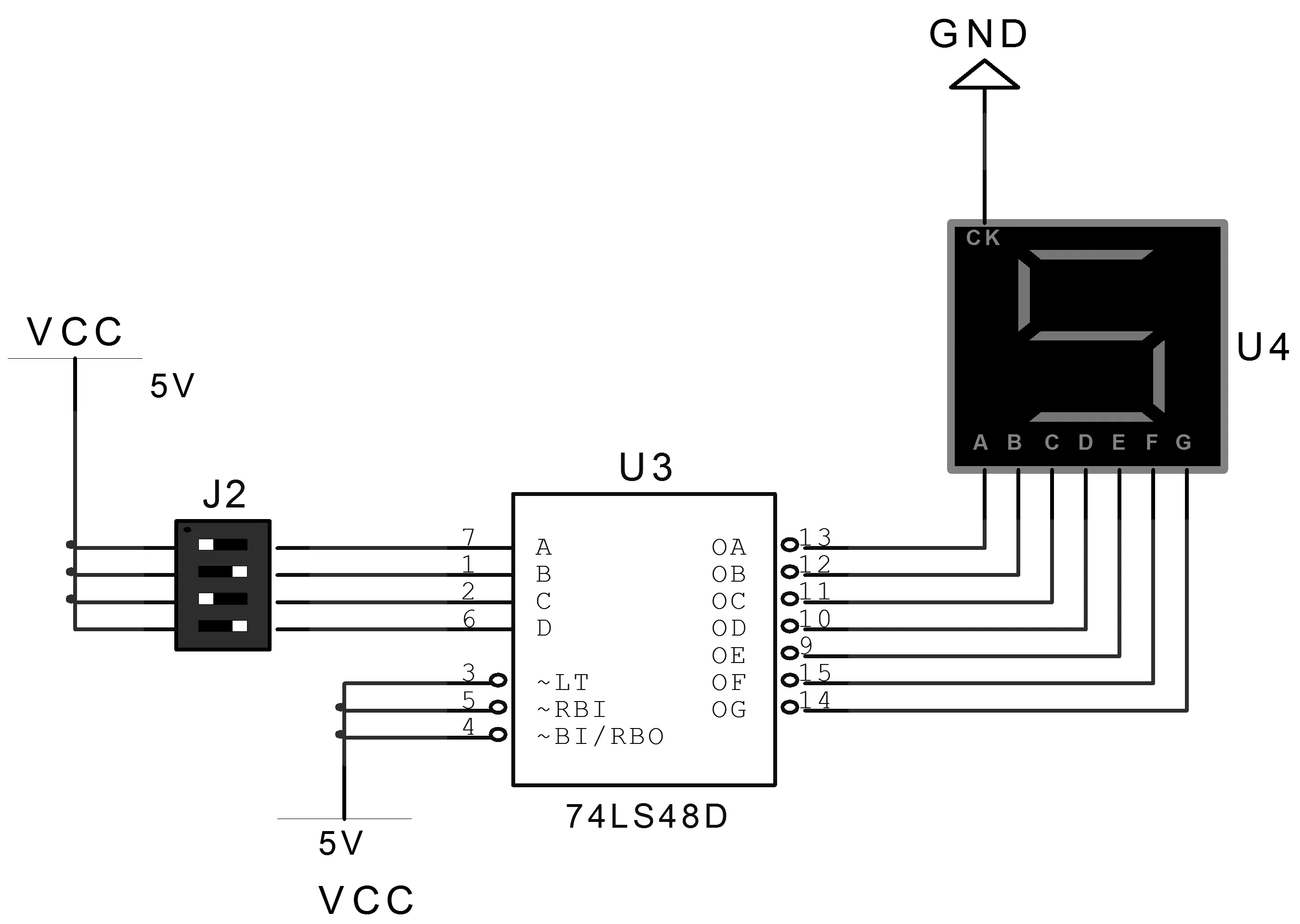

在设计与测试过程中,如果考虑到硬件实验箱上有共阴、共阳两种数码管[5],也可使用74LS48驱动共阴极数码管的图4仿真电路结构,由于译码驱动器芯片74LS48内部有升压电阻,可直接与显示器相连,故可省略排阻。在图4状态下,D、C、B、A的逻辑状态分别为0101,故数码管显示数字“5”。

图1 74LS192引脚排列图

图2 74LS47引脚排列图

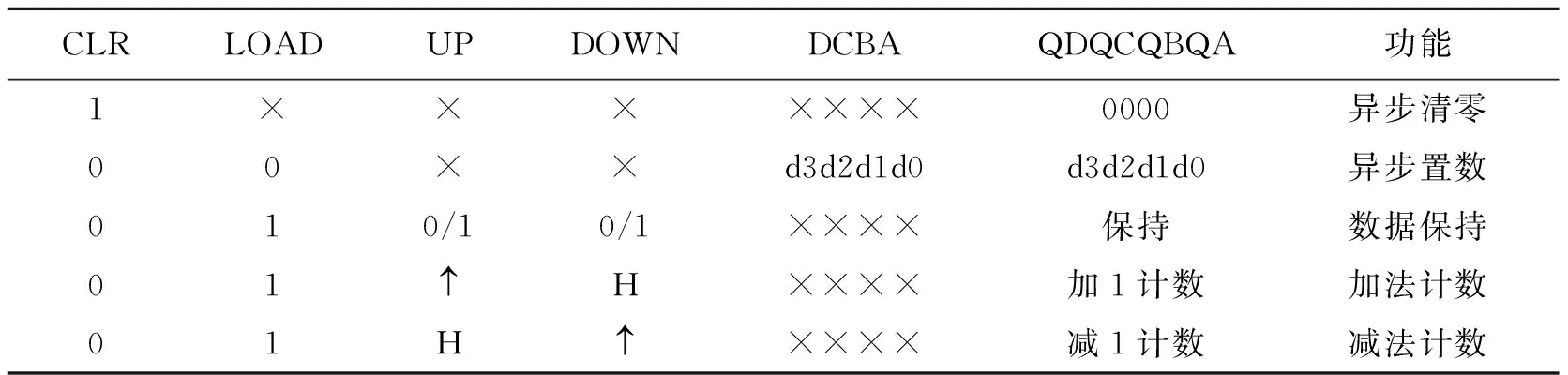

CLRLOADUPDOWNDCBAQDQCQBQA功能1×××××××0000异步清零00××d3d2d1d0d3d2d1d0异步置数010/10/1××××保持数据保持01H××××加1计数加法计数01H××××减1计数减法计数

表2 74LS47功能表

图3 译码器74LS47驱动共阳极数码管

图4 译码器74LS48驱动共阴极数码管

2.2 计数、译码与显示电路综合设计与测试

译码与显示电路顺利通过测试后,即可将计数器部分接入,设计如图5所示的一位十进制计数、译码与显示电路[6-7]。VCC和GND分别模拟高低电平,通过J6、J5、J4、J3四个单刀双掷开关控制计数器D、C、B、A四个并行数据输入端逻辑电平的“0”或“1”,J7和J8控制计数器异步预置端(LOAD)与异步清除端(CLR)逻辑电平的“0”或“1”,J9和J10控制加计数/减计数脉冲输入(UP/DOWN)接计数脉冲或接高电平。

图5 一位十进制计数、译码与显示电路

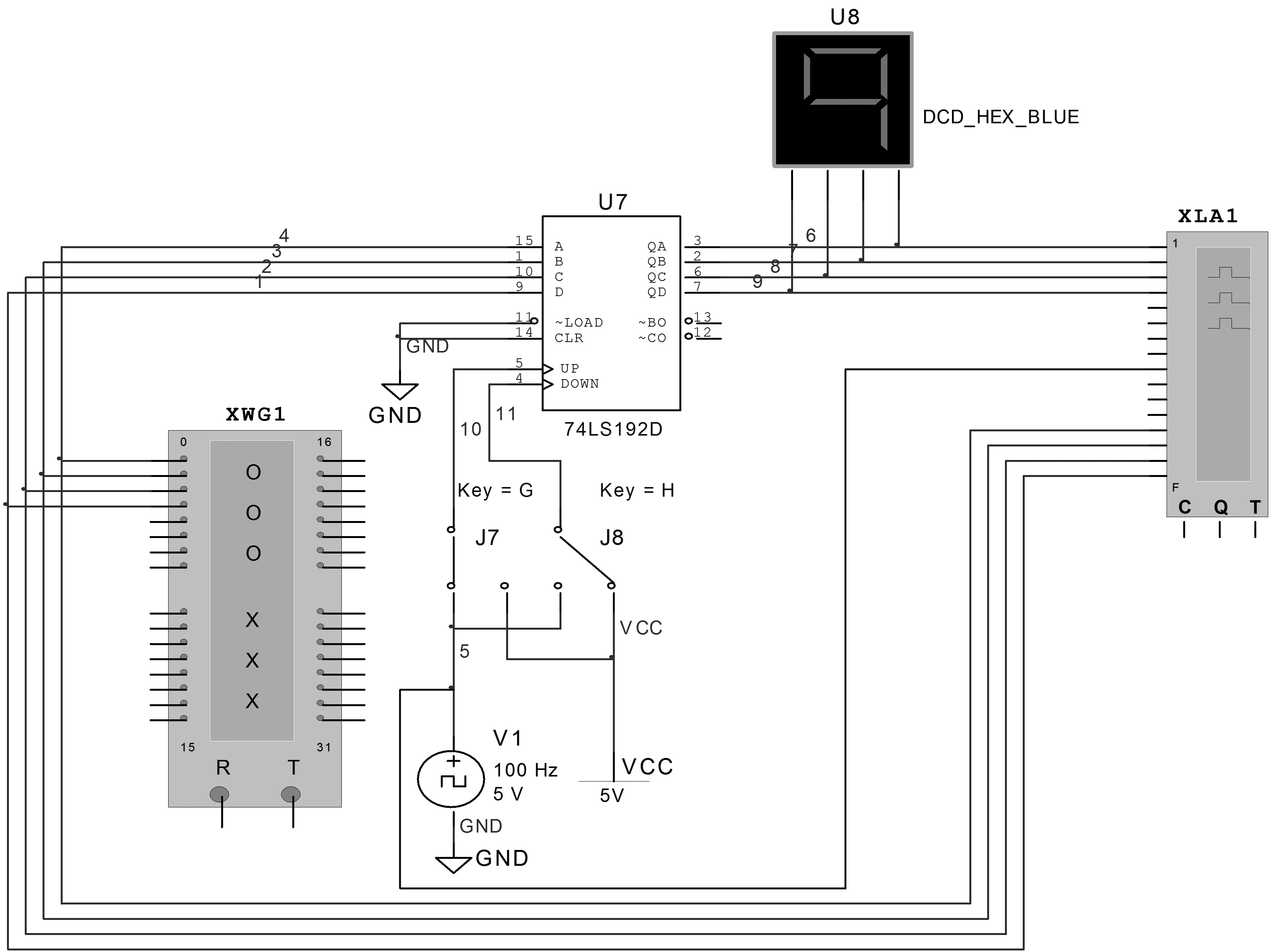

在图5状态下,异步预置端(LOAD)接高电平,异步清除端(CLR)接低电平,且UP接计数脉冲(用方波信号代替),DOWN接高电平,仿真结果显示数码管处于加计数状态,从数字0加计数到数字9,再从9变为0,再递增到9,循环往复,与74LS192功能表1相符。借助Multisim软件提供的逻辑分析仪(XLA1)、字信号发生器(XWG1)和数码管显示器(DCD_HEX)等器件,可设计构建如图6所示的74LS192时序分析电路[8-10],通过时序图8分析时序逻辑电路的工作过程及原理。

图6 74LS192时序分析电路

在时序分析电路图6中,当满足LOAD=CLR=0,即同处于低电平条件下,功能为异步置数,我们从图7字信号发生器设置界面的最下端可以清楚地看出,此时DCBA的逻辑状态为1001,故DCD_HEX显示为数字“9”。对于时序图8,输入与输出状态相同,与功能表1完全吻合。同样,在满足不同的条件之下,通过数码管的动态显示,可测试其清零、加减计数等控制功能。

图7 字信号发生器设置界面

在一位十进制计数、译码与显示电路的成功基础之上,为增加实验难度,提高综合设计能力,我们可将两片74LS192进行级联,设计实现如图9所示的两位十进制计数、译码与显示电路。

图9 二位十进制计数、译码与显示电路

图8 74LS192时序分析结果

在仿真实验后,再利用实验箱、芯片、数码管等器件搭建硬件电路,测试硬件电路功能是否与软件设计相符,通过对硬件电路的功能进行测试,可完全达到设计要求,但虚拟实验不等同于实物实验,在虚拟仿真与实物实验的过程中要注意以下几点:

1)虚拟仿真中所使用的芯片74LS47、74LS48、74LS192是从Multisim的74LS(逻辑库)中调取,VCC和GND引脚是隐藏的,在软件仿真中,集成电路的电源引脚和电源自动接通,但在硬件实验中,芯片的VCC和GND两个引脚必须分别接+5 V和地线GND,否则无法实现其逻辑功能。

2)从实验箱的“逻辑电平输出”选6个端口作为D、C、B、A、Load、CLR等6个变量的控制端,通过逻辑电平开关的偏置,灵活方便地控制各个变量的逻辑“0”和逻辑“1”。

3)在虚拟仿真及硬件实验时,计数脉冲信号可用方波信号来代替,在硬件实验中,采用VPP=5 V,f=1~5 Hz的方波信号效果较佳。

3 结语

笔者通过功能强大的虚拟仿真软件Multisim,设计研究了计数、译码与显示电路,在虚拟仿真中,可灵活地改变电路结构、元器件及参数设置,无限制地调用器件,分析实验原理、观察实验现象与结果,并且将虚拟仿真与实物实验相结合,通过软硬件方面的设计与调试,有助于提高综合小系统的设计能力。

参考文献:

[1]陈志贵.Multisim7在数字电路教学中的应用[J].电子技术,2007(4):45-48.

[2]吴勇灵,朱增辉,杨洁,等.基于74LS192千进制可逆计数器的设计与研究[J].制造业自动化,2012,34(20):111-113.

[3]黄山.N进制计数、译码和显示电路实验教学改革[J].安徽电子信息职业技术学院学报,2013(1):33-35.

[4]乔琳君.基于74LS160的N进制计数器仿真设计[J].电子设计工程,2013,21(24):191-193.

[5]王瑞峰,朱彪.计数译码显示电路常见故障诊断与排除[J].内蒙古科技与经济,2013(1):89-90.

[6]陈玲.基于Multisim仿真软件在《数字电子技术》教学中的应用[J].信息记录材料,2016,17(5):130-133.

[7]任骏原.74LS161异步置零法构成任意进制计数器的Multisim仿真[J].电子设计工程,2011,19(14):135-137.

[8]王静.用74LS290构成任意进制计数器的方法[J].赤峰学院学报(自然版),2012(1):47-48.

[9]马敬敏.集成计数器74LS161的Multisim仿真[J].现代电子技术,2011,34(3):166-167.

[10]丁业兵,方国涛,张文,等.基于Multisim的计数器设计仿真[J].电子设计工程,2013,21(13):147-149.