改性离子注入高阻SOI衬底的共面波导特性研究

2017-10-14常永伟

程 实,常永伟,魏 星,费 璐

改性离子注入高阻SOI衬底的共面波导特性研究

程 实1, 2, 3,常永伟1, 3,魏 星1, 3,费 璐1, 3

(1. 中国科学院上海微系统与信息技术研究所,信息功能材料国家重点实验室,上海 200050;2. 上海科技大学物质学院,上海 200031;3. 中国科学院大学,北京 100049)

因良好的射频性能,高阻SOI (High-Resistivity Silicon-on-Insulator, HR-SOI)被广泛应用于射频集成电路(RFICs)。通过提取共面波导传输线(Co-Plane Waveguide, CPW)的射频损耗来表征衬底材料的射频性能。高阻SOI衬底由于表面寄生电导效应(Parasitic Surface Conductance, PSC),射频性能恶化。设计并制备了一种新型的改性结构来优化高阻SOI的射频性能,通过将硅离子注入到绝缘埋层中来消除表面寄生电导效应。在0~8 GHz范围内,传输线损耗优于时下业界最先进的TR-SOI的结果(Trap-Rich Layer Silicon-on-Insulator)。由于工艺简单,易于集成化,是极具潜力的射频SOI材料。

高阻SOI;共面波导传输线;射频损耗;表面寄生电导效应;硅离子注入;TR-SOI

随着5G通信和物联网(IoT)的快速发展,对芯片集成度的需求也越来越高,人们希望将尽可能多的模块集成在单片集成芯片中。片上系统(Systems-on-Chip, SOC)和系统级封装(Systems-in-Package, SIP)是最有可能做到全面集成不同集成电路功能模块的解决方案。射频前端的集成是业界关注的重点,以往的射频前端模块包含大量三五族化合物半导体集成电路组件,无法与硅基CMOS工艺兼容,开发兼容硅基CMOS工艺的射频前端解决方案成为提升系统集成度的关键[1]。

和体硅相比,SOI(Silicon-on-Insulator)技术在频率响应、速度、集成度和功耗方面都有显著优势,由于埋氧层的存在,结合CMOS工艺的STI(Shallow-Trench Isolation)技术可以做到有源、无源器件的全介质隔离,大大降低由衬底引起的寄生效应和器件间的相互串扰,在混合信号芯片中更能降低由数字开关电路产生的衬底噪声DSN (Digital Substrate Noise),以高性价比实现了低插入损耗,在广泛的频段内实现了低谐波和高线性度,因此SOI非常适合作为系统集成芯片的衬底材料[2]。

在射频和毫米波应用中,常规CMOS工艺中使用的中低电阻率硅衬底(10 Ω·cm)制备的器件会由于高频寄生电流而面临很大的衬底损耗,因此需要采用高电阻率硅衬底(103Ω·cm),以减小衬底的高频寄生电流,降低损耗并提升片上无源器件的品质因素。由于闩锁效应的存在,高电阻率并不适用于体硅CMOS工艺。采用高阻硅衬底作为支撑片(Handle Wafer),中低电阻率硅衬底作为器件片(Device Wafer)制造出来的高阻SOI,兼有高阻硅的低衬底损耗特性,且消除了体硅材料面临的闩锁问题,是系统芯片集成射频前端模块的极佳解决方案[3]。尽管高阻SOI满足了射频前端应用的大部分需求,但其性能受到表面寄生电导效应的影响下滑显著[4-5]。表面寄生电导效应源自于高阻SOI材料本身固有的氧化物-半导体结构(Oxide-Semiconductor, OS),埋氧层中的固定氧化层电荷在高阻硅衬底表面感应产生了一层高电导率反型沟道,导致其表面电阻率下降,衬底寄生效应加剧,射频性能退化。

为了消除表面寄生电导效应,提升高阻SOI的射频性能,本文提出了一种新型的方法来抑制高阻SOI衬底的表面寄生电导效应:通过对埋氧层进行改性离子注入,减弱了固定氧化层电荷对低阻反型层的诱生作用,改善了材料的射频性能。

1 传输线损耗理论

共面波导传输线是一种平面传输线结构,中间的金属线作为信号传输线,两边的金属线作为接地线(图1)。和传统的微带线相比,共面波导的信号线与地线在同一平面,无需接地通孔,特别适合射频集成器件间的连接,在射频芯片中得到广泛应用,因此共面波导传输线是衡量SOI射频性能的极佳选择。

共面波导最重要的参数是插入损耗,其指在传输系统的某处由于元件或器件的插入而发生的负载功率的损耗,它表示为该元件或器件插入前负载上所接收到的功率与插入后同一负载上所接收到的功率以dB为单位的比值。硅基共面波导传输线的插入损耗主要由导体损耗、衬底损耗、衬底界面损耗、介质损耗和辐射损耗五个部分组成[5],其中前三者占主导因素。

(1)导体损耗:导体损耗主要由导体的电阻率决定,同时由于高频的趋肤效应,表面金属的电阻率影响较大,为了降低导体损耗,采用铝和金两步镀膜,使得表面金属为电阻率最小的金属金。

(2)衬底损耗:半导体衬底内的自由载流子是导致衬底损耗的关键因素。硅的损耗角与其电阻率有关,增加硅的电阻率可以有效降低衬底损耗[5]。

(3)界面损耗:界面损耗实质是衬底损耗的一部分,用来表示衬底的表面区域对损耗的影响。寄生表面电导效应等效于在界面处引入了一层低电阻层,高频寄生电流增大,引入了极大的界面损耗,严重恶化了材料的射频性能。

提升高阻SOI材料上共面波导传输线插入损耗性能的主体思路是克服寄生表面电导效应,降低界面损耗,从而降低总的射频损耗。基于此,业界提出了三种主流的方法,包括(a) 质子注入法(Proton Implantation);(b) 图形化介质法(Partial Dielectric Removal)以及(c) 表面加固法(Surface Stabilization)。

其中质子注入法通过向硅表面离子注入的方法注入高能质子,以打断Si—Si共价键,孤立的硅单键构成缺陷能级,束缚自由载流子,降低电导率,增大了硅的电阻率[6]。通过选择性刻蚀介质氧化层,将无金属覆盖区域的介质氧化层去除,表面寄生电导效应得到一定程度的减弱[4,7]。表面加固法消除寄生表面电导通常是在硅衬底表面增加载流子俘获层,传统的方法有使用四甲基氢氧化铵溶液(TMAH)对硅衬底表面处理和Ar离子对硅衬底表面注入。UCL (Université Catholique de Louvain)提出了一种结构,在高阻硅衬底和埋氧层之间引入一层过渡层,以降低寄生表面电导效应。这层过渡层主要作用是俘获自由载流子,通常称为载流子俘获层(Trap-Rich Layer),通常为多晶非晶硅纳米晶硅等钝化层[8-10,15,18]。因较好的热稳定性且兼容CMOS后道工艺[11-13],在硅衬底和埋氧层之间引入一层多晶硅层成为当下研究最为成熟的解决方案。

2 实验与分析

本文基于电荷中和的思想,对埋氧层进行硅离子注入,利用富硅层中和固定氧化层电荷对半导体表面电势的影响,在不改变硅衬底本身特性的前提下减弱并消除寄生表面电导效应,减小传输线的插入损耗。

为了验证改性离子注入对高阻SOI射频性能改良程度,设计了50 Ω特征阻抗的共面波导传输线。设计的传输线结构如图1所示,其中(a)为高阻SOI衬底上共面波导结构示意图;(b)为改性离子注入高阻SOI衬底上共面波导结构示意图;(c)为TR-SOI上共面波导结构示意图;(d)为无损石英基板上共面波导结构示意图。参数见表1。

(a) CPW1 (b) CPW2&3

(c) CPW4 (d) CPW5

图1 共面波导传输线结构示意图

Fig.1 Schematic diagrams of CPW lines

表1 传输线参数

Tab.1 CPW information

SOI晶圆片通过Smart-cut®技术制备,埋氧层厚度为0.4 μm,详细参数见表2。使用TMAH溶液去除顶层硅膜,利用离子注入技术对埋氧层进行改性,Si离子注入能量170 keV,注入剂量为1.0×1016cm–2以及5.0×1016cm–2。在介质层上光刻并电子束蒸发图形化的金属层,金属层由500 nm铝和500 nm金构成,总厚度1 μm。为了使共面波导传输线达到50 Ω的阻抗匹配,通过ADS软件模拟计算传输线传输特性矩阵[14],得到传输线尺寸为=30 μm,=12 μm,g=208 μm,=2176 μm。

表2 SOI参数

Tab.2 SOI information

使用Agilent N5242矢量网络分析仪进行射频小信号测试,传输线被视作线性二端口网络,信号输入功率恒定为–12 dBm,测试其从10 MHz到8 GHz的参数。用损耗系数来表示总的损耗系数,可以表示为

式中:21为传输线的增益,理想传输线的传输增益应为1,实际增益小于1就意味着传输线有传输损耗;|21|2表示传输线的传输损耗。11为反射系数,表示系统前后级的阻抗匹配程度;|11|2表示传输线的回波损耗。回波损耗与传输损耗综合的结果就是传输线总的插入损耗[15]。通过TRL(Thru-Reflect- Line)校准去耦参数中由探针接触金属平板的部分引起的误差(图2)。综合回波损耗和传输损耗,提取射频插入损耗[16]。

(a)=2176 μm 传输线

(b) Thru结构

(c) Open结构

(d) L=5100 μm校准线

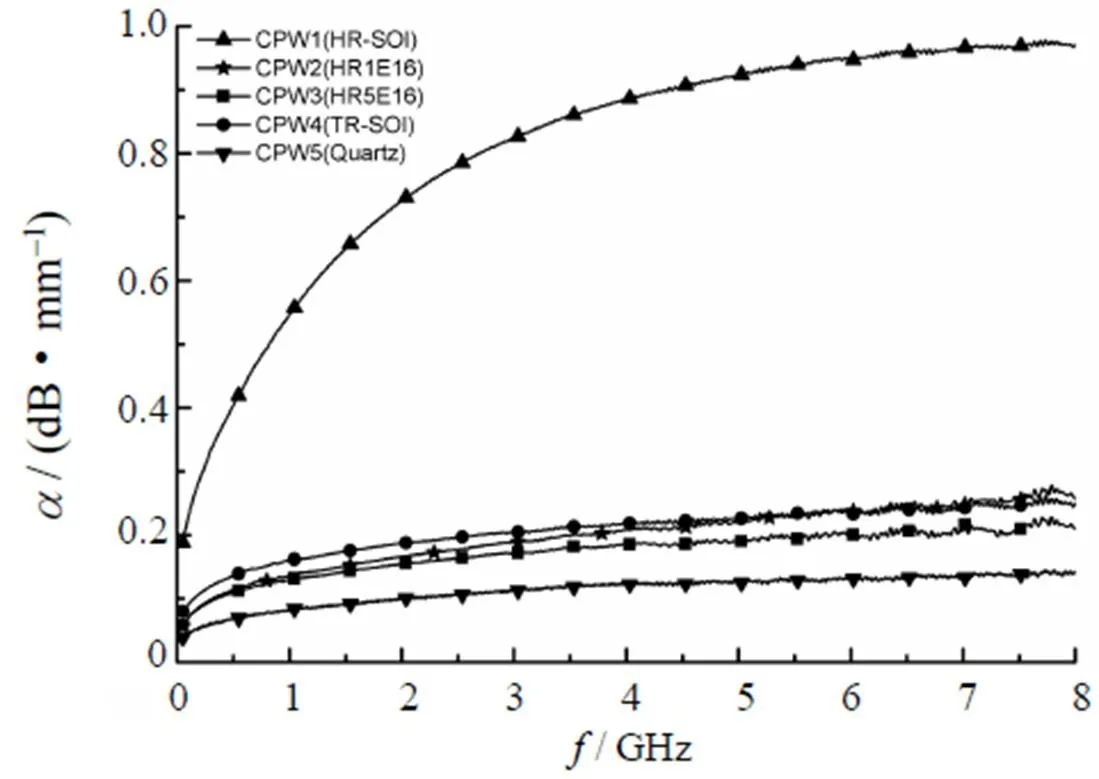

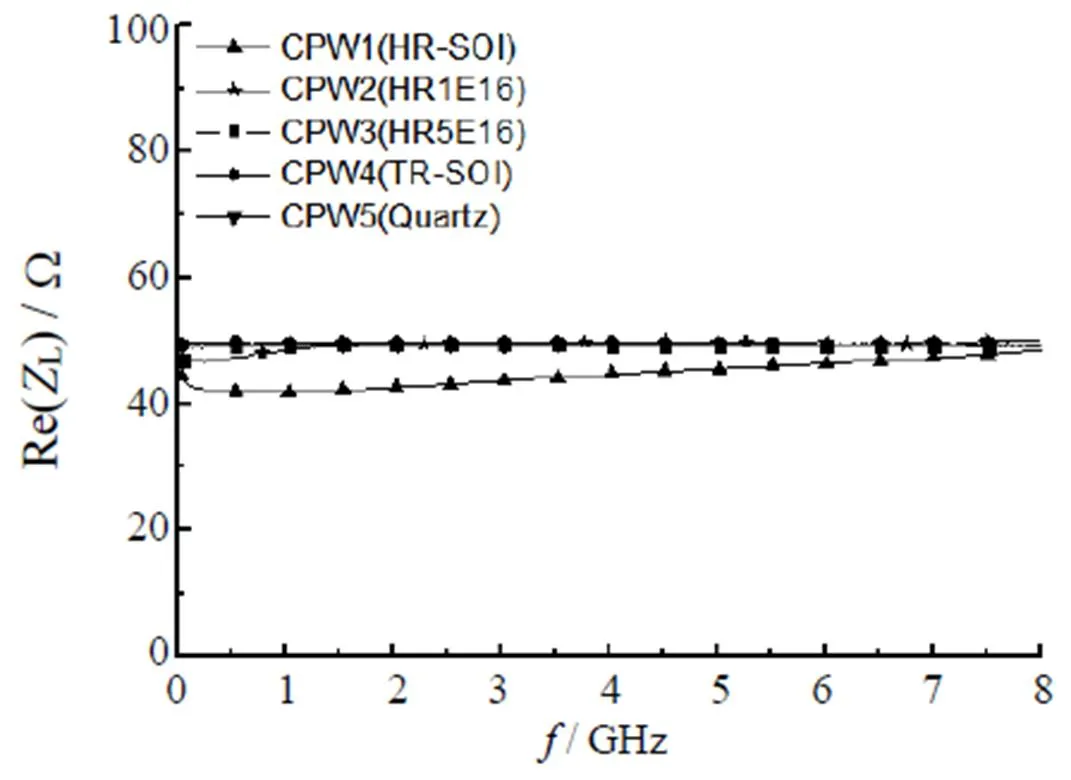

图3给出了不同衬底上传输线的射频损耗提取结果。可以看出,硅离子注入氧化层对高阻SOI上的传输线的射频性能有着显著改善,在0~8 GHz频段内注硅样品的损耗明显小于未注入样品,在频率达到8 GHz时,高阻SOI衬底制备的传输线(CPW1)损耗达到0.97 dB/mm,经过不同剂量硅离子注入的高阻SOI衬底制备的传输线损耗分别达到0.26 dB/mm(CPW2),和0.20 dB/mm(CPW3),TR-SOI损耗为0.23 dB/mm(CPW4),无损石英基板损耗为0.14 dB/mm(CPW5)。从图4中可以看出,在测试频率范围内,注入改性样品的特征阻抗匹配度良好,实部均接近50 Ω。表3给出了本文结果与文献结果的对比。在前一节传输线损耗理论分析中总结出随着衬底电阻率增加,金属电导率上升(金属厚度增加,传输线宽度增加)均能使传输线的插入损耗降低,氧化层的厚度也会影响传输线的插入损耗。因此本文使用标准无损耗石英衬底(仅有金属损耗部分)作为基准,通过对比改性注入样品(CPW2,CPW3)与业界领先的法国Soitec公司生产的引入多晶硅俘获层SOI样品(CPW4 TR-SOI),得出结论:当注入剂量较小时注硅样品传输线损耗接近时下业界最先进的TR-SOI材料,当注入剂量增加到5.0×1016cm–2时,注硅样品的传输线插入损耗比TR-SOI减小15%,接近无损石英基板水平。

(a) 损耗系数曲线

(b) 局部放大

图3 不同衬底CPW的损耗系数结果

Fig.3 Attenuation coefficientsof CPW lines on various substrates

图4 不同衬底CPW的特征阻抗提取结果

表3 文献数据对比

Tab.3 Pubished data of CPW losses

此外,传统氩注入或质子轰击高阻硅对衬底制造损伤的方法[8,18],会面临高温过程导致损伤恢复,射频性能退化;外延非晶硅,纳米硅等方法[15,18]也会面临退火过程中重结晶,俘获效果降低的现象,与CMOS后道工艺的兼容性不强。而对埋氧层注硅的方式不会对硅衬底造成损伤,从图5透射电镜截面照片中可以看出单晶硅无非晶化现象,晶体结构稳定,高温无退火性能。与普通二氧化硅层相比,注硅改性氧化层改善射频损耗性能的主要机理是富硅氧化层中的固定氧化层电荷被中和、屏蔽所致,并不会引起下界面的耗尽、反型,从根源上消除了寄生表面电导效应。与CVD生长的富硅氧化层相比[16],离子注入热氧化层的方式可以得到更好的氧化层质量,从而得到更好的隔离性能。

(a) 截面

(b) 局部放大

图5 TEM截面照片

Fig.5 X-TEM photos

3 结论

本文提出了一种对面向射频应用的高阻SOI材料改良的新方法,通过对埋氧层进行改性离子注入消除了高阻SOI的寄生表面电导效应,射频损耗性能大幅优化,通过传输线插入损耗测试,得到了比业界领先技术TR-SOI更好的性能,8 GHz时比TR-SOI样品损耗减小15%,且性能不随高温过程发生退化,因此该技术兼容CMOS工艺,工艺简单,易于集成化,是极具潜力的射频SOI材料。

[1] TRIGAS C. System-in-Package or System-on-Chip? [EB/OL].(2003-09-19)[2017-02-17]. http://www. eetimes. com/story/OEG20030919S0049.

[2] COLINGE J P. Silicon-on-insulator technology: materials to VLSI [M]. USA: Kluwer Academic Publisher, 1997.

[3] LEDERER D, RODA N C, OLBRECHTS B, et al. Fabrication and characterization of high resistivity SOI wafers for RF applications [C]//ECS Transactions, 214th ECS Meeting. NY, USA: IEEE, 2008: 165-174.

[4] WU Y, GAMBLE H S, ARMSTRONG B M, et al. SiO2interface layer effects on microwave loss of high-resistivity CPW line [J]. IEEE Microwave Guided Wave Lett, 1999, 9(1): 10-12.

[5] OLLHORN S, ZHAO W, MORSCHBACH M, et al. Attenuation mechanisms of aluminum millimeter-wave coplanar waveguides on silicon [J]. IEEE Trans Electron Devices, 2003, 50 (3): 740-746.

[6] WU Y, CHIN A, SHIH K, et al. Fabrication of very high resistivity Si with low loss and cross talk [J]. IEEE Electron Device Lett, 2000, (21)9: 442-444.

[7] GAMBLE H, ARMSTRONG B, WU Y, et al. Low-loss CPW lines on surface stabilized high-resistivity silicon [J]. IEEE Microwave Guided Wave Lett, 1999, 10(9): 395-397.

[8] RODA N C, LEDERER D, RASKIN J P. Optical crosstalk reduction using a HR-Si substrate with trap-rich passivation layer [C]//37th European Microwave Conference. NY, USA: IEEE, 2007: 592–595.

[9] JANSMAN B A, BEEK J V, DELDEN M V, et al. Elimination of accumulation charge effects for high resistive silicon substrates [C]//33rd Conference on European Solid-State Device Research. NY, USA: IEEE, 2003: 3-6.

[10] KAMINS T. Polycrystalline silicon for integrated circuits applications [M]. USA: Kluwer Academic Publishers, 1988.

[11] LEDERER D, RASKIN J. New substrate passivation method dedicated to HR SOI wafer fabrication with increased substrate resistivity [J]. IEEE Electron Device Lett, 26(11): 805-807.

[12] BEN A, RODA N, RASKIN J p. RF SOI CMOS technology on commercial trap-rich high resistivity SOI wafer [C]//IEEE int SOI conference. NY, USA: IEEE, 2012.

[13] LEDERER D, RASKIN J P. Effective resistivity of fully-processed SOI substrates [J]. Solid State Electron, 2005, 49 (3): 491-496.

[14] RODA N C, RASKIN J P. RF harmonic distortion of CPW lines on HR-Si and trap-rich HR-Si substrates [J]. IEEE Trans Electron Devices, 2012, 59(4): 924-932.

[15] CHEN C J, WANG R L, HSUEH T J. A nanocrystalline silicon surface-passivation layer on an HR-Si substrate for RFICs [J]. IEEE Electron Device Lett, 2011, 32(3): 369-371.

[16] Lu H c, Chu t h. The thru-line-symmetry(TLS) calibration method for on wafer scattering matrix measurement of four-port networks [C]// IEEE MTT-S Digest. NY, USA: IEEE, 2004: 1801-1804.

[17] REYNOSO J A, RANGEL-ROJO R, HERRERA M, et al. Influence of the SRO as passivation layer on the microwave attenuation losses on the CPW’s fabricated on HR-Si [J]. IEEE Microwave Wireless Compon Lett, 2003, 13(12): 508-510.

[18] RONG B, BURGHARTZ J N, NANVER J K, et al. Surface-passivated high-resistivity silicon substrates for RFICs [J]. IEEE Electron Device Lett, 2004, 25(4): 176-178.

(编辑:陈渝生)

Investigation on RF loss characteristics of Si implantationmodified HR-SOI

CHENG Shi1,2, 3, CHANG Yongwei1, 3, WEI Xing1, 3, FEI Lu1, 3

(1. State Key Laboratory of Functional Materials for Informatics, Shanghai Institute of Microsystem and Information Technology, Chinese Academy of Sciences, Shanghai 200050, China; 2. School of Physical Science and Technology, Shanghaitech University, Shanghai 200031,China; 3. University of Chinese Academy of Sciences, Beijing 100049, China)

High-resistivity silicon-on-insulator (HR-SOI) is widely adopted for high performance RFICs. RF loss was measured from coplanar waveguide (CPW) transmission lines fabricated on the HR-SOI. The RF performance of HR-SOI is degenerated due to the parasitic surface conductance (PSC). In this work a novel modified structure was designed and fabricated to optimize the RF performance of HR-SOI, Si+ion was implanted into the oxide to reduce the PSC effect. The loss of the CPW is superior to the state of art TR-SOI in 0-8 GHz frequency. It shows the potential application for RF-SOI technology due to the simple process and easily to be integrated.

HR-SOI; CPW; RF loss; PSC; Si implantation; TR-SOI

10.14106/j.cnki.1001-2028.2017.06.014

TN386

A

1001-2028(2017)06-0070-05

2017-05-18

程实

程实(1992-),男,安徽芜湖人,研究生,主要研究方向为SOI技术的射频应用,E-mail: chengshi@shanghaitech.edu.cn;常永伟(1988-),女,山东潍坊人,博士研究生,主要研究方向为高可靠性SOI,E-mail:ywchang@simgui.com.cn;费璐(1961-),男,美籍华人,研究员,博士,主要研究方向为SOI材料,E-mail:lufei@mail.sim.ac.cn;魏星(1981-),男,四川自贡人,副研究员,博士,主要研究方向为SOI材料,E-mail: xwei@mail.sim.ac.cn。

网络出版时间:2017-06-07 13:44

http://kns.cnki.net/kcms/detail/51.1241.TN.20170607.1344.014.html