100Gb/s线路侧光收发模块中ADC的时钟方案

2016-12-02申曜铭黄芝平刘德胜巴俊皓

申曜铭,黄芝平,刘德胜,巴俊皓

(国防科学技术大学 仪器系,长沙410000)

100Gb/s线路侧光收发模块中ADC的时钟方案

申曜铭,黄芝平,刘德胜,巴俊皓

(国防科学技术大学 仪器系,长沙410000)

100G b/s线路侧光收发模块中A D C的时钟设计关键在于保证时钟的低抖动性,是光模块可靠工作的基础。介绍了100G b/s线路侧光收发模块的基本架构和工作流程,提出两种时钟方案,对比分析了两种方案的性能,对线路侧光收发模块中A D C的时钟设计具有一定参考借鉴意义。

100G b/s;线路侧光收发模块;64G S/s A D C;低抖动时钟

0 引言

当今社会的信息化程度越来越高,对信息的交互速度要求也不断提升,骨干网络容量的不断提升为此奠定了夯实的基础。随着100G技术的日益成熟,大规模商用化已经可以实现,目前实现DWDM光纤传输的关键器件之一就是100Gb/s线路侧光收发模块。本文针对100Gb/s线路侧光收发模块中核心部件采样率64GS/s ADC的时钟方案进行了介绍。

1 100Gb/s线路侧光收发模块

1.1 模块简介

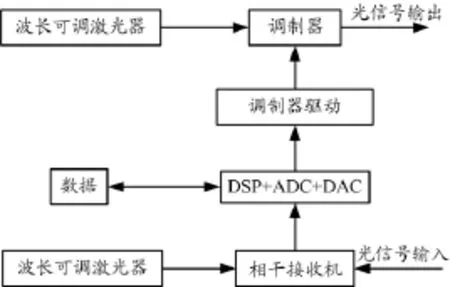

100Gb/s线路侧光模块主要应用于跨海光缆、骨干网等超远距离传输系统中。其主要结构如图1所示。

100Gb/s线路侧光收发模块基于专用DSP搭建起来,一般通过FPGA进行整体控制。发送侧,电信号数据通过DSP编码后由调制器驱动输入到调制器中,在调制器中被调制到激光上从而送入光纤中传输。接收侧,接收机将接收到的光信号重新转化为电信号,然后送入DSP中进行解码及相关补偿后恢复原始电信号数据,通过DSP输出。

图1 100G线路侧光收发模块结构

1.2 高速ADC/DAC侧功能分析

在模块中,DSP不直接与调制器驱动和接收机通信。在发送侧DSP通过4路高速DAC将已加入了超强前项纠错码和训练序列的电信号数据送入调制器驱动,通过马赫曾德尔调制器将数据调制到C/L波段激光上,然后送入光纤进行传输;在接收侧上,4路采样率64GS/s ADC对相干接收机发出的模拟信号数据进行采样,数字信号数据在DSP中进行超强前项纠错码解码、去训练序列以及相关算法估计和补偿,从而恢复原始数据。上述过程中,ADC的采样速率最高达64GS/s,这对时钟提出了苛刻的要求。要让如此高采样率ADC正常工作,关键就是时钟设计。

2 抖动影响与时钟方案

2.1 抖动影响

高速系统中,抖动是时钟质量的关键参数,原则上时钟抖动越小越好。首先,在逻辑处理上,若时钟抖动超过数字信号处理器的阈值,可能会使时序逻辑的建立时间和保持时间混乱,从而使系统功能紊乱[1];其次,抖动和噪声本质上是一样的,如果时间上表现抖动过大,频率上则表现为噪声增大,这将直接导致系统的信噪比降低。

2.2 工作条件

在100Gb/s线路侧光收发模块中,ADC对时钟的要求比DAC高。以日本NEL公司最新款100G光收发模块专用DSP为例,其ADC要求时钟抖动在50fs以内,而DAC在250fs以内即可,本文只探讨ADC的时钟方案。ADC时钟方案分两种:压控晶振+声表面滤波器方案、时钟芯片+去抖动芯片方案。

2.3 压控晶振+声表面滤波器方案

晶振的相位噪声产生原因比较复杂,有工艺、环境等因素。晶振在加工出来后,本身就具有一定的相位噪声,而相位噪声是抖动的直接来源[2]。实际应用中,直接由晶振输出抖动50fs以内的时钟比较困难。降低晶振输出抖动,一个可行的思路就是加入滤波器,将抖动控制在50fs以内。目前广泛使用的晶振滤波补偿器是声波表面滤波器(SAW滤波器),可以通过SAW滤波器对晶振输出信号进行滤波补偿,从而获得所需时钟信号。

根据参数要求,方案可选器件较多,这里以日本SEIKO公司的一款电压控制的SAW晶体振荡器(VCSO)EV-9100JG为例,方案原理框图如图2所示。

DSP输出的参考串码通过FPGA转换成控制串码,进而控制DAC输出控制电压,再通过放大器后对EV-9100JG进行电压控制。

图2 晶振方案框图

2.4 时钟芯片+去抖动芯片方案

如上文所述,单独使用晶振很难提供抖动50fs以内的时钟信号,单纯通过一块时钟芯片也很难提供50fs以内的时钟信号。如果使用抖动过滤芯片+时钟芯片组合,则可在输出特定频率时钟下将抖动降低到50fs以内。

根据参数要求,方案可选芯片较多,这里以美国ADI公司的AD9525+AD9559为例,前者是时钟芯片,后者是同步去抖动芯片,方案框图如图3所示。

图3 时钟芯片方案框图

DSP输出的信号通过FPGA转换成控制信号,控制DDS芯片输出参考时钟到去抖动芯片AD9559,去抖动后的输出时钟作为参考时钟输入到时钟芯片AD9525,通过内部PLL倍频后输出所需时钟。

AD9559输出时钟的频率和相位由参考时钟决定,抖动则由本地低抖动VCO和芯片内部的数字环路滤波器决定。DSP为AD9559提供参考时钟,AD9559内部有可编程DPLL,DPLL中有一个可编程数字环路滤波器,可以极大地降低时钟信号的抖动。DPLL输出信号作为参考时钟送入APLL中作倍频处理,最终将低抖动参考时钟信号提供给AD9525。

VCO为AD9525提供内部振荡,AD9559输出的低抖动信号作为参考时钟,决定AD9525输出时钟的相位和频率,通过AD9525内部的可编程PLL最终产生抖动在50fs内所需的时钟信号。

2.5 方案对比

压控晶振(VCXO)+SAW滤波器,能够可靠地提供50fs内的低抖动时钟信号,外围电路和配置程序设计简单,开发周期较短,价格合理。但是此方案应用场合比较固定,难以根据具体实际情况做出及时应对调整,灵活性不高。

完全可编程的时钟芯片+去抖芯片方案,此套方案的外围电路、配置程序设计难度增加,开发周期变长。但是通过FPGA配置程序具有灵活性,可以根据各种不同应用场合对配置程序做出及时修改,尽可能确保了解决方案在最优状态下运行,增加了方案适用范围,且价格合理。在不同的应用场合里,两套方案各有优势,总体上无法明确哪套方案一定比另一个更好,只能根据实际需要合理选择。

3 测试方法

由于实验设备限制,时域内通过示波器虽然可以观测到输出时钟信号,却无法测量出50fs内的抖动。目前世界上最新示波器也只能测量高于90fs的抖动,且价格极其昂贵。故可采用其它方法进行测试。

①因为时钟信号是提供给高速ADC的,如果时钟输出抖动超过50fs,高速ADC将无法正常工作,即与之进行数据交互的DSP将无法正常收发数据。因此,我们可采取间接的验证方法确定时钟是否满足要求,即分析整个模块是否正常工作。例如测试整个模块的OSNR是否正常来确认100Gb/s线路侧光收发模块是否正常工作[3]。

②通过精密频谱仪分析获得时钟信号频谱,在指定范围内进行相应积分运算,进而获得时钟信号的抖动[4]。

4 结束语

本文简单介绍了100Gb/s线路侧光收发模块,针对模块内部高速ADC时钟设计,提出两套方案。由于实验条件欠缺,在数据印证方面尚有不足,将在更有效的方案设计出现后加以解决。本文为100Gb/s线路侧光模块高速ADC时钟设计提供一定的参考,对其它相似时钟设计具有一定借鉴意义。

[1]吕郁.自适应带宽时钟发生器的抖动一致性研究[D].长沙:国防科技大学研究生院,2009:65-67.

[2]GREBENKEMPER J C.本振相位噪声及其对接收机性能的影响[J].和新阳,译.空间电子技术,2003(1):4-13.

[3]杨俊麒.100Gb/s线路侧光收发模块OSNR测试研究[J].光通信研究,2014(4):51-53.

[4]张志鑫.基于信号源与频谱仪的相位噪声测试软件设计[J].研究与开发,2012,31(3):65-67.

Proposal of high speed ADC sampling clock in 100 Gb/s line side transponder

SHEN Yao-ming,HUANG Zhi-ping,LIU De-sheng,BA Jun-hao

(Department of instrumentation,National University of Defense Technology,Changsha 410000,China)

The key of ADC clock design in the 100Gb/s line side transponder is low jitter that keeps the transponder work reliable.The paper describes the structure and workflow about 100Gb/s line side transponder,and introduces two proposals with comparison.It has certain value of reference for high speed sampling clock design in line side transponder.

100Gb/s,line side transponder,64GS/s ADC,low jitter clock

TN915.62

A

1002-5561(2016)03-0040-03

10.13921/j.cnki.issn1002-5561.2016.03.012

2015-12-07。

申曜铭(1990-),男,硕士研究生,主要从事100Gb/s线路侧光收发模块的研究。