基于FPGA的可变速率PSK数字解调器实现

2016-09-21毛小群

毛小群

(重庆电子工程职业学院,重庆 401331)

基于FPGA的可变速率PSK数字解调器实现

毛小群

(重庆电子工程职业学院,重庆401331)

针对QPSK变速率调制数字系统,提出了一种新的基于现场可编程门阵列(FPGA)实现方法,该系统可以支持4.88 Kb/s到2Mb/s和更高的连续比特速率。设计采用混合乘法器、数控振荡器(NCO)和积分-梳状滤波器(CIC),并给出了系统中载波和信号恢复电路的设计结构,且可以移植到任何FPGA器件。提出的设计在Xilinx Virtex-5 FPGA平台进行了硬件测试。硬件实现结果显示,采用本方法实现的解调器,表现出优越的使用效率。

变速率,调制器,比特速率,现场可编程门阵列

0 引言

随着全球范围内个人通信需求的不断增长,卫星通信的使用规模也不断增大。相移键控(PSK)因为其较好的抗噪能力(即使在低Eb/N0的情况下,相比其他方法它有更低的误码率)和再生能力,可以维持较高的服务通信质量(QoS),成为在卫星通讯中最常用的数字调制技术。

先进的卫星间通信必须支持不同速率,以满足用户对更大带宽的声音、视频和数据通信的需求。解调器在任何航空和地面通信接收器中都是一个关键的部分,用来从调制信号中获得需求的基带数据。为了实现速率达到2Mb/s或者更高的数字解调器,可以使用FPGA来实现可变速率的解调器。

文献[1]提出了一种QPSK数字解调器,通过调整解调器电路结构,来完成QAM调制方式的解调工作;文献[2]则提出了无需改变电路结构的数字解调器,就能够完成QPSK及8PSK解调工作;文献[3]提出了一种采用并行结构的高速数字解调器,这3种解调器都是基于对固定速率,且速率低于2Mb/s的情况。

本文设计了一种基于FPGA实现的可变速率的QPSK解调器。并在Xilinx Virtex5 FPGA系列的VC707评估板上进行了设计验证。设计采用混合乘法器、数控振荡器(NCO)和积分-梳状滤波器(CIC),并给出了系统中载波和信号恢复电路的设计结构。该系统可以支持4.88 Kb/s到2Mb/s和更高的连续比特速率。

1 PSK通信系统原理

图1显示了一个典型的卫星通信PSK系统的基本原理图。它包含基带数据的信源编码,载波相位调制和AWGN信道(天线与通信媒体终端之间,RF信号传输的模型)[4]。

图1 典型PSK通信系统的基本结构框图

在接收端,通过相反的过程获得需求的基带数据。数据的解调可以通过再生实现,也可以通过模拟或者数字接收器实现。解调器的数字实现应该是首选[5],因为相比模拟解调,数字解调器具有可编程性和更快的定时恢复。

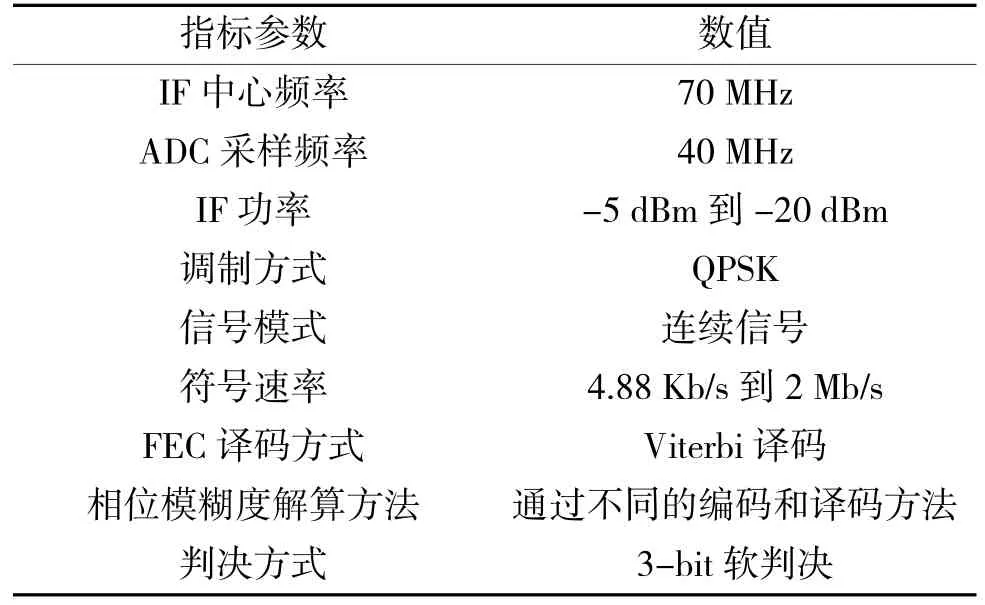

表1显示了QPSK解调的技术参数。根据处理的反转图像调制信号的频谱中心值,采样频率设定为70MHz。

表1 解调器技术参数

2 提出的解调器设计

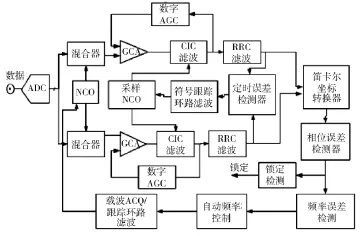

图2显示了提出的数字QPSK解调器的设计框图。它包括3个跟踪回路:自动给增益回路(AGC),载波捕获/跟踪回路和符号跟踪回路。

图2 提出的数字PSK解调器结构

AGC回路跟踪和调节由路径损耗引起的输入信号功率变化。载波跟踪回路可以消除载波频率和相位的不确定性(由于振荡器的不稳定性,符号跟踪回路的相位消除,数据中频率的不确定性和接收数据的时钟同步等问题引起)[6]。一个有限状态机被用于选择捕获或者跟踪的模式,和选择假锁和实锁状态的输出。

2.1数控振荡器和混合器设计

设计数控振荡器(NCO)是为了产生正弦和余弦载波[7],用于与数字调制的输入数据进行结合。正弦信号被用于相位组件,而余弦信号用于产生复杂信号的正交分量[8]。图3显示了NCO的设计结构。表2给出了NCO的技术指标参数。

图3 FPGA中NCO设计结构图

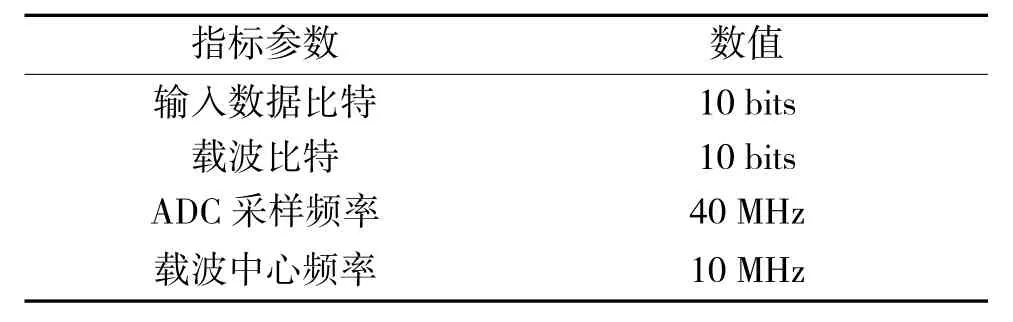

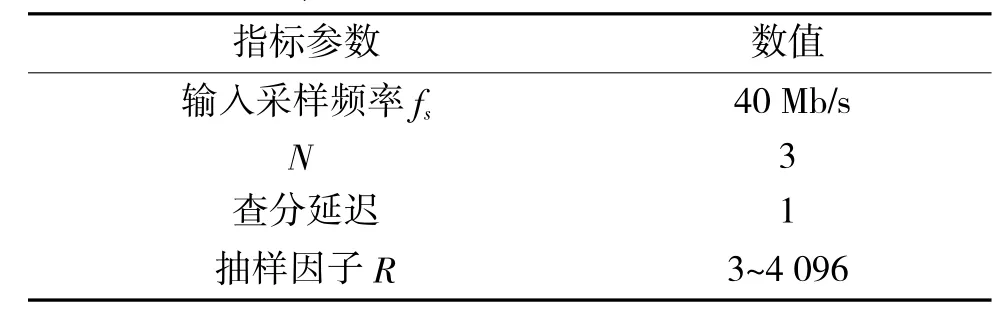

表2 NCO技术参数

在相关信道的载波频率附近,混合器将数字化的输入数据样本与合成载波相乘,以便将需要的信道带入基带范围。混合器的输出同时包含频率组件在输入采样频率的和值与差值。为了硬件验证本文设计,结构中混合器必须在ADC的采样频率下进行工作。如表3给出了混合器的技术指标参数。

表3 混合器技术参数

2.2环路滤波器设计

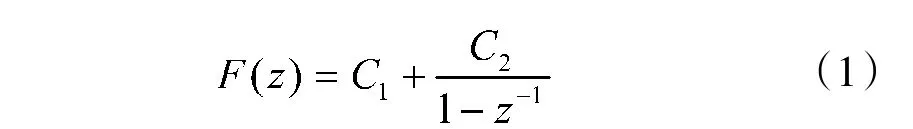

提出的解调器结构中的环路滤波器是一个二阶滞后滤波器,如图4所示。滤波传输函数为:

图4 数字环路滤波器

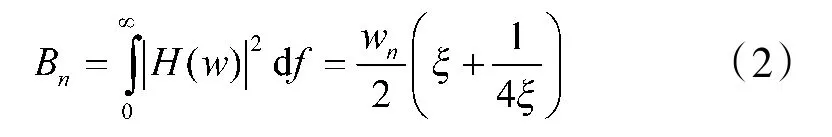

二阶锁相环的环路带宽Bn为:

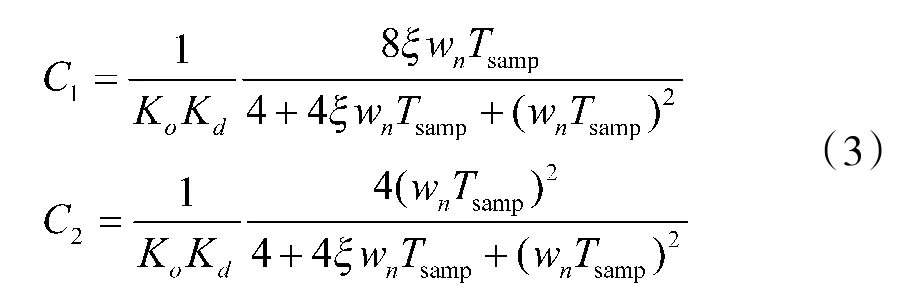

根据载波和符号跟踪环的环路带宽,可以计算出环路滤波器系数,如下式所示:

其中,wn是环路的固有频率,Tsamp是采样间隔,ξ是阻尼系数,K0和Kd为NCO增益和混合器增益。

2.3CIC滤波器设计

在提出的数字解调器结构中,为了进一步处理信号需要两个必须的功能:低通滤波和抽样。在混合器之后必须立刻进行低通滤波,以便消除由混合功能引起的多余信号频率。抽样是为了减少输入采样速率,以便为后续阶段在最大程度上,减少所需释放信号的过程[9]。

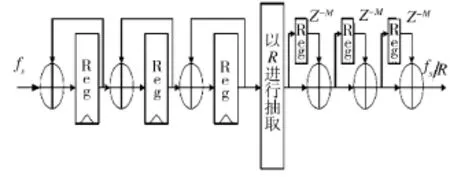

CIC滤波器是一个十分有效的执行抽样的方法[10],图5显示了CIC滤波器的结构。包括N个级联积分器(锁定采样频率为fs),速率变化因子R,N个级联的梳阶段(工作频率为fs/R),其中N具体的数量或者滤波器阶数。CIC滤波器是高效的硬件滤波器结构,因为它只使用移位寄存器和加法器来执行滤波功能[5]。

图5 CIC抽样滤波器结构图

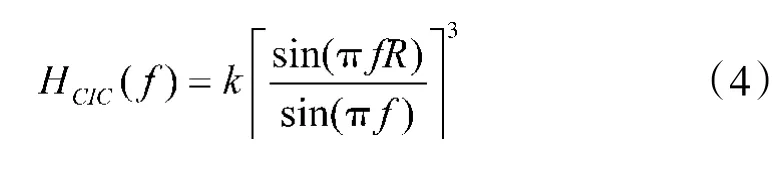

滤波器拥有一个频率响应函数,如下所示。

其中,f是相对于输入采样速率的归一化频率,k滤波增益且R是抽样速率。

通过抽样因子R可以控制滤波器通带带宽[11],而R是可以调节的,从而可以提供灵活的解调带宽来匹配符号边界。滤波器技术参数如表4所示。

表4 CIC滤波器技术参数

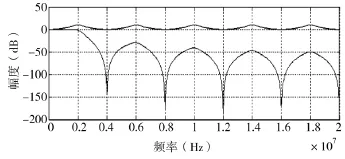

在CIC滤波器之后使用了可编程的有限脉冲响应滤波器(PFIR),以便弥补频带倾斜。精度密度系数可以制定在1 bits到32 bits范围内。图6显示了符号速率为2Mb/s时,补偿CIC的滤波响应。

图6 补偿CIC滤波响应

为了增加信噪比(SNR)以便更好地实现信号估计,在解调器中使用根余弦滤波器作为匹配滤波器。升余弦滤波器的幅值响应为:

其中,Ts表示单位符号间隔,α表示滚降系数并且在系统实现中设置为0.35。

3 实验结果与分析

整个设计的实现是使用VerilogHDL 2001,且没有使用FPGA IP核,因此,提出的设计是独立平台,可以应用于任何FPGA模块比如Xilinx或者Actel。尽管如此,本文FPGA实现实验使用了XilinxISE9.2i,功能函数仿真使用了与Xilinx Virtex-5 FPGA匹配的Questa Sim 10.0b。图7显示了实现提出设计的硬件测试系统。包括COMTECH调制解调器用于调制输入,Tektronix TLA5201B逻辑分析仪用于捕获和观察解调器的输出结果。

图7 硬件测试系统

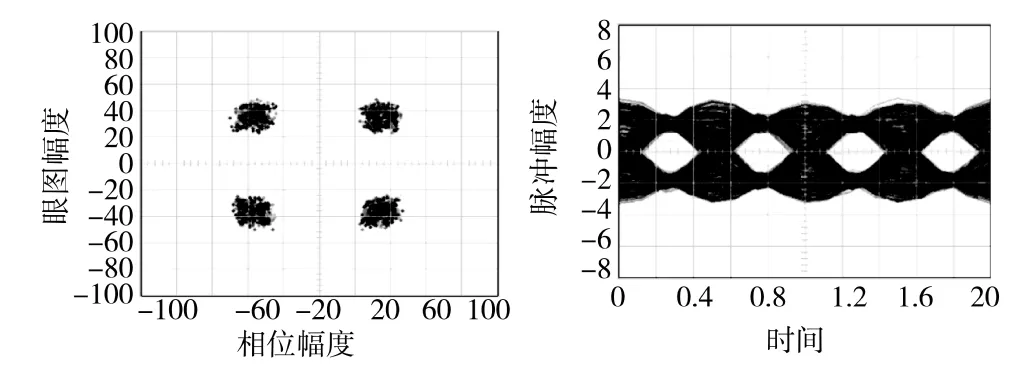

使用Simulink模型对不同的设计参数进行了仿真,从而更容易的完成硬件实现。下页图8给出了符号速率为2Mb/s时,解调器端口4相位星座图和眼图。

图8 QPSK星座和眼图

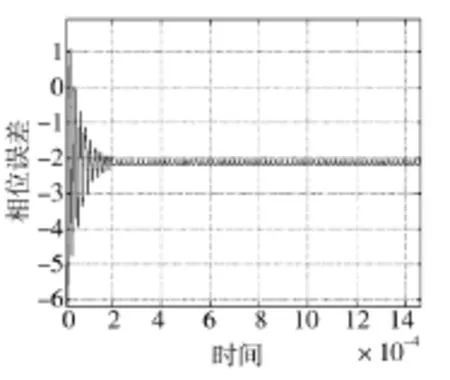

图9(a)显示了在闭环条件下输入与本地载波之间,载波跟踪环路的相位误差响应。图9(b)显示了符号速率为2Mb/s时BER的理论值与仿真值。PSK编码系统达到了0.5dB的实现裕量,编码增益大概为5dB。

图9 (a)锁定载波跟踪环路的载波相位误差

图9(b)载波跟踪环路的BER曲线

图10显示了由ADC通过40Mb/s采样后,70MHz载波16 384点的FFT图。无杂散动态范围(SFDR)>50 dB,由此可以看出相对于ADC动态范围,解调器的性能是独立分布的。

图10 ADC特性的FFT图

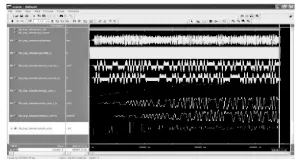

已调信号需要通过Xilinx开发板集成的ACD模拟设备AD9054A,且通过逻辑分析仪捕获其输出。该数据存储在FPGA的ROM中,作为整个设计的仿真输入。Questa Sim 10.0b的结果如图11所示。仿真结果包括相位误差处于锁定状态时的调制信号输入,NCO的合成载波,混合器输出,数字ADC输出,CIC滤波器输出。

4 结论

本文提出一种硬件有效的QPSK数字解调器结构,该设计使用可编程数据速率,可适用于先进的卫星通信系统。提出的设计是独立平台,可以移植在任何目标FPGA。提出的设计在Xilinx Virtex-5 FPGA平台进行了硬件测试。硬件实现结果显示,采用本文方法实现的解调器,表现出优越的使用效率。

图11 数字解调器的功能仿真结果

[1]向东游,张华栋,李忠亮.一种适用于QPSK遥测接收机的符号定时估计器的FPGA实现研究[J].计算机测量与控制,2013,21(9):2538-2540.

[2]朱云鹏.一种QPSK载波恢复环防错锁优化方法[J].无线电通信技术,2012,38(1):63-65.

[3]ROBBERTV D.QPSK and BPSK demodulator chipset for satelli-teapplications[J].IEEE Transactionson Consumer Electronics,1995,41(1):30-41.

[4]SHIVARAMAIAH N C,DEMPSTER A G,RIZOS C. Time-multiplexed offset-carrierQPSK forGNSS[J].IEEE Transactions on Aerospace and Elect-ronic Systems,2013,49(2):1119-1138.

[5]RODRIGUEZ-GOMEZ R,FERNANDEZ-SANCHEZ E J,DIAZ J,et al.FPGA implementation for real-time background subtraction based on horprasertmodel[J].Sensors,2012,12(1):585-611.

[6]LINN Y.A self-normalizing symbol synchronization lock detector for QPSK and BPSK[J].IEEE Transa-ctions on WirelessCommunications,2006,5(2):347-353.

[7]张毅,欧阳志新,邓云凯,等.高性能无数据辅助QPSK频偏估计新算法[J].西安电子科技大学学报:自然科学版,2013,40(2):187-193.

[8]茅帅帅,诸波,王永强,等.基于DSP实现的100 Gbit/s DP-QPSK系统相干接收技术[J].激光与红外,2013,43 (12):1393-1396.

[9]吕曦光,王磊,徐东明,等.相干光通信中基于QPSK调制的光锁相环分析[J].长春理工大学学报:自然科学版,2013,36(3):49-52.

[10]房利,张荣芬,李良荣,等.QPSK调制/解调电路的verilog HDL模型与功能仿真[J].贵州大学学报:自然科学版,2013,30(6):81-84.

[11]周泽湘,徐运武.基于VHDL的QPSK调制解调系统设计与仿真[J].电子设计工程,2013,21(9):89-90,94.

FPGA Implementation of Variable Rate PSK Digital Demodulator

MAO Xiao-qun

(Chongqing College of Electronic Engineering,Chongqing 401331,China)

In order to achieve QPSK variable rate modulation digital system,a novel based on field programmable gate array(FPGA)implementation method is proposed.The system can support 4.88Kb/s to 2Mb/s and higher continuous bit rate.Design with the mixed multiplier,numerically controlled oscillator(NCO)and integral comb filter(CIC),and the structure of carrier recovery circuit and signal of the system is described.This system can be ported to any FPGA device.The proposed design of the hardware tests in the Xilinx Virtex-5 FPGA platform.The test results show that the proposed demodulator show superior ability in efficiency.

variable rate,modulator,bit rate,field programmable gate array(FPGA)

TN761

A

1002-0640(2016)08-0181-04

2015-06-05

2015-07-23

毛小群(1981-),女,湖南邵阳人,研究生,讲师。研究方向:电子技术、自动化控制,信号处理。